目录

1. 像素数据输出时序

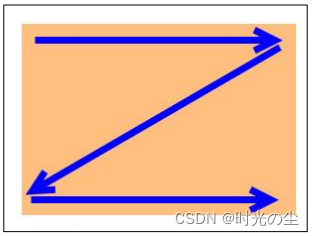

主控器控制 OV7725 时采用 SCCB 协议读写其寄存器,而它输出图像时则使用 VGA 或QVGA 时序,其中 VGA 在输出图像分辨率为 480*640 时采用,QVGA 是 Quarter VGA,其输出分辨率为 240*320,这些时序跟控制液晶屏输出图像数据时十分类似。OV7725 传感器输出图像时,一帧帧地输出,在帧内的数据一般从左到右,从上到下,一个像素一个像素地输出(也可通过寄存器修改方向)。

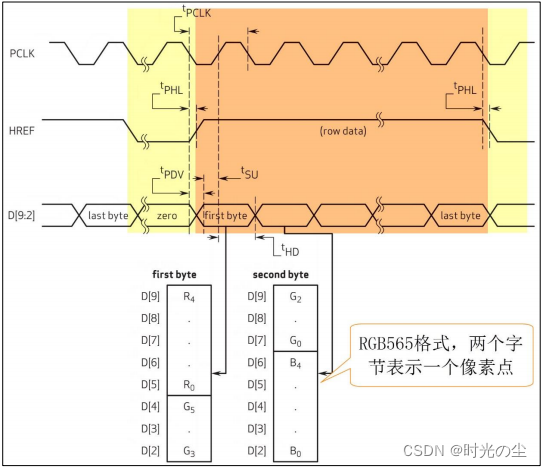

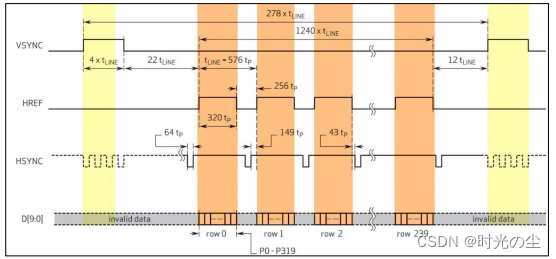

若我们使用 D2-D9 数据线,图像格式设置为 RGB565,进行数据输出时,D2-D9 数据线在 PCLK 在上升沿阶段维持稳定,并且会在 1 个像素同步时钟 PCLK 的驱动下发送 1 字节的数据信号,所以 2 个 PCLK 时钟可发送 1 个 RGB565 格式的像素数据。当 HREF 为高电平时,像素数据依次传输,每传输完一行数据时,行同步信号HREF 会输出一个电平跳变信号间隔开当前行和下一行的数据;一帧的图像由 N 行数据组成,当 VSYNC 为低电平时,各行的像素数据依次传输,每传输完一帧图像时,VSYNC 会输出一个电平跳变信号。

2. FIFO 读写时序

STM32F4 系列的控制器主频高、一般会扩展外部 SRAM、SDRAM 等存储器,且具有DCMI 外设,可以直接根据 VGA 时序接收并存储摄像头输出的图像数据;而 STM32F1 系列的控制器一般主频较低、为节省成本可能不扩展 SRAM 存储器,而且不具 DCMI 外设,难以直接接收和存储 OV7725 图像传感器输出的数据。OV7725 摄像头在图像传感器之外还添加了一个型号为 AL422B 的 FIFO,用于缓冲数据。AL422B 的本质是一种 RAM 存储器,它的容量大小为 393216 字节,支持同时写入和读出数据。

|

管脚名称

|

管脚类型

|

管脚描述

|

|

DI[0:7]

|

输入

|

数据输入引脚

|

|

WCK

|

输入

|

数据输入同步时钟

|

|

/WE

|

输入

|

写使能信号,低电平有效

|

|

/WRST

|

输入

|

写指针复位信号,低电平有效

|

|

DO[0:7]

|

输出

|

数据输出引脚

|

|

RCK

|

输入

|

数据输出同步时钟

|

|

/RE

|

输入

|

读使能信号,低电平有效

|

|

/RRST

|

输入

|

读指针复位信号,低电平有效

|

|

/OE

|

输入

|

数据输出使能,低电平有效

|

|

TST

|

输入

|

测试引脚,实际使用时设置为低电平

|

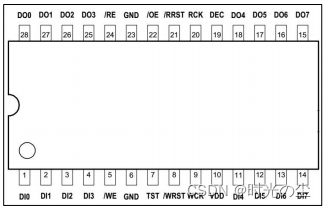

由于 AL422B 支持同时写入和读出数据,所以它的输入和输出的控制信号线都是互相独立的。写入和读出数据的时序类似,跟 VGA 的像素输出时序一致,读写时序介绍如下:

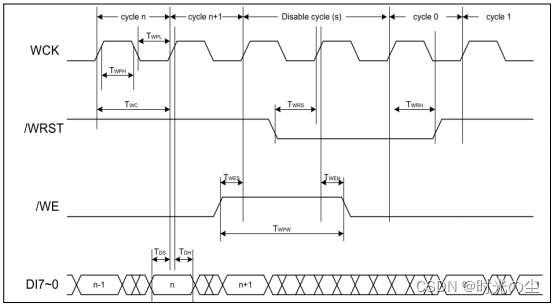

2.1 写时序

在写时序中,当 WE 管脚为低电平时,FIFO 写入处于使能状态,随着读时钟 WCK 的运转, DI[0:7]表示的数据将会就会按地址递增的方式存入 FIFO;当 WE 管脚为高电平时,关闭输入,DI[0:7]的数据不会被写入 FIFO。

在控制写入数据时,一般会先控制写指针作一个复位操作:把 WRST 设置为低电平,写指针会复位到 FIFO 的 0 地址,然后 FIFO 接收到的数据会从该地址开始按自增的方式写入。

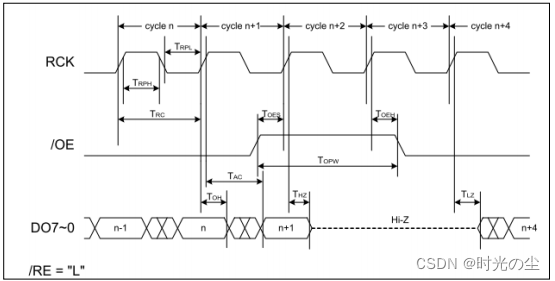

2.2 读时序

FIFO 的读时序类似,不过读使能由两个引脚共同控制,即 OE 和 RE 引脚均为低电平时,输出处于使能状态,随着读时钟 RCK 的运转,在数据输出管脚 DO[0:7]就会按地址递增的方式输出数据。

类似地,在控制读出数据时,一般会先控制读指针作一个复位操作:把 RRST 设置为低电平,读指针会复位到 FIFO 的 0 地址,然后 FIFO 数据从该地址开始按自增的方式输出。

3. 摄像头的驱动原理

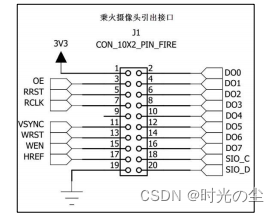

这里我使用的是野火的OV7725摄像头,其接线如下对于排母部分:

|

管脚名称

|

管脚关系

|

管脚描述

|

|

OE

|

FIFO

的

OE

引脚

|

数据输出使能,低电平有效

|

|

RRST

|

FIFO

的

RRST

引脚

|

读指针复位信号,低电平有效

|

|

RCLK

|

FIFO

的

RCK

引脚

|

数据输出同步时钟

|

|

VSYNC

|

OV7725

的

VSYNC

引脚

|

场同步信号

|

|

WRST

|

FIFO

的

WRST

引脚

|

写指针复位信号,低电平有效

|

|

WEN

|

与下面的

HREF

共同组成与非门的输入

|

与

HREF

共同控制

FIFO

的

WE

引脚,

WEN

与HREF 同时为高电平时,

WE

为低电平,

OV7725可以向 FIFO

写入数据

|

|

HREF

|

OV7725

的

HREF

引脚

|

行同步信号

|

|

DO[0:7]

|

FIFO

的

DO[0:7]

引脚

|

数据输出引脚

|

|

SIO_C

|

OV7725

的

SCL

引脚

|

SCCB

总线的时钟线

|

|

SIO_D

|

OV7725

的

SDA

引脚

|

SCCB

总线的数据线

|

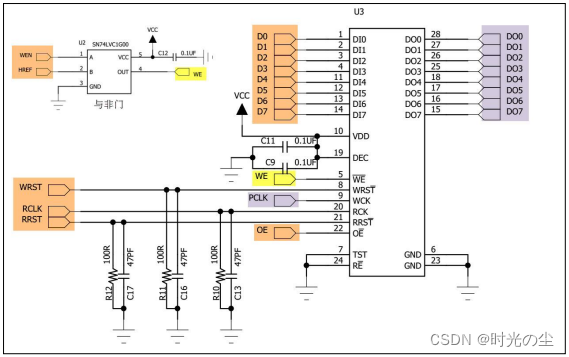

通过下图我们可以了解到,与 OV7725 传感器像素输出相关的PCLK 和 D[0:7]并没有引出,因为这些引脚被连接到了 FIFO 的输入部分,OV7725 的像素输出时序与 FIFO 的写入数据时序是一致的,所以在 OV7725 时钟 PCLK 的驱动下,它输出的数据会一个字节一个字节地被 FIFO 接收并存储起来。

其中最为特殊的是 WEN 引脚,它与 OV7725 的 HREF 连接到一个与非门的输入,与非门的输出连接到 FIFO 的 WE 引脚,因此,当 WEN 与 HREF 均为高电平时,FIFO 的 WE 为低电平,此时允许 OV7725 向 FIFO 写入数据。

外部控制器通过控制 WEN 引脚,可防止 OV7725 覆盖了还未被控制器读出的旧 FIFO数据。另外,在 OV7725 输出时序中,只有当 HREF 为高电平时,PCLK 驱动下 D[0:7]线表示的才是有效像素数据,因此,利用 HREF 控制 FIFO 的 WE 可以确保只有有效数据才被写入到 FIFO 中。

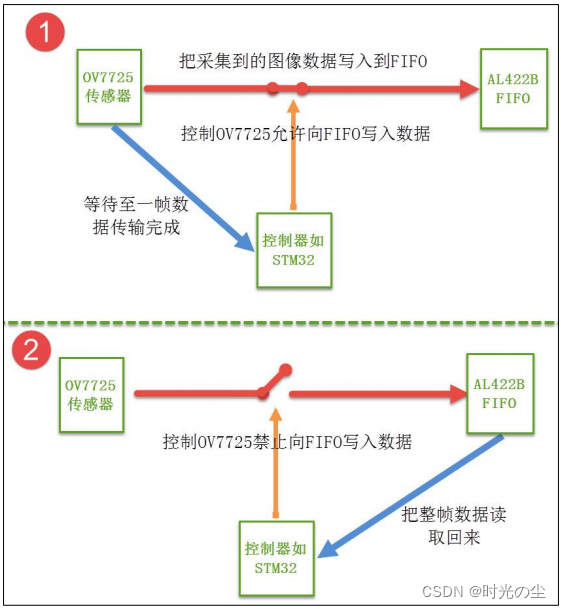

摄像头采集数据的过程如下:

(1) 利用 SIO_C、SIO_D 引脚通过 SCCB 协议向 OV7725 的寄存器写入初始化配置;

(2) 初始化完成后,OV7725 传感器会使用 VGA 时序输出图像数据,它的 VSYNC 会首先输出帧有效信号(低电平跳变),当外部的控制器(如 STM32)检测到该信号时,把 WEN 引脚设置为高电平,并且使用 WRST 引脚复位 FIFO 的写指针到 0 地址;

(3) 随着 OV7725 继续按 VGA 时序输出图像数据,它在传输每行有效数据时, HREF引脚都会持续输出高电平,由于 WEN 和 HREF 同时为高电平输入至与非门,使得其连接到 FIFO WE 引脚的输出为低电平,允许向 FIFO 写入数据,所以在这期间,OV7725 通过它的 PCLK 和 D[0:7]信号线把图像数据存储到 FIFO 中,由于前面复位了写指针,所以图像数据是从 FIFO 的 0 地址开始记录的;

(4) 各行图像数据持续传输至 FIFO,受 HREF 控制的 WE 引脚确保了写入到 FIFO 中的都是有效的图像数据,OV7725 输出完一帧数据时,VSYNC 会再次输出帧有效信号,表示一帧图像已输出完成;

(5) 控制器检测到上述 VSYNC 信号后,可知 FIFO 中已存储好一帧图像数据,这时控制 WEN 引脚为低电平,使得 FIFO 禁止写入,防止 OV7725 持续输出的下一帧数据覆盖当前 FIFO 数据;

(6) 控制器使用RRST复位读指针到FIFO的0地址,然后通过FIFO的RCLK和DO[0:7]引脚,从 0 地址开始把 FIFO 缓存的整帧图像数据读取出来。在这期间,OV7725是持续输出它采集到的图像数据的,但由于禁止写入 FIFO,这些数据被丢弃了;

(7) 控制器使用 WRST 复位写指针到 FIFO 的 0 地址,然后等待新的 VSYNC 有效信号到来,检测到后把 WEN 引脚设置为高电平,恢复 OV7725 向 FIFO 的写入权限,OV7725 输出的新一帧图像数据会被写入到 FIFO 的 0 地址中,重复上述过程。

把 OV7725 配置为 240*320 分辨率(QVGA),RGB565 格式,那么 OV7725 输出一帧的图像大小为 240*320*2=153600 字节,而本摄像头采用的 FIFO 型号 AL422B 容量为 393216 字节,最多可以缓存 2 帧这样的图像,通过这样的方式,STM32 无需直接处理 OV7725 高速输出的数据。但是,如果配置 OV7725为 480*640 分辨率时,其一帧图像大小为 480*640*2=614400 字节,FIFO 的容量不足以直接存储一帧这样的图像,因此,当 OV7725 往 FIFO 写数据的时候,STM32 端要同时读取数据,确保在 OV7725 覆盖旧数据的之前,STM32 端已经把这部分数据读取出来了。

7704

7704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?