ARM与DSP的PCIE通信调试

这两天在调试ARM从DSP获取编码ES的程序,有些知识觉着需要记录下来,毕竟岁数大了记性变差了。

言归正传,以图像编码为例,对图像编码任务来说ARM与DSP的通信产生在YUV和ES数据的交互层面,其中ARM采集YUV数据通过PCIE总线传输给DSP进行编码,DSP编码后的ES数据再通过PCIE总线还回ARM,ARM将ES打包发送,如何高效的利用PCIE总线特性完成数据交互任务,是一个值得研究的问题。

一、posted和Non-posted

说到PCIE传输不得不提到PCIE的两种传输方式,posted和Non-posted,在sprugx7b.pdf 17.2.2节有详细介绍。

可以看出Memory Read 是 Non-posted的方式,Memory Write是posted方式。关于两种方式的具体含义区别参考下面的说明(来源网络)。

PCI总线规定了两类数据传送方式,分别是Posted和Non-Posted数据传送方式。其中使用Posted数据传送方式的总线事务也被称为Posted总线事务;而使用Non-Posted数据传送方式的总线事务也被称为Non-Posted总线事务。

其中Posted总线事务指PCI主设备向PCI目标设备进行数据传递时,当数据到达PCI桥后,即由PCI桥接管来自上游总线的总线事务,并将其转发到下游总线。采用这种数据传送方式,在数据还没有到达最终的目的地之前,PCI总线就可以结束当前总线事务,从而在一定程度上解决了PCI总线的拥塞。

而Non-Posted总线事务是指PCI主设备向PCI目标设备进行数据传递时,数据必须到达最终目的地之后,才能结束当前总线事务的一种数据传递方式。

显然采用Posted传送方式,当这个Posted总线事务通过某条PCI总线后,就可以释放PCI总线的资源;而采用Non-Posted传送方式,PCI总线在没有结束当前总线事务时必须等待。这种等待将严重阻塞当前PCI总线上的其他数据传送,因此PCI总线使用Delayed总线事务处理Non-Posted数据请求,使用Delayed总线事务可以相对缓解PCI总线的拥塞。

Posted数据请求在通过PCI总线之后,将逐级释放总线资源,因此PCI总线的利用率较高。而使用Non-Posted方式进行数据传送的处理过程与此不同,Non-Posted数据请求在通过PCI总线时,并不会及时释放总线资源,从而在某种程度上影响PCI总线的使用效率和传送带宽。

二、ARM获取ES的两种方案对比

ARM传输YUV数据的方式,采用ARM端主动写YUV数据到outbound地址区域,然后由PCIE总线映射数据到对端DSP,这种方式是posted。而ARM获取ES数据之前考虑了两种方案,下面展开两个方案看看经过测试选择那个方案最合适。

1、方案1

方案1

方案1如图所示,ARM端通过设置OB寄存器将本地OB空间映射到PCIE总线,DSP将这段PCIE总线地址通过设置本地IB寄存器映射到本地地址域。ES传输时ARM读取OB空间的标志位,当ES准备好后,ARM读取OB空间数据传输到后端进行打包发送。

这里需要注意的是,每次ARM在OB空间的读操作都会发起一次PCIE总线事务,而这个事务的类型是Non-posted,而Non-posted方式是一种同步的方式,是比较耗费PCIE总线资源的(可简单理解为请求--应答的方式如图所示),同时也耗费CPU资源。

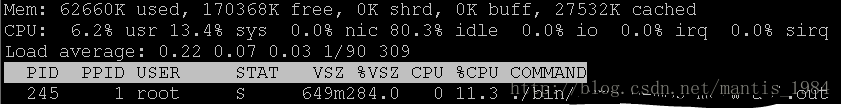

采用此种方案进行1920x1080@30fps,4000kbps条件下的自编自解测试,运动图像条件下(摄像机前晃手),查看CPU占用率,如下图所示:

样本1:

样本2:

样本3:

CPU占用率在20%~25%之间

2、方案2

方案2

方案2如图所示,与方案1相反,DSP端利用起自己的OB空间和OB寄存器,ARM端使用IB寄存器将对应的PCIE空间映射到本地的普通内存上,这样还是ARM去读本地普通内存上的数据,但是这个读取的过程并不会发起PCIE总线事务,只有在DSP主动写它自己的OB空间时才会发起一次总线事务,这个写数据的过程是posted方式的,比方案1理论上是效率高的更好方式。

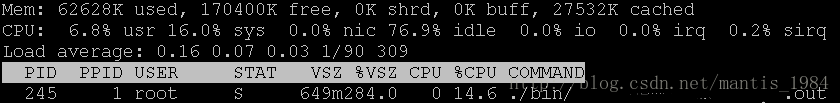

采用此种方案进行1920x1080@30fps,4000kbps条件下的自编自解测试,运动图像条件下(摄像机前晃手),查看CPU占用率,如下图所示:

样本1:

样本2:

样本3:

CPU占用率10%~15%

CPU占用率的下降有PCIE总线事务改为posted方式带来的,另外比方案1少了1次数据拷贝的环节。

1182

1182

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?