目录

3.2 配置地址空间(Configuration Address Space)

3.2.1 PCI兼容配置寄存器空间(PCI-Compatible Configuration Register Space)

3.2.2 扩展配置空间(Extended Configuration Space)

三、PCIe拓扑与配置地址空间

3.1 定义说明

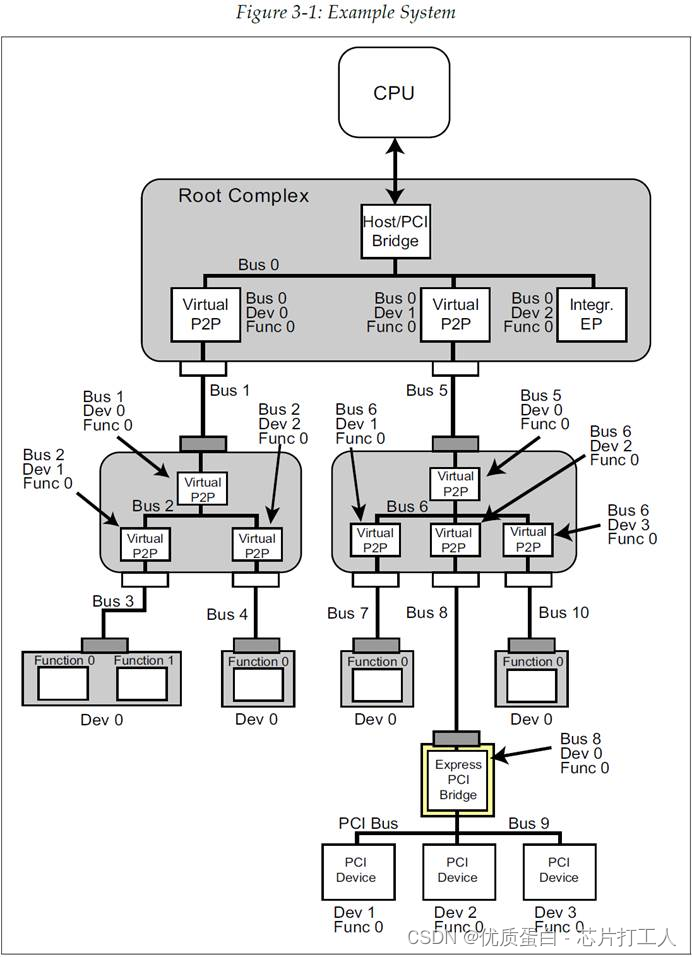

“BDF”标识:连接在PCIe总线上的设备通过总线(Bus)号、设备(Device)号和功能(Function)号所唯一标识。下图展示了一个PCIe拓扑,在此主要关注其中的Buses、Devices和Functions。

3.1.1 总线(Bus)

- 总线号至多可包含256个(Bus 0至Bus 255)。

- 每个Bus必须被分配一个唯一的总线号。

- Bus 0通常由硬件分配给RC。Bus 0由一个集成有EP的虚拟PCI总线,一到多个虚拟PCI-to-PCI Bridges(P2P Bridges)组成,其中的P2P Bridges拥有硬件编码、不可更改的设备号和功能号,每个P2P Bridge都会产生一个新的Bus,供其他PCIe设备连接。

- 软件通过“深度优先搜索”位总线分配总线号。

3.1.2 设备(Device)

- 单个PCIe至多允许单个PCI总线上挂载32个设备。

- PCIe点对点的连接要求使得仅有一个设备可以连接在PCIe链路上,就是Device 0(由图可见每个bus下方的设备号都是Device 0)。

3.1.3 功能(Function)

- Functions可能包含硬盘驱动接口、显示控制器、以太网控制器、USB控制器等。

- 每个设备至少有一个功能Function 0,至多有8个功能。

- 多Function的设备不需要依次按照编号逐个实现 Function,例如,一个设备可以只实现Function 0、2、7。

- 每个Function都有它们自己的配置地址空间,这个配置地址空间用于设置与Function相关的资源。

- 当配置软件检测到了一个多Function设备时,必须检查所有可能的Function。

3.2 配置地址空间(Configuration Address Space)

早在PCI中就已经实现了标准化的配置寄存器,可通过配置软件进行系统资源的分配和配置,以此消除每个插件卡之间的memory、IO和中断的设置冲突。

PCI为每个Function都定义了一个专用的配置地址空间块,映射在这个配置空间中的寄存器们(即PCI兼容配置寄存器空间)使得软件可以发现这个Function的存在,并对这个Function进行一般操作和状态检查。

3.2.1 PCI兼容配置寄存器空间(PCI-Compatible Configuration Register Space)

每个Function都含有256byte的PCI兼容配置寄存器空间,这部分空间本是为PCI所设计的,如下图。

这个配置空间的前16DW(64 bytes)是配置头部(Header),Header分为Type 0和Type 1两种。剩余的48DW(192 bytes)是一些可选寄存器,包括PCI能力结构(Capability Structure)。

3.2.1.1 Type 0 Header

Type 0设备通常为Endpoint,如显卡、网卡、存储设备等。

- Device ID:PCI设备的设备号

- Vendor ID:设备的厂商的编号

- Status:PCI设备状态寄存器,用于保存PCI设备的状态,如中断状态或运行产生错误时的状态。

- Command:PCI设备命令寄存器, 在PCI设备使能pci_enable_device时会配置该寄存器。主要时负责使能或关闭PCI设备的I/O访问,memory访问和INTx中断等。

- Class Code:设备分类信息, 表示PCI设备属于哪一种类别,如网卡,存储卡,显卡等。

- Revision ID:表示PCI设备的版本号

- Header type:PCI设备头类型寄存器,表示该设备时Endpoint设备还是Bridge设备

3.2.1.2 Type 1 Header

Type 1设备通常为Bridge,包括RC和Switch端口中的P2P Bridge。

3.2.2 扩展配置空间(Extended Configuration Space)

当引入PCIe之后,最初始的256byte配置空间已经不足以放下所有的Capability Structure。因此配置空间的大小从原先的每个Function 256 bytes扩展至了每个Function 4k bytes。新增加出来的960DW扩展配置空间只能通过增强配置机制(Enhanced Configuration Mechanism)来进行访问。

传统PCI软件无法发现这个区域并进行访问,所以这部分区域对于 PCI 是不可见的。

上篇:PCIe学习笔记2:PCIe体系架构——PCIe设备层次

下篇:更新中

3133

3133

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?