目录

2.2.1 设备核心层(Device Core/Software Layer)

2.2.2.1 事务层数据包(Transaction Layer Packet,TLP)

2.2.3.1 链路层数据包(Data Link Layer Packet,DLLP)

2.2.3.2 Ack/Nak协议(Ack/Nak Protocol)

二、PCIe设备层次

2.1 概览

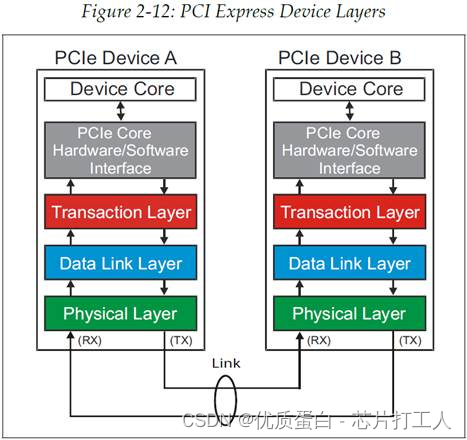

PCIe 定义了一种分层的体系结构,这些层在逻辑上是相互独立的,且各层仅负责相同层内的通信(例如,发送端和接收端的事务层都只处理数据包的事务层信息),各层都有一个用于发出信息流的发送端和一个接收信息流的接收端。

根据上图,由上至下对各层进行说明:

- 设备核心层以及它与事务层的接口(PCIe Core Hardware/Software Interface)。设备核心层实现设备的主要功能——如果设备是一个endpoint,那么它最多可以包含 8 个功能(function),每个功能实现自己的配置空间;如果设备是一个swtich,那么其核心由数据包路由逻辑和内部总线构成;如果设备是一个 RC,那么其核心会实现一个虚拟的 PCI 总线 0,在这个虚拟的 PCI 总线 0中存在着所有的芯片组嵌入式端点以及虚拟桥。

- 事务层(Transcation Layer)。事务层负责TLP(Transaction Layer Packet,事务层包)的产生(发送端)和解析(接收端),同时也负责 QoS(Quality of Service,服务质量)、流量控制以及事务排序。

- 数据链路层(Data Link Layer)。数据链路层负责DLLP(Data Link Layer Packet,数据链路层包)的产生和解析,同时负责链路错误检测以及修正(也称为Ack/Nak 协议)。

- 物理层(Physical Layer)。物理层负责字符序列包的产生和解析。具体而言,物理层实现TLP、DLLP和字符序列包在物理链路上的发送与接收。在发送端,数据包将经过字节条带化逻辑、扰码器、编码器(8b/10b编码或128b/130b编码)和并-串转换模块的处理;在传输链路上,数据包将以训练后的链路速率以差分形式传输;在接收端,物理层须从数据流中恢复出时钟(Clock and Data Recovery,CDR,时钟数据恢复),数据包将经过串-并转换模块、缓存、解码器、解扰器和字节交换恢复逻辑(对应在发送端的逆操作)。此外,物理层中包含LTSSM(Link Training and Status State Machine,链路训练状态机),负责进行链路初始化以及训练。

注意:区别TLP、DLLP和字符序列包,三者之间并非包含关系。

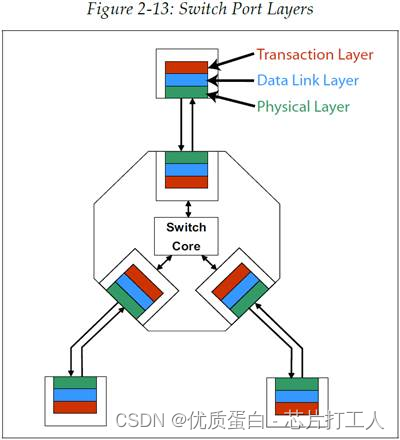

每个 PCIe 接口都支持以上各层的功能,包括switch端口,因为路由信息是需要通过数据包的内部查看的。

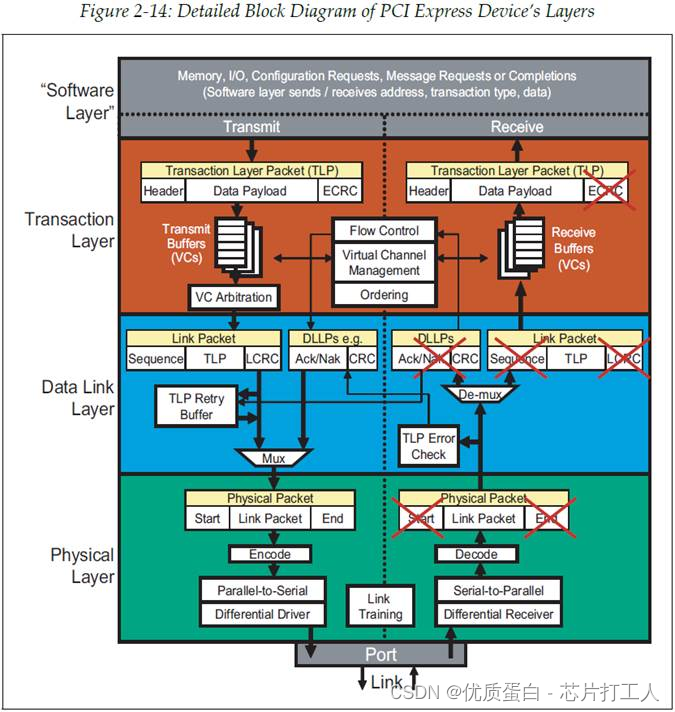

各层的递进:

发送端——设备所发出的请求包或者完成包是在事务层进行组包的,组包所用到的信息由设备核心层所提供,通常包括命令类型、目标设备的地址、请求的属性特征等等。组好的数据包会被存入一个被称为虚拟通道缓存(VCs),发往下一个层级。当这个包被发给数据链路层后,数据链路层会在数据包中加入额外的信息以供接收方进行错误检查,而且这个数据包会在本地储存下来,以便在对端检测到传输错误时重新发送该数据包。当数据包到达物理层处理后将进行传输。

接收端——数据包在物理层进行处理(例如错误检查)后将发往数据链路层,在数据链路层,数据包进行该层的错误检查,若未错误便发往事务层。在事务层数据包被缓存、错误检测,并解析原始信息(命令、属性等),以便将这些数据传输到设备核心层。

2.2 层次详解

2.2.1 设备核心层(Device Core/Software Layer)

设备核心层并不是 PCIe 协议规范中所定义的一个层级,但其位于事务层的上方,是所有请求的源头或是目的地。设备核心层为事务层提供了需要发送的请求信息,其中的信息包括事务类型、地址、需要传输的数据量等等。

2.2.2 事务层(Transaction Layer)

为了响应来自软件层的请求,事务层生成出站数据包(outbound packet);事务层也会检查入站数据包(inbound packet),并将入站数据包内包含的信息向上转发给软件层。

2.2.2.1 事务层数据包(Transaction Layer Packet,TLP)

TLP存在四种请求类型:内存(Memory)、IO、配置(Configuration)、消息(Message)。这四种请求类型还可以归为两类:非报告(Non‐posted )和报告(Posted),见下表。

| 请求类型 | Non-posted / Posted |

|---|---|

| Memory Read | Non‐posted |

| Memory Write | Posted |

| Memory Read Lock | Non‐posted |

| IO Read | Non‐posted |

| IO Write | Non‐posted |

| Configuration Read (Type 0 and Type 1) | Non‐posted |

| Configuration Write (Type 0 and Type 1) | Non‐posted |

| Message | Posted |

对于非报告式请求,发起方首先向完成方发送一个请求数据包,完成方应该产生一个完成包作为响应。

- 所有的读请求都是非报告式的,因为读请求所请求的数据需要通过完成包来返回给发起方。

- IO 写请求和配置写请求也是非报告,因为这两种请求需要目标设备在写入完成后返回完成包,以此来让发起方确认数据被正确写入到目的设备中。

- 内存写请求和消息请求都是报告式的,发起方不需要等待响应,可提升总线整体性能。

需要注意的是,尽管报告式请求不要求返回完成包,但报告式写操作仍然要参与数据链路层的 Ack/Nak协议,以此来保证较为可靠的数据包传输。

2.2.2.2 TLP的组包与拆包

当 TLP 途经发送方各层次时,各层次分别会向数据包中添加一些信息,逐层包裹组包;接收方各层次会分别根据对应层所添加的信息来进行拆包和校验。TLP数据包的结构如下图。

组包

- 设备核心层将组成 TLP 的核心部分的首部(Header)和数据(Data)发送给事务层。TLP必须包含一个首部,但可能没有数据。

- 事务层可选择向数据包中添加ECRC(End-to-End CRC, 端到端循环冗余检测)字段,用于事务层错误检测。

- 数据链路层向 数据包中添加序列号(Sequence Number)和 LCRC(Link CRC, 链路CRC) ,LCRC被用于数据链路层错误检测。

- 物理层向数据包中添加特定的字段,例如Start和End字段。PCIe 1.X和PCIe 2.X规范中物理层将额外添加控制字段,但在PCIe 3.X及之后则不再在物理层使用控制字段。

拆包

- 物理层将确认当前比特流中是否存在正确的Start、End或者其他字段,并将它们剥除,然后将剥除了这些字段后的数据包转发给数据链路层。

- 数据链路层将进行 LCRC 以及序列号的校验。如未发现错误,那么数据链路层将会把 LCRC 和序列号从数据包剥除,并将其转发给事务层。

- 事务层的处理存在需考虑以下情况:如果接收方是一个switch,事务层将从TLP的首部中获取路由信息并确定这个数据包要被转发到哪一个端口,此时switch可以选择对这个 TLP 进行 ECRC校验并及时汇报错误,但是switch无权更改TLP中的ECRC字段;如果接收方是TLP 的目的设备,且ECRC校验正确,事务层将剥除 ECRC 字段并将剩余部分转发给设备核心层。

可见,组包和拆包实际上是操作与逆操作的过程。

注意:数据包在到达目的设备之前,经过总线中每一个设备时都将进行上述步骤的拆包和组包,且每一次组包设备都会计算出一个新的 LCRC 值添加至数据包中。数据包转发的过程只有事务层的信息(红色部分)是不进行操作的,因此可以确保在目的设备处ECRC能发挥事务层的错误校验作用。

2.2.3 数据链路层(Data Link Layer)

数据链路层主要实现3个功能:错误纠正、流量控制以及一些链路电源管理,在此暂不赘述。本小节主要对链路层数据包和数据链路层的Ack/Nak协议进行说明。

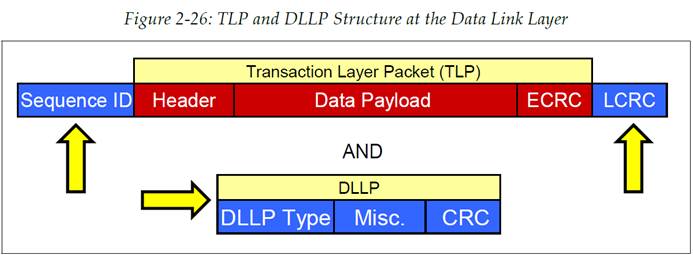

2.2.3.1 链路层数据包(Data Link Layer Packet,DLLP)

在一条链路上,DLLP 是一种在本端设备的数据链路层与对端设备的数据链路层之间传输的数据包,其结构如下图。

DLLP仅在某一链路中传输,且不会发送至事务层。数据链路层会向DLLP Core添加一个16位的CRC,用作接收方数据链路层的错误校验。

2.2.3.2 Ack/Nak协议(Ack/Nak Protocol)

本小节内容摘录自《PCI Express Technology 3.0》,是一个非常好的示例。

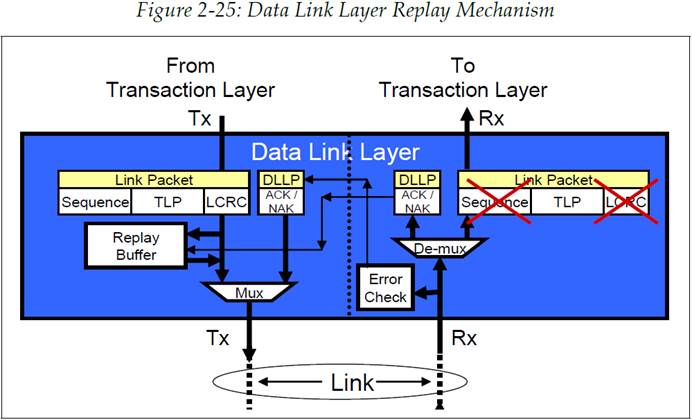

如图2‑25 所示是一种基于硬件的自动重试机制。如图2‑26 所示,每一个被发送方发出的 TLP 都被加上了 LCRC 与序列号,在接收方会对这两个信息进行检查。发送方的重传缓存保存着每个被发送的 TLP 的副本,直到对端确认成功收到了这个 TLP。这个确认成功收到的过程是通过接收方发送 Ack DLLP 来实现的,在这个 Ack DLLP 中包含有接收方成功接收的上一个 TLP 的序列号。当发送方收到这个 Ack DLLP,它将会把里面序列号所对应的 TLP、以及这个 TLP 之前的所有 TLP,都从重传缓存内清除。

如果接收方检测到了一个 TLP 错误,它将会把这个 TLP 丢弃,并向发送方返回一个 Nak DLLP,以期望发送方能对未确认成功接收的 TLP 进行重传,并通过重传获得一个完好的 TLP。由于错误检测通常是十分迅速的操作,因此从错误检测开始到发起重传的时间也比较短,这样就可以在较短的时间内纠正发生的错误。这一操作过程被称为 Ack/Nak(Acknowledge/NotAcknowledge) 协议。

一个 DLLP 的基础形式如图2‑26 所示,它由 4 字节的 DLLP 类型域以及 2 字节 CRC 组成,其中 DLLP 类型域中包含了一些其他的信息。

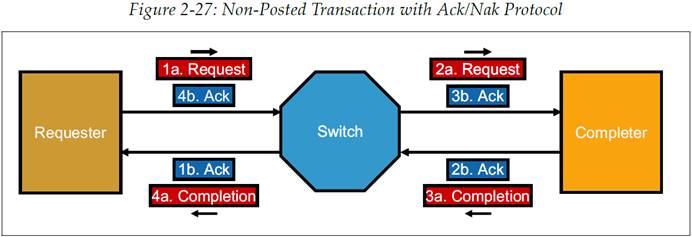

如图2‑27 所示,它展示了一个内存读 TLP 通过交换机的示例。一般来说,这个过程的步骤如下:

-

步骤1a:发起方发送一个内存读请求,并在自身的重传缓存中也保存一个请求包的副本。交换机接收这个 MRd TLP(Memory Read TLP,以后简写为 MRd TLP),并校验 LCRC 以及序列号。

步骤1b:校验未发现出错,因此交换机向发起方返回一个 Ack DLLP。作为响应,发起方将其重传缓存中保存的 MRd TLP 副本丢弃。

-

步骤2a:交换机将这个 MRd TLP 转发到正确的输出端口,使用的路由信息是这个 MRd TLP 的内存地址,在转发出去的同时,交换机会在这个输出端口的重传缓存内保存一份这个 TLP 的副本。完成方接收到这个 MRd TLP 并对其进行错误校验。

步骤2b:校验未发现出错,因此完成方向交换机返回一个 Ack DLLP。作为响应,交换机之前输出这个 TLP 的输出端口会将其重传缓存中保存的这个 MRd TLP 的副本丢弃。

-

步骤3a:作为这个请求的最终目的地,完成方将会校验 MRd TLP 中的 ECRC 字段域,这个字段域是可选的不是必需的。若校验未出错,则将这个请求呈交给设备核心层。然后根据这个请求命令中的相关信息,设备将会收集被请求的数据,发起方返回一个 CplD(Completion with Data TLP,带有数据的完成包),同时它也将在自己的重传缓存中保存这个 CplD TLP 的副本。当交换机接收到这个 CplD TLP 时将会对其进行错误校验。

步骤3b:校验未发现出错,因此交换机向完成方返回一个 Ack DLLP。作为响应,完成方将其重传缓存中保存的这个 CplD TLP 的副本清除。

-

步骤4a:交换机对这个 CplD TLP 中的发起方 ID 进行译码,并通过这个信息将 CplD TLP 路由至正确的输出端口,输出的同时在这个输出端口的重传缓存内保存 CplD TLP 的副本。当发起方接收到这个 CplD TLP 时将会对其进行错误校验。

步骤4b:校验未发现出错,因此发起方向交换机返回一个 Ack DLLP。作为响应,交换机之前输出这个 CplD TLP 的输出端口会将其重传缓存中保存的这个 CplD TLP 的副本丢弃。发起方将校验 ECRC 字段域(这个字段是可选的,不是必需的),校验未出错则将完成包里的数据向上呈交给设备核心层逻辑。

2.2.4 物理层

物理层是 PCIe 协议层次中的最底层,TLP 和 DLLP都需要经过物理层后进行传输。PCIe协议规范中将物理层分为两个部分进行讨论:逻辑部分和电气部分。

- 逻辑部分:包含一系列的数字逻辑,包含将数据包在链路上发送的串行传输逻辑以及接收输入数据包的处理逻辑。

- 电气部分:包含模拟电路接口,与链路直接相连,为每个通道提供差分驱动器以及差分接收器。

2.2.4.1 逻辑部分

在发送端,物理层逻辑部分将由数据链路层转发来的 TLP 与 DLLP数据包,并向数据包添加包起始字段和包结束字段(如下图所示),并进行字节条带化和扰码。

- 字节条带化(byte striping):在物理层中,数据包中的每一个字节都将被分割到链路所使用的所有lanes,这一过程被称为字节条带化,每个lane在链路上都扮演着一个独立的串行传输路径,这些lanes各自传输的数据会在接收端被聚合。

- 扰码:传输前每个字节都进行了扰码,以减少传输连续重复的“0”或“1”,这有助于减少链路上的 EMI(electro-magnetic interference,电磁干扰),并有利于将参考时钟从数据流中恢复(Clock Data Recovery,CDR,时钟数据恢复)。

2.2.4.2 电气部分

电气部分的发送器和接收器通过一个交流耦合链路相连接,其物理路径上放置电容,信号的高频部分通过,而阻塞低频(直流)部分。这种方式允许发送端和接收端的共模电压存在差异,意味着发送端和接收端可以使用不同的参考电压。

2619

2619

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?