题目来自HDLBits - Module fadd

定义1位全加器模块,

module add1 ( input a, input b, input cin, output sum, output cout );

// Full adder module here

assign sum = a ^ b ^ cin;

assign cout = (a&b) | (b&cin) | (cin&a);

endmodule顶层模块例化32个1位全加器,并完成级联,

module add32 (

input [31:0] a,

input [31:0] b,

output [31:0] sum,

output cout

);

wire [31:0] c; // 进位

generate

genvar i;

for(i = 0; i < 32; i = i + 1) begin: gen_add

if (i == 0) begin

add1 add1_inst(

.a(a[i]),

.b(b[i]),

.cin(1'b0),

.sum(sum[i]),

.cout(c[i])

);

end

else begin

add1 add1_inst(

.a(a[i]),

.b(b[i]),

.cin(c[i-1]),

.sum(sum[i]),

.cout(c[i])

);

end

end

endgenerate

assign cout = c[31];

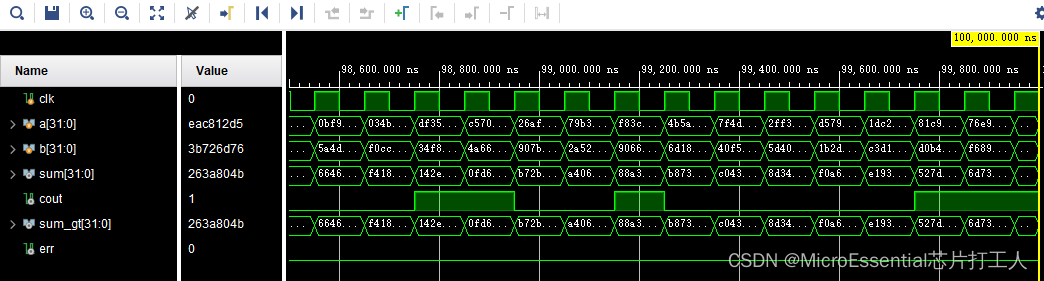

endmodule仿真验证波形如下,

3969

3969

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?