13.2 QUEST: A 7.49TOPS Multi-Purpose Log-Quantized DNN Inference Engine Stacked on 96MB 3D SRAM Using Inductive-Coupling Technology in 40nm CMOS

第一段:

第一段的主要意思是,DNN实现的加速器需要大的和宽带宽的存储(large and high-bandwidth external memories)。一开始用DRAM,但是DRAM的延迟太高,严重限制性能。之后有算法层面的改进,网络修剪和压缩(network pruning and compression),有点东西。然而,修剪完的网络编的不规则和稀疏,又出现了新的问题:对存储器系统的灵活随机存取(agile random accesses to the memory systems)变得更有需要了。

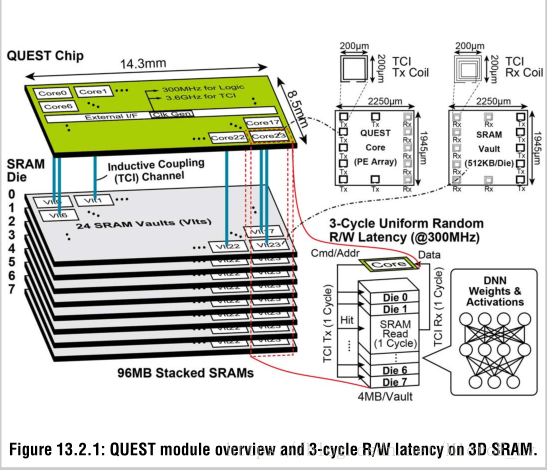

第二段:Figure 13.2.1

这一段基本都会在阐明这样一种堆叠方式。最上方是一块QUEST芯片,下方堆叠了8块SRAM的die。两个部分通过电感耦合的方式进行无线连接。这种方式称为TCI,ThruChip Interface。平行的TCI通道可以给QUEST提供多条高带宽的数据存取通路指向堆叠着的SRAM,更好的是SRAM还可以以超低延迟进行随机存取,虽然SRAM本身很小,但是3D的堆叠就可以提供出更大的SRAM存储空间。

Power/Ground 通过TSV(Through Silicon Vias穿过硅片的通路)的方式进行提供。

QUEST上本身集成了24块处理核心单元,每个单元又与32bit宽4MB大小的SRAM相连。整个的读写延迟包括TCI的时间总共是三个周期,这对八个SRAM芯片是一样的。

TSV主要是用于die的堆叠,但是它存在着open-contact faulure断路失败。解决方法就是,在设计中,左右的transmission信号传输都用的是TCI通道,整个3D模型就会限制TSV在源或者地网格中的应用,着花样大量的平行链接会让这样的问题得到解决。

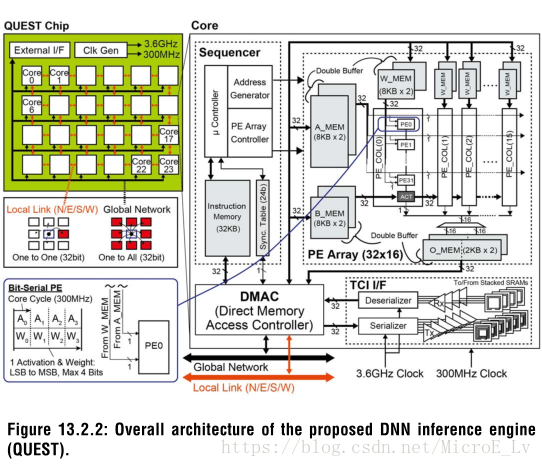

第三段:Figure 13.2.2

这张图主要是向我们展示了一个QUEST芯片的整体结构和每个core单元的工作方式。所有Core的工作方式是一种MIMD-Parallel的行为方式,就是并行运算。它们之间通过Global Network或者local link相连。每个core的内部否有微编程的序列器用于控制PE单元。整个core的同步性是用一个同步表synchronization table来实现的。还有一个DMAC(Direct Memory Access Controller)作为内部存储与外部SRAM之间的存取中间站。Weights权重通过W-MEMs分配给每个PE,这是一个平行行为。Activations通过A-MEM以一个row-parallel的方式分给PE。Bias通过移位进入。最后生成output activations 写入O_MEM中。

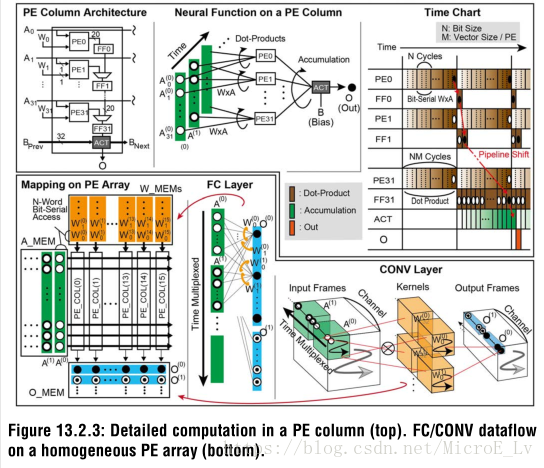

第三段:Figure 13.2.3

上面共有五幅图。第一幅图显示的是,同一column的PE,每个PE都可以获得不同的Weights,但是同一row的PE,每个PE得到的是相同的Activation。

第二幅图显示的是,在一个PE的column中,部分的点积首先被计算出来,通过移位被汇集到ACT中。

第三幅图显示的是一个时间表,里面表示出的是平行PE、位串行和点积计算。这样的机制是这个结构能够将多种DNN应用于单一PEarray结构的关键。

第四幅图与第五幅图将的主要是全连接层与卷积层的解决方法吧……说实话没太看懂。

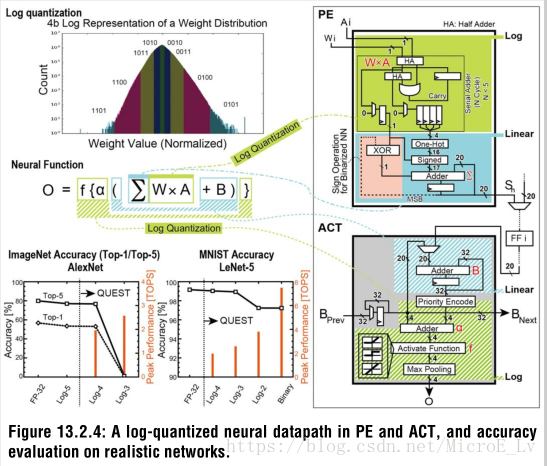

第四段:Figure 13.2.4

第四段主要是在讲这是如何通过log量化log-quantized来实现各种各样的运算。

log-quantized比linear quantized有两个方面好得多,一个是“denser the finer”越密集越好的特点使得其用于代表weights/activation 的分配是个更好的选择;另一个是资源消耗的乘法操作可以简化为加法,因为对数化之后加法就是操作数的乘法。在PE中的点乘可以转化为“log”的位串行加法和线性的汇集,ACT汇集了加法之后再加上bias偏移,再应用一下scaling/activation函数(对数方法)。这lightweightPE结构使得密集的PEarray可以与W_MEMs和A_MEMs紧密相连,实现综合性的平行NN计算。

log-quantized实现准确性可以从上图的左下角的小图里面看出来。

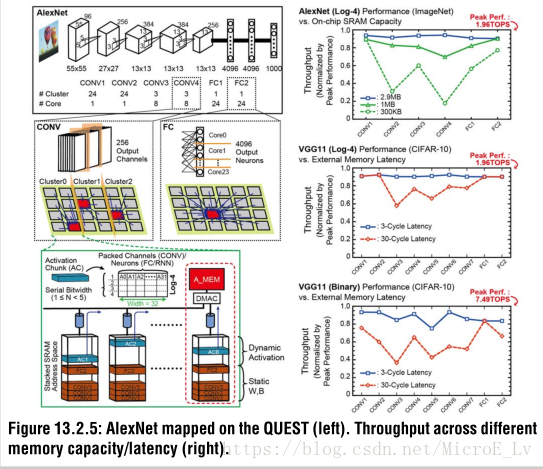

第五段:Figure 13.2.5

这一段主要做了对一个优越性的阐述。

前半部分,也是上图左半部分主要是描述QUEST 3D 模块应用于AlexNet上的处理过程。24快核心单元各自去一层层的处理数据,产生结果写入SRAM或者从SRAM上读取结果。对于卷积层来说,QUEST是将cores分群(cluster)一个channel映射到本群里所有core上,使得core可以共用一个输入channel。

对于全连接层,输出的神经元映射到所有的cores。

这两种情况,每个core上的计算都需要从SRAM上读取activations ,这通过的是TCI通道和芯片上的数据通道网络。这种数据存取分散到每个单独的存储单元,并且脉冲时间非常的短。

后半部分,也就是上图的右半部分。第一个曲线表表达的是,有2.9MB芯片存储空间对于整体的网络表现是非常重要的,1MB和300KB的存储空间明显可以看出网络表现的差距。

第二个曲线表达的是随机存取延迟random-access latency对网络性能的影响。这里使用VGG11进行试验。可以看出3-Cycle的延迟性能上要比30-Cycle的延迟好太多。

最后一个曲线与第二个曲线进行对比,不同量化方式的相同表现可以验证延迟对性能的影响。

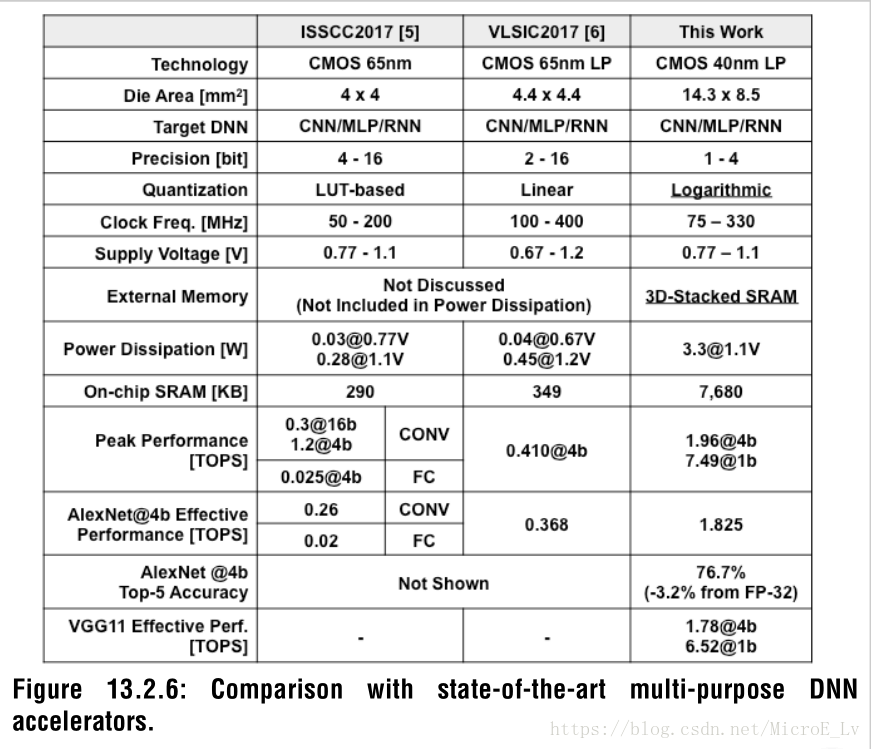

第六段:Figure13.2.6

第七段:总结特点

QUEST的目标是“rapidly revolutionizing highly compressed DNNs”。

有仨特点:

第一,3D综合,用的是大容量和带宽,同时低延迟的快速存取SRAM。

第二,对PEarray计算中的CONV/FC等各种DNN层的灵活数据流支持flexible dataflow support 。

第三,一种位串行的PE结构,用于二进制或者log-quantizedDNN量化方法。

288

288

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?