【写在前面】刚入门小菜鸟,记录一下口罩识别学习过程。参考文件和网址会在文末注明。有错误欢迎指出,也欢迎进行补充~

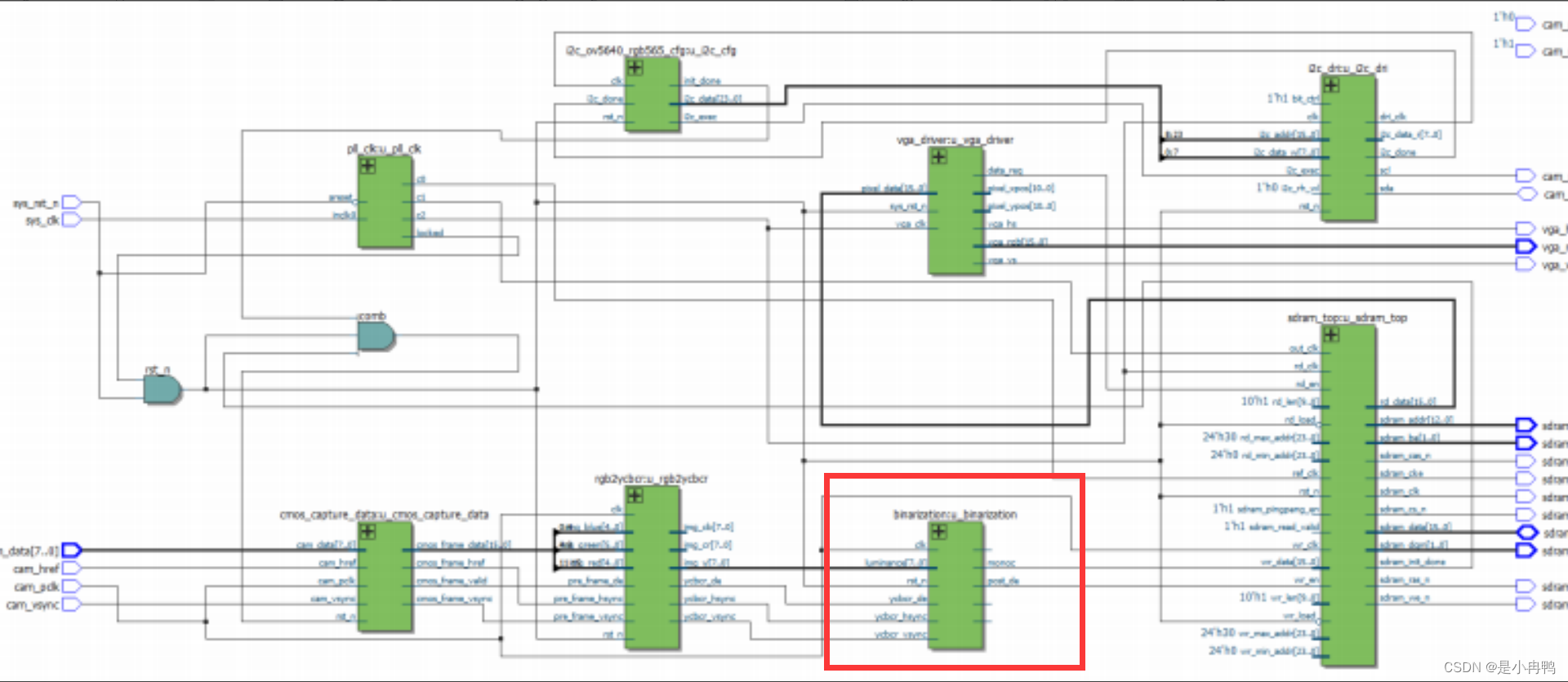

原理图如下,二值化对应为红框里的部分

使用的二值化方法是手动指定一个阈值,通过阈值来进行二值化处理。(还有一种方法是一个自适应阈值二值化方法,在这里未使用)

源码如下:

module binarization(

//module clock

input clk,

input rst_n, //复位信号

//图像处理前数据接口

input ycbcr_vsync,

input ycbcr_hsync,

input [7:0] luminance,

//图像处理后数据接口

output post_vsync,

output post_hsync,

output post_de,

outputreg monoc

);

//reg define

reg ycbcr_vsync_d;

reg ycbcr_hsync_d;

reg ycbcr_de_d;

assign post_vsync = ycbcr_vsync_d ;

assign post_hsync = ycbcr_hsync_d ;

assign post_de = ycbcr_de_d ;

//二值化

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

monoc <= 1'b0;

else if(luminance > 8'd64) //灰度阈值

monoc <= 1'b1; //低于时赋1

else

monoc <= 1'b0; //高于时赋0

end

//延时1拍以同步时钟信号

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

ycbcr_vsync_d <= 1'd0;

ycbcr_hsync_d <= 1'd0;

ycbcr_de_d <= 1'd0;

end

else begin

ycbcr_vsync_d <= ycbcr_vsync;

ycbcr_hsync_d <= ycbcr_hsync;

ycbcr_de_d <= ycbcr_de ;

end

end

endmodule涉及到的知识解释:

1.LCD显示器显像的信号HSync ,VSync

VSYNC:帧同步信号。表示扫描1帧的开始,一帧也就是LCD显示的一个画面。

HSYNC:行同步信号。表示扫描1行的开始。

例如,要显示一个A x B的画面,则有:

VSYNC = HSYNC x B

HSYNC = PCLK x A

再例如:

PCLK:像素时钟,时最小时钟单位,控制整个程序的运行进程。

ENABLE:数据使能,为1时才能接受数据,为0时不能。

P_DATA: 数据输出

上升沿:由0—>1

下降沿:由1—>0

更多知识请看:LCD显示器显像的信号HSync ,VSync - 简书 (jianshu.com)

2.二值化部分

二值化即将灰度值(光亮值)和设定的阈值比较,比较结果以0和1的形式存入monoc中。0和1只是比较的结果,不是像素的实际灰度值。之后需要根据monoc确定像素点的颜色。

3.延时以同步时钟信号

我们在前面使用了一个时钟周期进行二值化,相应的同步信号也应该延迟一个时钟周期,从而实现数据的同步。

参考:《开拓者FPGA开发指南V1.5》

2776

2776

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?