GIC 逻辑分块

GIC 架构分为了两个逻辑块: Distributor 和 CPU Interface,也就是分发器端和 CPU 接口端。

这两个逻辑块的含义如下:

Distributor(分发器端)

示例代码 17.1.3.2 GIC 控制器结构体

/*

* GIC 寄存器描述结构体,

* GIC 分为分发器端和 CPU 接口端

*/

1 typedef struct

2 {

3 /* 分发器端寄存器 */

4 uint32_t RESERVED0[1024];

5 __IOM uint32_t D_CTLR; /* Offset: 0x1000 (R/W) */

6 __IM uint32_t D_TYPER; /* Offset: 0x1004 (R/ ) */

7 __IM uint32_t D_IIDR; /* Offset: 0x1008 (R/ ) */

8 uint32_t RESERVED1[29];

9 __IOM uint32_t D_IGROUPR[16]; /* Offset: 0x1080 - 0x0BC (R/W) */

10 uint32_t RESERVED2[16];

11 __IOM uint32_t D_ISENABLER[16];/* Offset: 0x1100 - 0x13C (R/W) */

12 uint32_t RESERVED3[16];

13 __IOM uint32_t D_ICENABLER[16];/* Offset: 0x1180 - 0x1BC (R/W) */

14 uint32_t RESERVED4[16];

15 __IOM uint32_t D_ISPENDR[16]; /* Offset: 0x1200 - 0x23C (R/W) */

16 uint32_t RESERVED5[16];

17 __IOM uint32_t D_ICPENDR[16]; /* Offset: 0x1280 - 0x2BC (R/W) */

18 uint32_t RESERVED6[16];

19 __IOM uint32_t D_ISACTIVER[16];/* Offset: 0x1300 - 0x33C (R/W) */

20 uint32_t RESERVED7[16];

21 __IOM uint32_t D_ICACTIVER[16];/* Offset: 0x1380 - 0x3BC (R/W) */

22 uint32_t RESERVED8[16];

23 __IOM uint8_t D_IPRIORITYR[512];/* Offset: 0x1400 - 0x5FC (R/W) */

24 uint32_t RESERVED9[128];

25 __IOM uint8_t D_ITARGETSR[512];/* Offset: 0x1800 - 0x9FC (R/W) */

26 uint32_t RESERVED10[128];

27 __IOM uint32_t D_ICFGR[32]; /* Offset: 0x1C00 - 0xC7C (R/W) */

28 uint32_t RESERVED11[32];

29 __IM uint32_t D_PPISR; /* Offset: 0x1D00 (R/ ) */

30 __IM uint32_t D_SPISR[15]; /* Offset: 0x1D04 - 0xD3C (R/ ) */

31 uint32_t RESERVED12[112];

32 __OM uint32_t D_SGIR; /* Offset: 0x1F00 ( /W) */

33 uint32_t RESERVED13[3];

34 __IOM uint8_t D_CPENDSGIR[16];/* Offset: 0x1F10 - 0xF1C (R/W) */

35 __IOM uint8_t D_SPENDSGIR[16];/* Offset: 0x1F20 - 0xF2C (R/W) */

36 uint32_t RESERVED14[40];

37 __IM uint32_t D_PIDR4; /* Offset: 0x1FD0 (R/ ) */

38 __IM uint32_t D_PIDR5; /* Offset: 0x1FD4 (R/ ) */

39 __IM uint32_t D_PIDR6; /* Offset: 0x1FD8 (R/ ) */

40 __IM uint32_t D_PIDR7; /* Offset: 0x1FDC (R/ ) */

41 __IM uint32_t D_PIDR0; /* Offset: 0x1FE0 (R/ ) */

42 __IM uint32_t D_PIDR1; /* Offset: 0x1FE4 (R/ ) */

43 __IM uint32_t D_PIDR2; /* Offset: 0x1FE8 (R/ ) */

44 __IM uint32_t D_PIDR3; /* Offset: 0x1FEC (R/ ) */

45 __IM uint32_t D_CIDR0; /* Offset: 0x1FF0 (R/ ) */

46 __IM uint32_t D_CIDR1; /* Offset: 0x1FF4 (R/ ) */

47 __IM uint32_t D_CIDR2; /* Offset: 0x1FF8 (R/ ) */

48 __IM uint32_t D_CIDR3; /* Offset: 0x1FFC (R/ ) */

49

50 /* CPU 接口端寄存器 */

51 __IOM uint32_t C_CTLR; /* Offset: 0x2000 (R/W) */

52 __IOM uint32_t C_PMR; /* Offset: 0x2004 (R/W) */

53 __IOM uint32_t C_BPR; /* Offset: 0x2008 (R/W) */

54 __IM uint32_t C_IAR; /* Offset: 0x200C (R/ ) */

55 __OM uint32_t C_EOIR; /* Offset: 0x2010 ( /W) */

56 __IM uint32_t C_RPR; /* Offset: 0x2014 (R/ ) */

57 __IM uint32_t C_HPPIR; /* Offset: 0x2018 (R/ ) */

58 __IOM uint32_t C_ABPR; /* Offset: 0x201C (R/W) */

59 __IM uint32_t C_AIAR; /* Offset: 0x2020 (R/ ) */

60 __OM uint32_t C_AEOIR; /* Offset: 0x2024 ( /W) */

61 __IM uint32_t C_AHPPIR; /* Offset: 0x2028 (R/ ) */

62 uint32_t RESERVED15[41];

63 __IOM uint32_t C_APR0; /* Offset: 0x20D0 (R/W) */

64 uint32_t RESERVED16[3];

65 __IOM uint32_t C_NSAPR0; /* Offset: 0x20E0 (R/W) */

66 uint32_t RESERVED17[6];

67 __IM uint32_t C_IIDR; /* Offset: 0x20FC (R/ ) */

68 uint32_t RESERVED18[960];

69 __OM uint32_t C_DIR; /* Offset: 0x3000 ( /W) */

70 } GIC_Type;

从图 17.1.3.2 可以看出,此逻辑块负责处理各个中断事件的分发问

题,也就是中断事件应该发送到哪个 CPU Interface 上去。分发器收集所有的中断源,可以控制

每个中断的优先级,它总是将优先级最高的中断事件发送到 CPU 接口端。分发器端要做的主要

工作如下:

①、全局中断使能控制。

②、控制每一个中断的使能或者关闭。

③、设置每个中断的优先级。

④、设置每个中断的目标处理器列表。

⑤、设置每个外部中断的触发模式:电平触发或边沿触发。

⑥、设置每个中断属于组 0 还是组 1。

CPU Interface(CPU 接口端): CPU 接口端听名字就知道是和 CPU Core 相连接的,因此在

图 17.1.3.2 中每个 CPU Core 都可以在 GIC 中找到一个与之对应的 CPU Interface。 CPU 接口端

就是分发器和 CPU Core 之间的桥梁, CPU 接口端主要工作如下:

①、使能或者关闭发送到 CPU Core 的中断请求信号。

②、应答中断。

③、通知中断处理完成。

④、设置优先级掩码,通过掩码来设置哪些中断不需要上报给 CPU Core。

⑤、定义抢占策略。

⑥、当多个中断到来的时候,选择优先级最高的中断通知给 CPU Core。

core_ca7.h 定义了 GIC 结构体,此结构体里面的寄存器分为了分发器端和 CPU 接口端,

“示例代码 17.1.3.2”中的结构体 GIC_Type 就是 GIC 控制器,列举除了 GIC 控制器的所有寄存器,可以通过结构体 GIC_Type 来访问 GIC 的所有寄存器。

第 5 行是 GIC 的分发器端相关寄存器,其相对于 GIC 基地址偏移为 0X1000,因此我们获取到GIC 基地址以后只需要加上 0X1000 即可访问 GIC 分发器端寄存器。

第 51 行是 GIC 的 CPU 接口端相关寄存器,其相对于 GIC 基地址的偏移为 0X2000,同样的,获取到 GIC 基地址以后只需要加上 0X2000 即可访问 GIC 的 CPU 接口段寄存器。

那么问题来了? GIC 控制器的寄存器基地址在哪里呢?这个就需要用到 Cortex-A 的 CP15 协处理器了,下一小节就讲解 CP15 协处理器。

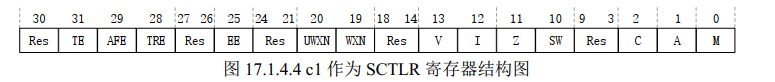

CP15 协处理器

关于 CP15 协处理器和其相关寄存器的详细内容请参考下面两份文档:

《ARM ArchitectureReference Manual ARMv7-A and ARMv7-R edition.pdf》 第 1469 页“B3.17 Oranization of the CP15 registers in a VMSA implementation”。和《Cortex-A7 Technical ReferenceManua.pdf》 第 55 页“Capter 4 System Control”。

CP15 协处理器一般用于存储系统管理,但是在中断中也会使用到, CP15 协处理器一共有16 个 32 位寄存器。 CP15 协处理器的访问通过如下另个指令完成:

MRC: 将 CP15 协处理器中的寄存器数据读到 ARM 寄存器中。

MCR: 将 ARM 寄存器的数据写入到 CP15 协处理器寄存器中。

MRC 就是读 CP15 寄存器, MCR 就是写 CP15 寄存器, MCR 指令格式如下:

MCR{cond} p15, <opc1>, <Rt>, <CRn>, <CRm>, <opc2>

cond: 指令执行的条件码,如果忽略的话就表示无条件执行。

opc1: 协处理器要执行的操作码。

Rt: ARM 源寄存器,要写入到 CP15 寄存器的数据就保存在此寄存器中。

CRn: CP15 协处理器的目标寄存器。

CRm: 协处理器中附加的目标寄存器或者源操作数寄存器,如果不需要附加信息就将

CRm 设置为 C0,否则结果不可预测。

opc2: 可选的协处理器特定操作码,当不需要的时候要设置为 0。

MRC 的指令格式和 MCR 一样,只不过在 MRC 指令中 Rt 就是目标寄存器,也就是从CP15 指定寄存器读出来的数据会保存在 Rt 中。而 CRn 就是源寄存器,也就是要读取的写处理器寄存器。

假如我们要将 CP15 中 C0 寄存器的值读取到 R0 寄存器中,那么就可以使用如下命令:

MRC p15, 0, r0, c0, c0, 0

CP15 协处理器有 16 个 32 位寄存器, c0~c15,本章来看一下 c0、 c1、 c12 和 c15 这四个寄存器,因为我们本章实验要用到这四个寄存器,其他的寄存器大家参考上面的两个文档即可。

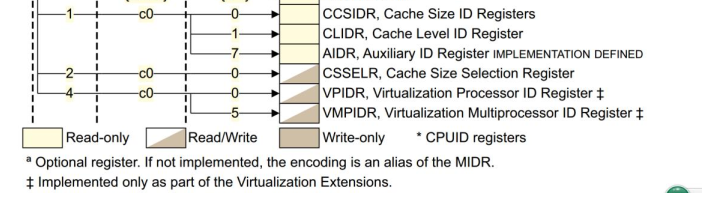

c0 寄存器

CP15 协处理器有 16 个 32 位寄存器, c0~c15,在使用 MRC 或者 MCR 指令访问这 16 个寄存器的时候,指令中的 CRn、 opc1、 CRm 和 opc2 通过不同的搭配,其得到的寄存器含义是不同的。

MRC/MCR 指令中的 CRn=c0, opc1=0, CRm=c0, opc2=0 的时候就表示此时的 c0 就是 MIDR 寄存器,也就是主 ID 寄存器,这个也是 c0 的基本作用。对于 Cortex-A7内核来说, c0 作为 MDIR 寄存器的时候其含义如图

bit31:24:厂商编号, 0X41, ARM。

bit23:20:内核架构的主版本号, ARM 内核版本一般使用 rnpn 来表示,比如 r0p1,其中 r0后面的 0 就是内核架构主版本号。

bit19:16:架构代码, 0XF, ARMv7 架构。

bit15:4:内核版本号, 0XC07, Cortex-A7 MPCore 内核。

bit3:0:内核架构的次版本号, rnpn 中的 pn,比如 r0p1 中 p1 后面的 1 就是次版本号。

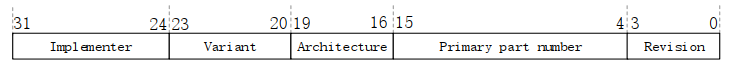

c1 寄存器

MRC/MCR 指令中的 CRn=c1, opc1=0, CRm=c0, opc2=0 的时候就表示此时的 c1 就是 SCTLR 寄存器,也就是系统控制寄存器,这个是 c1 的基本作用。 SCTLR 寄存器主要是完成控制功能的,比如使能或者禁止 MMU、 I/D Cache 等, c1 作为 SCTLR 寄存器的时候其含义如图

SCTLR 的位比较多,我们就只看本章会用到的几个位:

bit13: V , 中断向量表基地址选择位,为 0 的话中断向量表基地址为 0X00000000,软件可以使用 VBAR 来重映射此基地址,也就是中断向量表重定位。为 1 的话中断向量表基地址为

0XFFFF0000,此基地址不能被重映射。

bit12: I, I Cache 使能位,为 0 的话关闭 I Cache,为 1 的话使能 I Cache。

bit11: Z,分支预测使能位,如果开启 MMU 的话,此为也会使能。

bit10: SW, SWP 和 SWPB 使能位,当为 0 的话关闭 SWP 和 SWPB 指令,当为 1 的时候就使能 SWP 和 SWPB 指令。

bit9:3:未使用,保留。

bit2: C, D Cache 和缓存一致性使能位,为 0 的时候禁止 D Cache 和缓存一致性,为 1 时使能。

bit1: A,内存对齐检查使能位,为 0 的时候关闭内存对齐检查,为 1 的时候使能内存对齐检查。

bit0: M, MMU 使能位,为 0 的时候禁止 MMU,为 1 的时候使能 MMU。如果要读写 SCTLR 的话,就可以使用如下命令:

MRC p15, 0, , c1, c0, 0 ;读取 SCTLR 寄存器,数据保存到 Rt 中。

MCR p15, 0, , c1, c0, 0 ;将 Rt 中的数据写到 SCTLR(c1)寄存器中。

c12 寄存器

当 MRC/MCR 指令中的 CRn=c12, opc1=0, CRm=c0, opc2=0 的时候就表示此时 c12 为 VBAR 寄存器,也就是向量表基地址寄存器。设置中断向量表偏移的时候就需要将新的中断向量表基地址写入 VBAR 中,比如在前面的例程中,代码链接的起始地址为0X87800000,而中断向量表肯定要放到最前面,也就是 0X87800000 这个地址处。所以就需要设置 VBAR 为 0X87800000,设置命令如下:

ldr r0, =0X87800000 ; r0=0X87800000

MCR p15, 0, r0, c12, c0, 0 ;将 r0 里面的数据写入到 c12 中,即 c12=0X87800000

c15 寄存器

在图 17.1.4.5 中,我们需要 c15 作为 CBAR 寄存器,因为 GIC 的基地址就保存在 CBAR中,我们可以通过如下命令获取到 GIC 基地址:MRC p15, 4, r1, c15, c0, 0 ; 获取 GIC 基础地址,基地址保存在 r1 中。获取到 GIC 基地址以后就可以设置 GIC 相关寄存器了,比如我们可以读取当前中断 ID,当前中断 ID 保存在 GICC_IAR 中,寄存器 GICC_IAR 属于 CPU 接口端寄存器,寄存器地址相对于 CPU 接口端起始地址的偏移为 0XC,因此获取当前中断 ID 的代码如下:

MRC p15, 4, r1, c15, c0, 0 ;获取 GIC 基地址

ADD r1, r1, #0X2000 ;GIC 基地址加 0X2000 得到 CPU 接口端寄存器起始地址

LDR r0, [r1, #0XC] ;读取 CPU 接口端起始地址+0XC 处的寄存器值,也就是寄存器GIC_IAR 的值

关于 CP15 协处理器就讲解到这里,简单总结一下,通过 c0 寄存器可以获取到处理器内核信息;通过 c1 寄存器可以使能或禁止 MMU、 I/D Cache 等;通过 c12 寄存器可以设置中断向量偏移;通过 c15 寄存器可以获取 GIC 基地址。关于 CP15 的其他寄存器,大家自行查阅本节前面列举的 2 份 ARM 官方资料。

2453

2453

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?