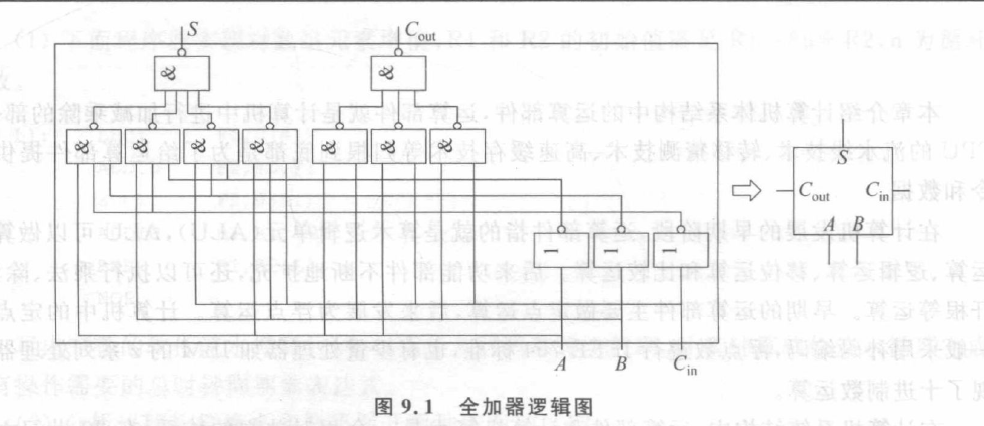

1. 一位全加器

输入:cin, A, B

输出:co sum

真值表

逻辑表达式

sum = cin ^ A ^ B

co = A&B | A&Cin | B&Cin

注意:sum的时延几乎是carray时延的两倍

电路图

因此全加器的输出需要2、3级门延迟

2. 多位全加器

2.1 串行进位加法器

把多个全加器串链起来就形成了串行进位加法器,串行进位加法器将低位全加器的进位输出Cout作为本级全加器的进位输入Cin,因此在计算最高位的进位输出时(进位输出当作两级门延时),有32级门延时,这对CPU提高主频来说,关键路径的门延时太长了。

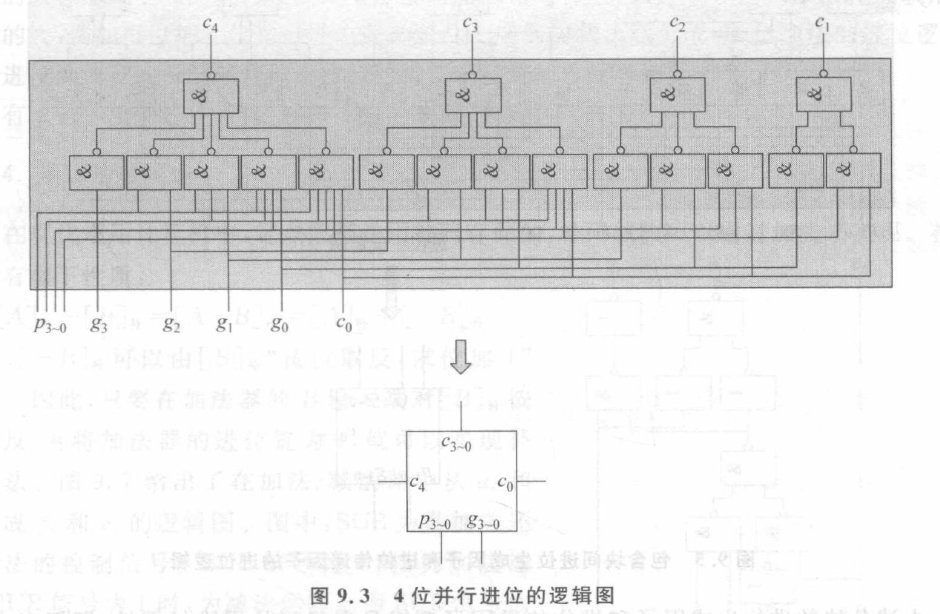

2.2 超前进位加法器

通过并行计算每一位的进位,使得进位结果的输出只与输入有关,而与前一位的进位无关,简单来说就是列出真值表,直接求出组合逻辑表达式,缺点是输出的扇入过大,需要用到许多多输入门。

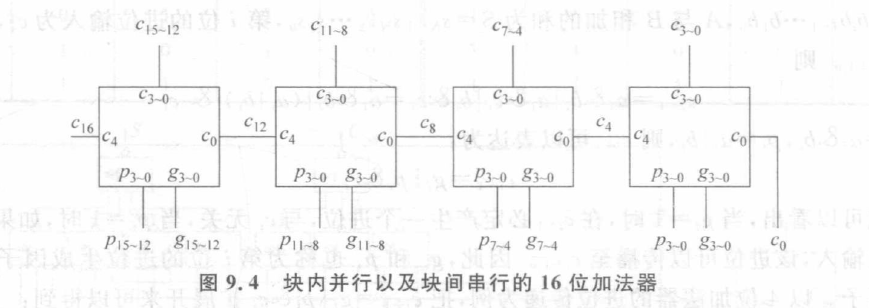

2.3 块内并行,块间串行16位加法器

块内并行,最高位输出只需要2个门延时,块间串行,因此16位加法器需要8个门延时。

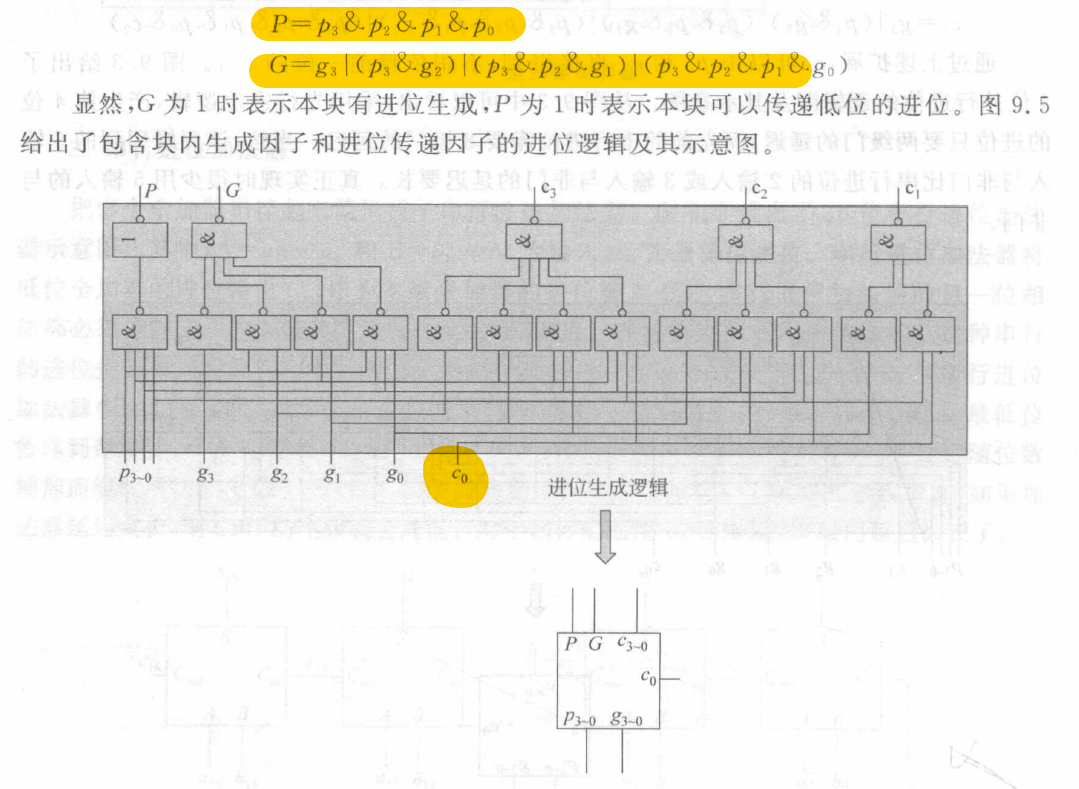

2.4 块内并行,块间并行

注意P, G的生成与c0无关,因此P G生成需要2个门延迟,之后加上c0,生成c4需要2个门延时,c4作为第2个c0,生成c7-4需要两个门延时,因此需要6个门延时,加上p3-0和g3-0需要两个门,总共需要8个门延时。

3. 减法器

在现代通用计算机中,定点数都是用补码存储的,补码减法可以通过加法来实现,补码的运算性质如下

因此我们只需要根据B的补码,求得-B的补码,然后进行加法运算就可以了。因此只需要进行按位取反,然后加1就可以实现补码减法。在实现时,我们对c0进行选择,如果为加法,c0=0;如果为减法,c0=1;

4. 溢出判断

- 对于加法,如果两个正数相加结果为负,或者两个负数相加,结果为正,则发生溢出;对于减法运算,如果整数减负数结果为负数,或者负数减正数结果为正数,则发生溢出,因此运算器的溢出判断条件为

因为运算部件中,溢出判断逻辑在加减法结果的基础上生成,因此溢出判断是运算部件的关键路径。 - 比较器可以通过减法实现,如果减法没有发生溢出,且结果符号位为1,则A<B;如果有发生溢出,则结果符号位为0时A<B;

2207

2207

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?