spi主机端代码

fpga verilog 实现 注释齐全

ID:4715618774471120

是有点难度

SPI(Serial Peripheral Interface)是一种常见的串行通信协议,用于连接主机和外设。在本文中,我们将重点讨论在FPGA中使用Verilog语言实现SPI主机端代码,并且注释齐全的重要性。

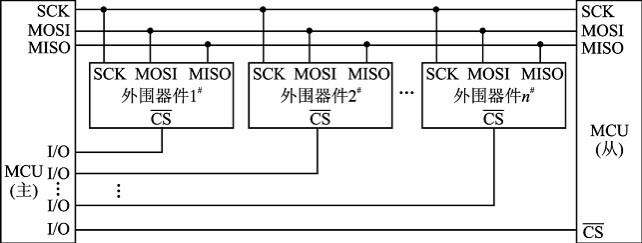

首先,让我们来了解SPI协议的基本原理。SPI协议由四条信号线组成,包括主机输出数据(MOSI)、主机输入数据(MISO)、时钟(SCK)和片选(SS)。主机通过时钟信号控制数据的传输速率,并通过片选信号选择与其通信的外设。主机通过MOSI将数据发送给外设,并通过MISO接收外设发送的数据。因此,在FPGA中实现SPI主机端代码,需要针对这些信号进行逻辑设计和时序控制。

在Verilog语言中,我们可以使用模块化的方式来实现SPI主机端代码。首先,我们可以定义一个主机模块,其中包含输入输出信号和控制逻辑。主机模块可以接收来自外设的数据,并且根据需要将数据发送给外设。同时,主机模块需要根据时钟信号进行数据的同步和时序控制,以确保数据的准确传输和接收。

在设计主机模块时,注释的齐全性非常重要。注释可以提供对代码的解释和说明,方便其他开发人员阅读和理解代码逻辑。在SPI主机端代码中,注释应该包括对每个模块和信号的功能说明、时序要求以及与外设的通信协议说明。通过注释的齐全性,可以提高代码的可维护性和可读性。

为了实现注释的齐全性,我们可以将注释写在每个模块和信号定义的前面,以说明其作用和功能。此外,我们还可以在代码的关键部分添加注释,以解释代码实现的具体逻辑和细节。注释的内容应该简洁明了,不要使用过于晦涩的技术术语,以确保其他开发人员可以轻松理解和使用代码。

除了注释的齐全性,代码的结构也需要清晰有序。合理的代码结构可以提高代码的可读性和可维护性。在SPI主机端代码中,我们可以按照功能和模块进行划分,将相关的代码放在同一个模块中。例如,可以定义一个时钟模块,用于产生时钟信号和时序控制;定义一个数据传输模块,用于处理数据的发送和接收;定义一个片选模块,用于选择与主机通信的外设。通过合理的代码结构,可以使代码逻辑更加清晰,易于理解和修改。

总结而言,本文围绕SPI主机端代码的实现以及注释的齐全性展开了讨论。在FPGA中使用Verilog语言实现SPI主机端代码时,需要考虑时序控制和逻辑设计。同时,注释的齐全性和代码结构的清晰性也是编写高质量代码的重要因素。通过合理地设计和注释代码,我们可以实现高效可靠的SPI主机端代码,并提高代码的可维护性和可读性。

相关代码 程序地址:http://nodep.cn/618774471120.html

188

188

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?