一,缓存结构

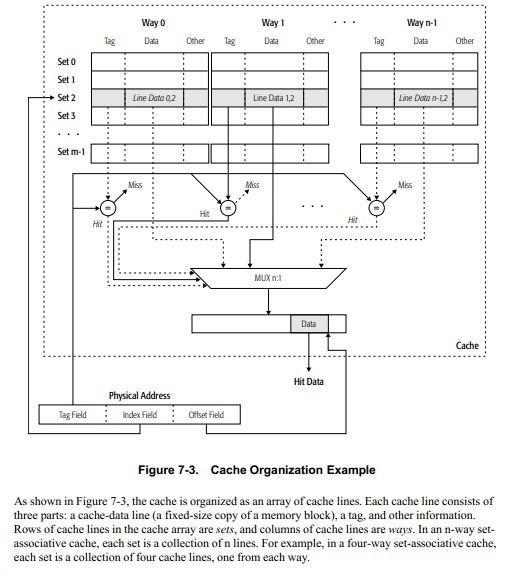

下图为一个n-way set-associative cache 结构图:

缓存组织为cache line数组的形式,每一个cache line由三部分组成,内存数据,tag,其他信息。

多个cache line一行,组成一个set,一列cache line为way,在n-way set-associative cache中,每个set由n个cache line

组成,例如一个4-way set-associative cache,每个set由4个cache line组成,每个way一个cache line。

二,缓存索引

通过物理地址获取数据或指令在缓存中的位置(set, way, byte),每个物理地址被分为三部分:

Index,选择缓存的行(set),同一行中的所有cache line通过index域选择。

tag,选择一行(set)中特定的cache line,物理地址的tag域与每个cache line的tag域进行比较,如果匹配,则发出cache hit信号

,选择此cache line,否则发出cache miss信号。

offset,物理地址在cache line中的第一个byte,数据或指令从此byte的位置读取。

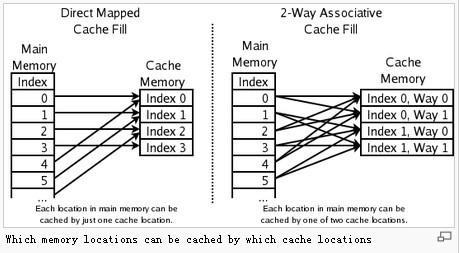

三,fully associative cache、direct-mapped scheme和set-associative scheme

direct mapped, if each entry in main memory can go in just one place in the cache, the cache is .

fully associative, If the replacement policy is free to choose any entry in the cache to hold the copy.

N-way set associative, Many caches implement a compromise in which each entry in main memory can go to any one of N places in the cache.

因此2-way set associative意味着,主存中的任意一个entry在缓存中有两个可以保存的位置。

参考:

AMD64 Architecture Programmer’s Manual Volume 2: System Programming

735

735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?