定义

m序列是最长线性反馈移位寄存器序列的简称。它是由带线性反馈的移存器产生的周期最长的序列。一般来说,一个n级线性反馈移存器可能产生的最长周期等于(2^n -1)。

m序列是一种典型的伪随机序列。在通信领域有着广泛的应用,如扩频通信、卫星通信的码分多址(CDMA),数字数据中的加密、加扰、同步、误码率测量等领域。

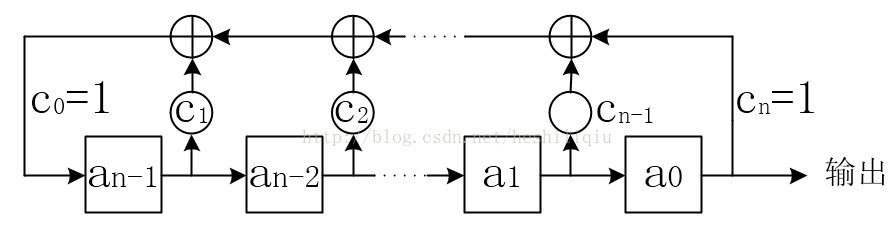

线性反馈移位寄存器原理方框图

与产生m序列有关的3个方程

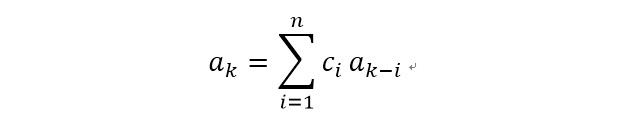

1)递推方程

它给出了状态ak和前面n个状态的关系。

2)特征方程(又叫特征方程式)

它决定了移存器的反馈连接和序列的结构。式中x^i仅指明其系数(1或0)代表ci的值,x本身的取值并无实际意义。

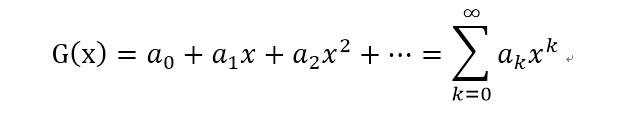

3)母函数

它表示反馈移存器的输出序列{ak}。

本原多项式

若一个n次多项式f(x)满足下列条件:

1)f(x)为既约的;

2)f(x)可整除(x^m +1),m=2^n -1;

3)f(x)除不尽(x^q +1),q<m;

则称f(x)为本原多项式。

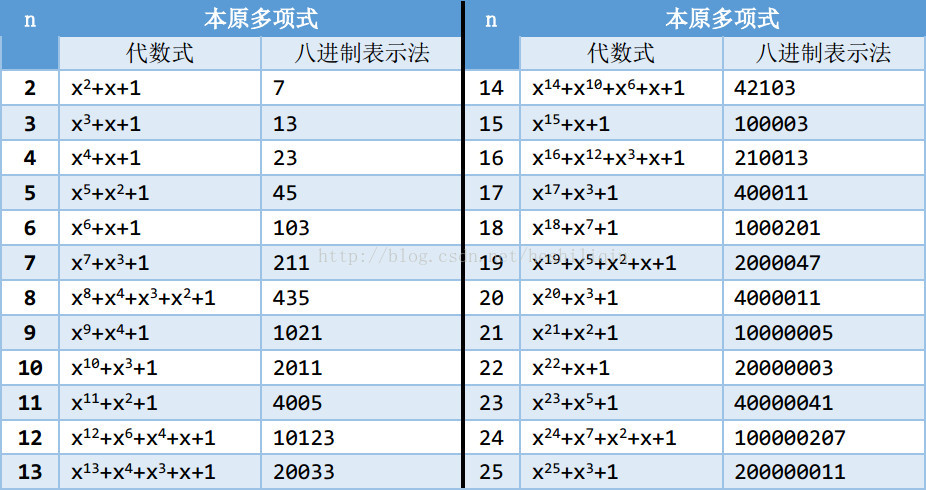

为什么要理解本原多项式?因为一个线性反馈移存器能产生m序列的充要条件:反馈移存器的特征多项式为本原多项式。常用的本原多项式由查表得到。

本原多项式表

verilog实现及仿真

m_sequence.v(以x8+x4+x3+x2+1为例) tips:代码实现依据原理方框图和特征多项式。

<span style="font-size:14px;">module m_sequence(

-

input sclk, -

input rst_n, -

output wire m_seq -

); -

parameter POLY = 8'b10001110;//由本原多项式得到 -

reg [7:0] shift_reg; -

always@(posedge sclk or negedge rst_n) -

begin -

if(rst_n == 0)begin -

shift_reg <= 8'b11111111;//初值不可为全零 -

end -

else begin -

shift_reg[7] <= (shift_reg[0] & POLY[7])^ -

(shift_reg[1] & POLY[6])^ -

(shift_reg[2] & POLY[5])^ -

(shift_reg[3] & POLY[4])^ -

(shift_reg[4] & POLY[3])^ -

(shift_reg[5] & POLY[2])^ -

(shift_reg[6] & POLY[1])^ -

(shift_reg[7] & POLY[0]); -

shift_reg[6:0] <= shift_reg[7:1]; -

end -

end -

assign m_seq = shift_reg[0]; -

endmodule</span>

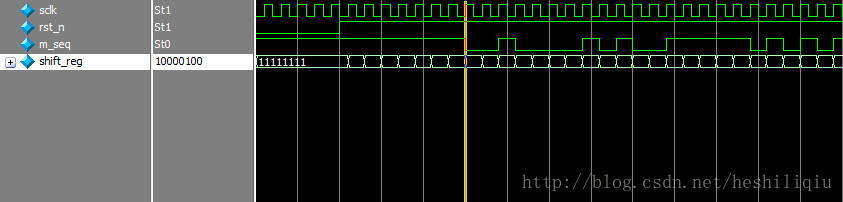

仿真截图:

注:从图中黄线处开始得到新值,黄线前面是初始化的值。

7839

7839

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?