一、Vivado将模块封装为IP的方法(网表文件)

在给别人用自己的工程时可以封装IP,Vivado用封装IP的工具,可以得到像xilinx的ip一样的可以配置参数的IP核,但是用其他工程调用后发现还是能看到源文件,如何将工程源文件加密,暂时没有找到方法,如果知道还请赐教。

而直接用.edif网表文件作为ip的方法如下:

1、建立工程设置顶层模块

将需要封装的模块设置为顶层模块。(shift_bus模块)

2、综合待封装模块

vivado综合时会默认将输入输出端口添加buffer缓存,而封装的模块大多都是用在一个大的模块的内部,综合不能添加iobuf,在ISE的综合选项中有-iobuf选项而在Vivado中该选项是隐藏的,可以在综合设置窗口的Options下面最后一项 More Options一栏写入“-no_iobuf”,然后综合即可。

3、生成.edif网表文件

打开综合后的设计:在Flow Navigator中点击“Open Synthesis Deisgn”

在TCL Console中输入:“write_edif /path/xx.edif” 。特别注意:路径分隔字符为“/”(得到的网表文件为shift_bus.edif)

4、建立wrapper

建立一个与待封装模块同名的.v文件,该文件只描述该模块的接口。(shift_bus.v)

5、调用

将shift_bus.v和shift_bus.edif文件添加到需要调用的工程中,然后直接对shift_bus模块进行例化即可。

在vivado中使用( read_edif 路径/xxx.ngc)读入网表文件到工程中,添加只包含端口信息的文件

二、【划水】Vivado生成网表文件是怎么回事呢?

https://zhuanlan.zhihu.com/p/137433454

四、vivado下将rtl模块做成网表加入工程使用

在fpga开发过程中,往往是模块化的分工合作,大家做好自己的模块再统一添加到顶层。

rtl代码是透明,当你不想公开自己的代码而只想提供一个黑盒子时,就需要想别的办法。

xilinx vivado提供IP封装的功能,但是不能提供加密,所以可行的办法是提供网表来供顶层使用。

模块的网标生成需要注意三个问题:

1、将模块作为顶层综合时,端口会被工具认作是I/O而添加IO BUF;

2、端口的很多信号由于没有驱动所以会被工具优化掉;

3、xilinx工具无法确定网表使用者是否有IP核的licence,所以制作网表的rtl内不能包含xilinx的IP核。

以上问题都能想办法规避,

1、IO BUF可以不用管,工具会将不是顶层模块的端口的IO BUF优化掉,当然你也可以自己去删;

2、在模块的端口添加(KEEP = “TRUE”),保证信号不被优化;

3、一定需要用到xilinx的IP核的话就将IP核作为你的模块的一个平行模块。

网标的生成也很简单,将模块作为顶层综合后,路径下会有checkpoint,而该文件会包含顶层例化的.v和.vhd、网表.edf.。将该文件加入工程替代.v或.vhd即可。

五、在Vivado下利用Tcl编辑综合后的网表

http://www.iot-online.com/jishuwenku/2017/0602/69596.html

七、VIVADO网表文件DCP,edf

为了便于模块化设计,同时保护自己的知识产权,Xilinx VIVADO 提供两种代码封装方法:DCP文件和edf文件。

DCP文件生成方法:

1、将需要生成DCP的模块设置为顶层,打开综合设置,在more option中填入 -mode out_of_context,删除所有约束文件(约束文件会被封装在DCP中,并且优先级最高),开始综合;

2、综合完成后在runs\synth_1文件夹下可找到DCP文件,但该DCP文件在实际使用中会有诸多限制,如模块内部有IP核或其他DCP文件,则可能出现错误,如何实现DCP嵌套IP可参照以下步骤;

3、DCP嵌套,为了保证DCP嵌套后能正常被调用综合,在第1步中在综合前可将所有IP核设置为globle模式,在完成综合后打开综合设计,在TCL命令框中输入:write_checkpoint -force D:/x/xxx.dcp,其中xxx为模块名称,这样就可以生成完整的dcp文件。

EDF(网表)文件生成方法:

1、将需要生成DCP的模块设置为顶层,打开综合设置,在more option中填入 -mode out_of_context,删除所有约束文件,开始综合;

2、在完成综合后打开综合设计,在TCL命令框中输入:write_edif D:/x/xxx.edf生成edf文件,输入write_verilog -mode synth_stub D:/x/xxx_stub.edf生成黑盒接口文件,应为edf文件不像DCP文件,可以单独被调用,edf文件必须配合.v的黑盒接口才能被调用;

3、关于设计模块内包含IP核或edf的设计,不建议使用edf封装,很可能报IP错误,若实在需要使用,可在TCL命令框中输入:write_edif -force D:/x/xxx.edf生成edf文件,可一定程度上减少报错,但不能保证。

DCP和edf比较:

1、DCP文件对软件版本及其敏感,高版本软件生成的DCP无法在低版本软件使用;

2、采用一定手段,DCP可实现IP、DCP嵌套,但EDF实现嵌套的能力较弱。

九、write_edif

EDF文件可以直接导入Vivado,而无需Verilog源文件。

好处:

(1) 避免沙雕队友修改源代码,则可以直接提交EDF网表文件。

(2) 避免用户剽窃劳动成果,保护自己的知识产权。

(3) 对于无需更改的设计复用,直接用EDF网表会贼方便。

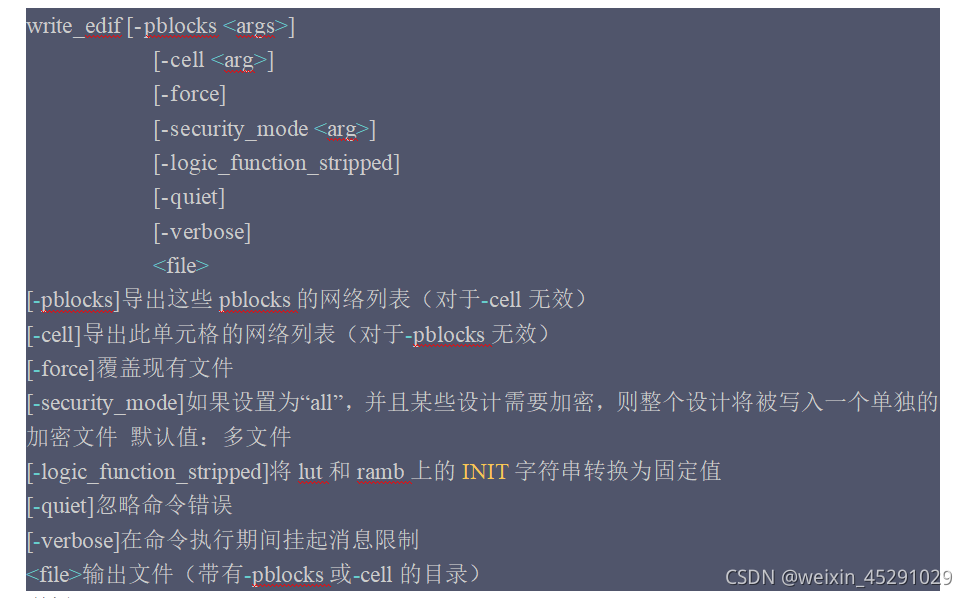

1 vivado write_edif

目的:将当前网络列表导出为EDIF文件。

语法:

举例:

write_edif C:/Data/edifOut.edn 将整个设计的EDIF网表文件写入指定的文件名

write_edif -pblocks [get_pblocks] C:/Data/FPGA_Design/ 获取输出设计中所有Pblock的EDIF网表。这些文件将被写入指定的目录。

Pblocks:手工布局的本质是对指定逻辑单元设定面积约束,在Vivado下就是对其画一个Pblock。Pblock的大小限定了该逻辑单元所能使用的FPGA资源;Pblock的位置限定了该逻辑单元在FPGA中的位置;Pblock中所包含的FPGA资源类型限定了该逻辑单元所能使用的资源。

2 操作步骤

(1)将需要封装的模块设置为顶层模块

(2)综合或实现需要生成edif的verilog或vhdl源文件。

(3)open Elaborated Design or Open Synthesized Design or Open Implemented Design

(4) tcl console:write_edif xx.edf

(5) tcl console:write_verilog -mode synth_stub xx_stub.v

(6) 调用 xx.edf和xx_stub.v

3752

3752

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?