1 介绍

在控制系统工程和信号处理领域,“Unit Delay”、"Memory"以及"代数环"是一些常用的概念,下面对它们进行简要解释:

① Unit Delay(单位延迟)

“Unit Delay” 是一个用于表示系统或信号处理中的离散时间延迟的元件。在离散时间系统中,输入信号通过一个单位延迟后变为输出信号。这个延迟一般表示一个采样周期的时间。在模型中,通常使用z^-1表示单位延迟,其中z是单位圆上的复数。Unit Delay在离散时间系统的差分方程中很常见,特别是在数字滤波器和控制系统的离散化中。

② Memory(存储器)

在控制系统中,“Memory” 或 “State” 表示系统的内部状态或存储信息。控制系统的动态行为可以由这些状态来描述。在状态空间表示中,系统的状态通过微分方程或差分方程进行描述,而这些方程中的状态就是系统的内部存储。“Memory” 可以是连续时间系统的积分状态或者是离散时间系统的过去时刻的状态值。

③ 代数环

"代数环"是代数结构的一个概念,它是一个集合,配备了两个二元运算(通常是加法和乘法),并且满足一些特定的性质。一个代数环必须满足以下几个条件:

-

封闭性:对于环中的任意两个元素进行加法和乘法运算的结果仍然在这个环中。

-

结合律:加法和乘法运算在环中是结合的。

-

分配律:乘法对于加法具有分配律。

代数环可以进一步分类,例如,如果环中的乘法满足交换律,则称为交换环。环的一个特例是域,它是一个具有更多性质的代数结构,包括乘法的可逆性。

2 区分

Unit Delay 是一个用于在离散时间系统中引入单位时间延迟的元件。它简单地将输入信号延迟一个采样周期,对应于离散系统中的时间步长。

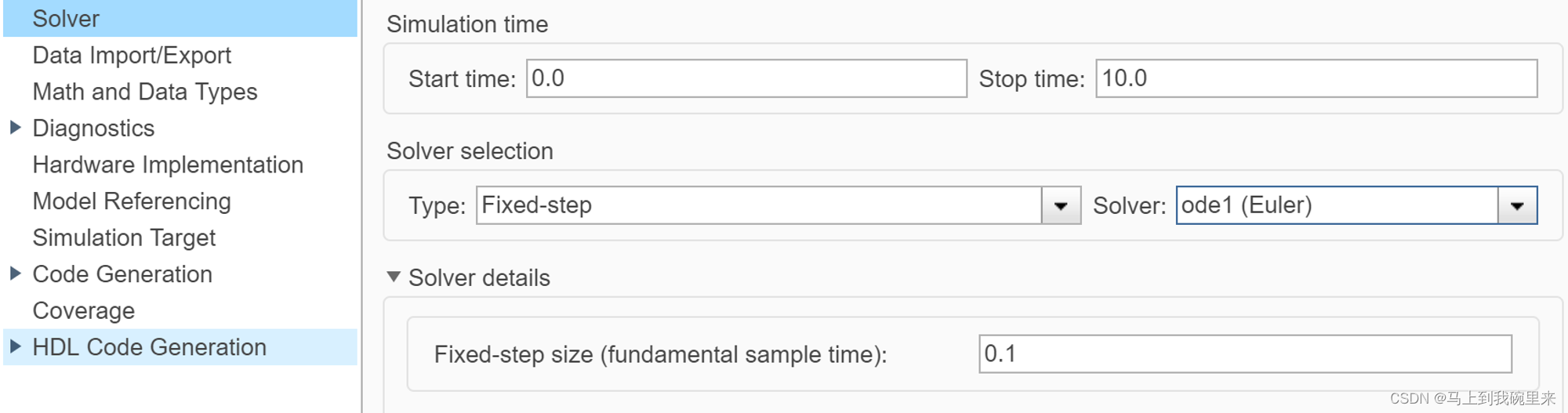

Memory Block 也是一个用于延迟信号的元件。在使用离散求解器时,它可以延迟仿真步长;而在连续求解器中,它涉及到主步长(major step)和次步长(minor step)的概念。主步长可以被视为整个仿真过程的主要时间步长,而次步长则是在主步长内仿真器采用的更小步长,以确保仿真的准确性。

Memory Block 可以被用于逼近连续微分运算,通过存储和处理信号的历史信息来实现微分的逼近。描述中提到的使用 Memory Block 连接时钟和时钟信号本身来计算步长和信号的增量,并通过两者相除得到微分,需要注意这种方法可能存在一些复杂性和限制,建议在具体应用中小心使用。

关于提到的 “最好不要用 memory block 来消除代数环” 的建议,这是因为在某些情况下,使用 Memory Block 打破代数环可能导致数值求解的稳定性问题。因此,推荐使用其他方法来处理代数环,例如代数环破坏器(Algebraic Loop Breaker)。

When the Memory block inherits a discrete sample time, the block is analogous to the Unit Delay block. However, the Memory block does not support state logging. If logging the final state is necessary, use a Unit Delay block instead.

This is documented in the reference page for the memory block.

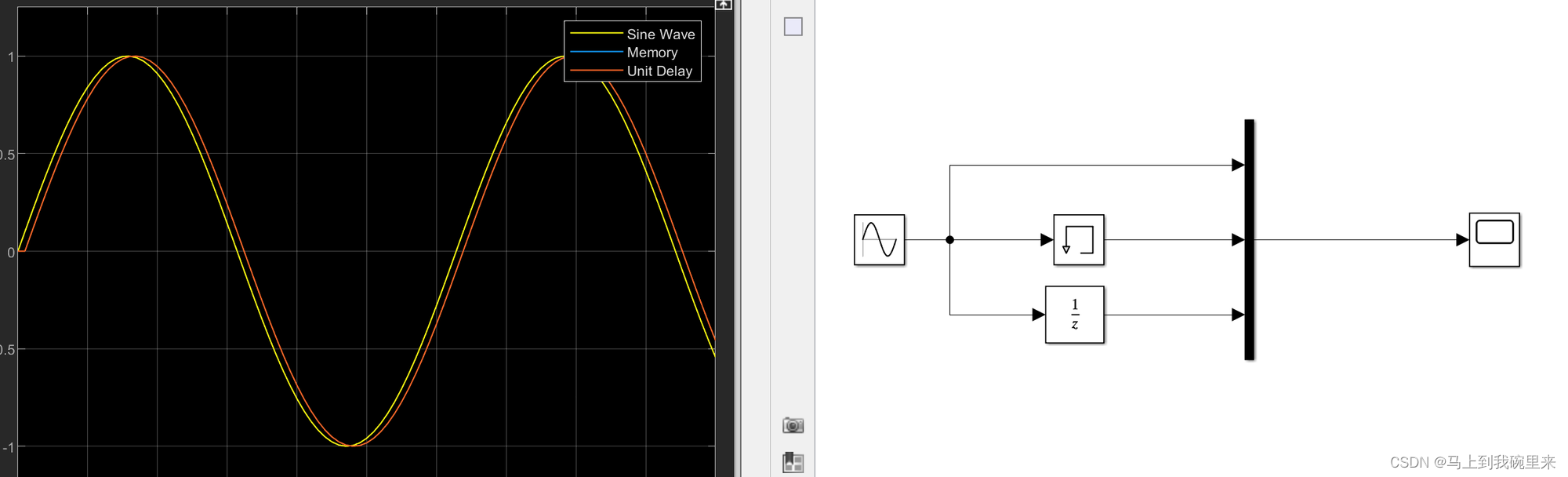

3 仿真验证

看到蓝橙线重合,这里说明离散下效果基本一致

2918

2918

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?