PLL锁相环,CMOS模拟集成电路设计,模拟ic设计, PLL锁相环设计,PLL学习资料,非常适合初学者,包含有veriloga模型和testbench电路和仿真设计文档,非常详细和全面,能够快速上手。

ID:23500754376909003

imxxok

PLL锁相环(Phase Locked Loop)是一种常用的电路设计技术,特别是在CMOS模拟集成电路设计中。本文将围绕PLL锁相环的设计展开讨论,旨在为初学者提供详细和全面的学习资料,包括veriloga模型、testbench电路和仿真设计文档,以便快速上手。

在介绍PLL锁相环之前,我们先简要了解一下CMOS模拟集成电路设计的基本原理和概念。CMOS模拟集成电路是指采用互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor)技术制造的集成电路。它具有低功耗、高噪声容限以及可靠性高等优点,因此在现代电子产品设计中得到广泛应用。

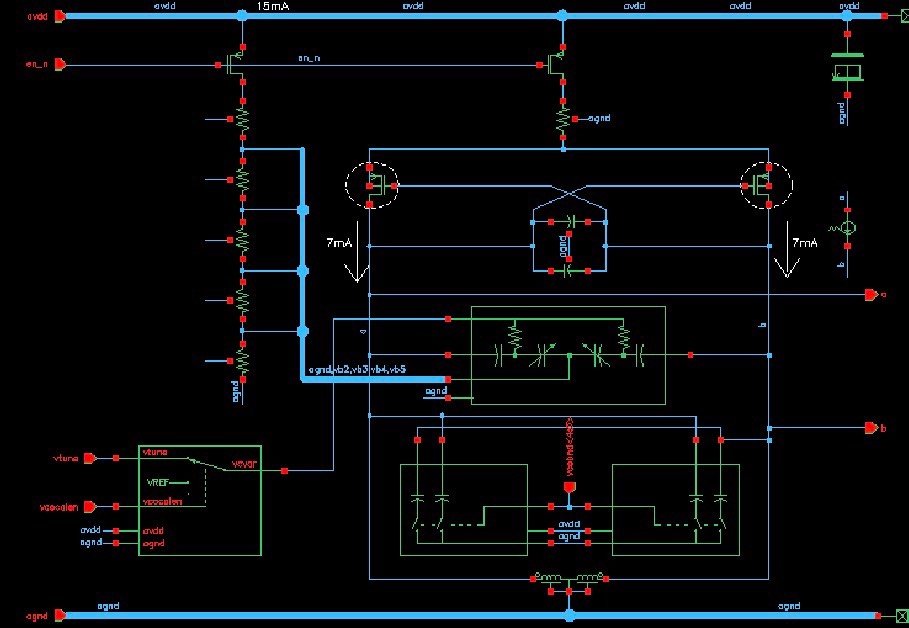

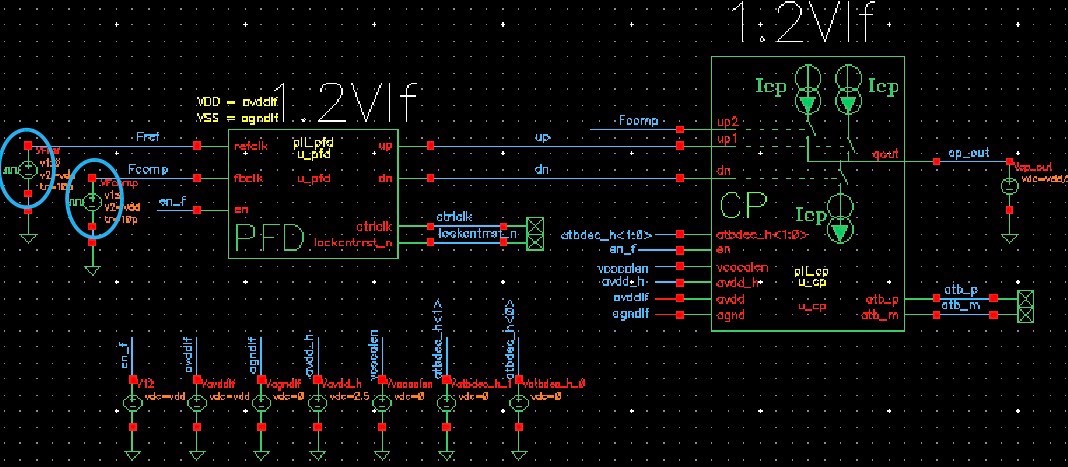

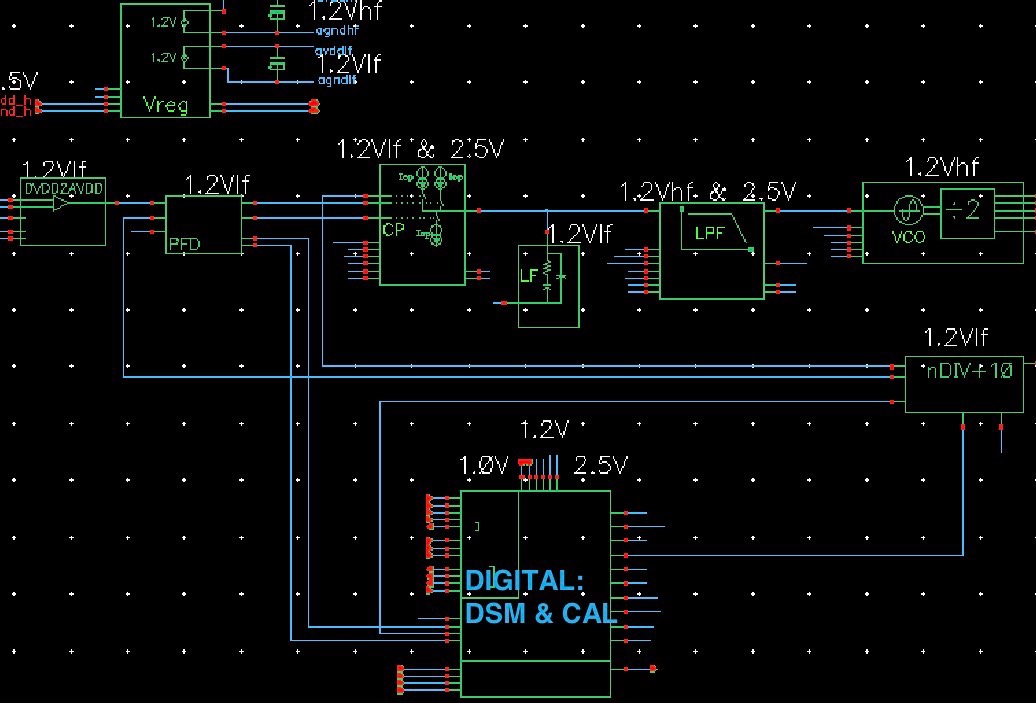

PLL锁相环是一种闭环反馈控制系统,其主要作用是通过比较输入信号和参考信号的相位差来生成稳定的输出信号。它由相频比较器、环路滤波器、VCO(Voltage-Controlled Oscillator)等组成。其中,相频比较器用于比较输入信号和参考信号的相位差,并产生误差信号;环路滤波器用于滤波和放大误差信号;VCO则是一个电压控制的振荡器,其频率受到环路滤波器输出的控制。

PLL锁相环的设计中,需要考虑多个关键参数和指标。首先,我们需要确定参考信号的频率范围和要求。其次,需要选择合适的VCO设定电压范围,并进行合理的偏置设置。此外,相频比较器的设计也需要根据具体的应用需求进行优化。对于CMOS模拟集成电路设计而言,还需要考虑功耗、噪声和抗干扰等因素。

针对初学者而言,我们提供了详细的学习资料,包括veriloga模型和testbench电路。Veriloga是一种硬件描述语言,可以用于建模和仿真电路。通过Veriloga模型,初学者可以更好地理解PLL锁相环的工作原理,并通过仿真结果验证设计的正确性。而testbench电路则是用于验证和测试Veriloga模型的电路,包含了丰富的测试用例和仿真设计文档,使初学者能够快速上手。

在实际的PLL锁相环设计中,还需要考虑一些实用技巧和注意事项。例如,如何根据具体的应用场景选择合适的参考信号和频率范围;如何优化VCO的线性度和噪声性能;如何进行合理的电源抗干扰设计等。这些方面的知识和技巧需要通过实践和经验积累来掌握,初学者可以通过阅读相关文献和参考资料来进一步深入学习。

总之,本文围绕PLL锁相环的设计展开了详细的讨论,并提供了Veriloga模型、testbench电路和仿真设计文档等学习资料,非常适合初学者快速上手。在实际的CMOS模拟集成电路设计中,PLL锁相环是一项重要的技术,通过合理的设计和优化,可以实现更好的性能和稳定性。希望本文能为读者提供有益的参考和指导,促进技术的发展和应用。

以上相关代码,程序地址:http://fansik.cn/754376909003.html

705

705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?