本文以SAR ADC为例,主要介绍在ADC在常见应用电路中,如何提升采样精度。

1.常见ADC类型

针对常见ADC功耗、面积、结构、 设计难度等方面,对各种高速ADC架构进行了分析比对,罗列了在不同的应用领域常见ADC类型,如表1.1所示:

表1.1 不同ADC对比

| 优点 | 缺点 | 性能 | 应用 | |

| 全并行ADC | 速度快 | 功耗高,面积大 | 高速,低精度 | 网络通讯 |

| 折叠内插式ADC | 速度快,无需反馈环路 | 需大量电阻,面积大,功耗高 | 高速,低精度 | 雷达 |

| 逐次逼近型ADC | 低功耗,结构简单 | 需比较多次 | 高速,中精度 | 光纤通信 |

| 两步式ADC | 速度快 | DAC精度设计难度大 | 高速,中精度 | 电磁存储 |

| 流水线ADC | 速度快,精度高,数字校准方便 | 级间增益运放设计难度大,功耗高,面积大 | 高速,高精度 | 无线通信 |

| 流水线SAR ADC | 速度快,精度高 | 功耗高,面积大,不适应低压设计 | 高速,高精度 | 无线通信 |

经过上述表格的对比,不难发现逐次逼近型(SAR)ADC由于具有结构简单、模拟模块更少、 面积更小、功耗更低,且数字输出不存在延迟等优点,占据着重要的地位。但SAR ADC一般采样速率在2K-3M sps,因此本文将针对高速SAR ADC如何在保证采样精度的前提下,进一步提升采样速率进行研究,以使得其更好地应用在更高速、更高精度的应用系统中。

2.SAR_ADC原理

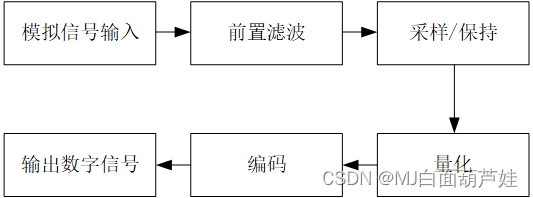

ADC 基本工作流程如下图所示,尽管有不同结构的 ADC 电路,但是,基本原理都可以归纳为滤波、采样/保持、量化、编码。前置滤波的作用,是为了防止高频信号混叠到 ADC 基带内,产生干扰所设置的,通常由 ADC 自身带宽来限制。采样电路是通过采样时钟,对进行滤波后传递进来的模拟信号进行采样,将连续的模拟信号转换成离散的数字信号;保持电路则是用来确保采样值在量化期间不随量化过程的进行发生改变,保证量化的精度。从 ADC 生成采样信号起,到输出相应二进制数字信号为止,这段时间叫做 ADC 的转换时间。转换时间就取决于量化和编码的速度。

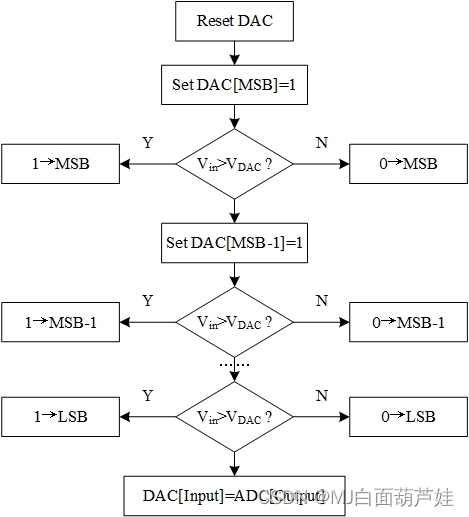

SAR ADC的特点是功耗低,结构简单,具有中高精度分辨率,常用于工业或移动设备中。传统的SAR ADC架构为同步时钟控制,主要由采样保持电路,DAC阵列,高速比较器,SAR逻辑和输出寄存器等模块组成。量化算法流程如下图所示。量化采用串行方式进行,从最高位MSB开始 进行比较,先将需要比较的位置MSB置1,比较Vin与VDAC的大小,若Vin大,MSB置1,反之置0。完成一次比较后存储比较结果于寄存器中。以此类推,权重 随着位数逐位降低,N次比较完成后,完成量化过程。由于一次循环只比较一次, 所以只需一个比较器,通过多个时钟周期循环进行,中间结果的模拟部分由DAC储存,数字部分由寄存器储存,两者同时进行,最终输出结果。

3.SAR_ADC结构

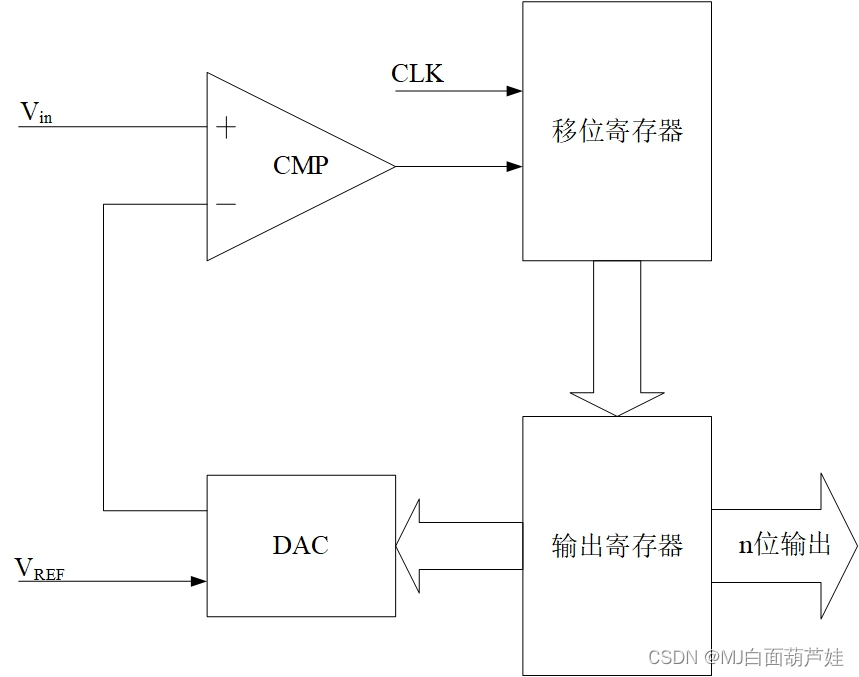

SAR ADC是通过一个DAC产生一个模拟信号,通过自高向低位逐级逼近输入信号的办法来得到与输入信号对应的数字编码,下图为一个典型SAR ADC结构图。这种ADC中包含一个比较器,一个DAC和数字控制逻辑。 数字控制逻辑通过比较器自高向低逐位判断输入信号对应的二进制编码来控制DAC输出。它的模数转换过程如下:首先将输入模拟信号与数摸转换器的输出进行 比较,比较结果(大于为1,小于为0)即作为一位输出,同时由其决定下一周期数摸转换器的输出,每完成一次比较,SARADC 就由高到低完成一位数字量的转换, 利用类似牛顿二分法的算法,在N个周期就可完成 N位精度的模数转换。SAR ADC的速度主要受DAC的建立时间、比较器的速度及控制逻辑的开关时间决定,其功 率损耗随采样速率而变化,这由其结构决定的。而且这种结构的ADC由于只需要 一个比较器就可以完成整个转换过程,因而在面积和功耗上占有极大的优势。

4.ADC的阻抗匹配

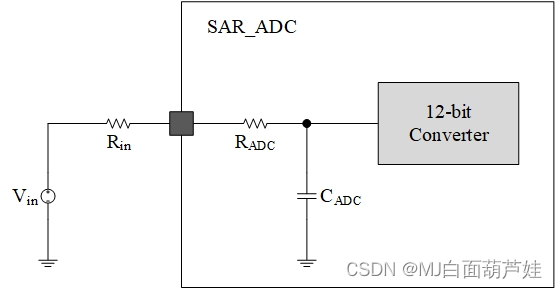

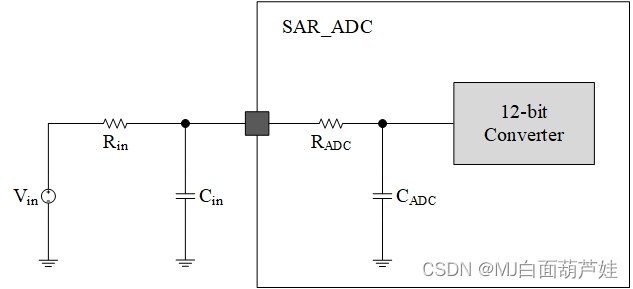

下图为SAR ADC外部电路与内部采用模块的结构示意图,其中为外部输入电阻,

为SAR ADC内的采样电阻,

为采样电容。输入信号

经过外部输入电阻进入SAR ADC并对

进行充电,最终将

的保存的电荷送入12 bit的转换器,完成进一步的转换输出。

对充电的时间需满足下式:

其中为时间常数,代表给

充满电的快慢;

为采样周期。

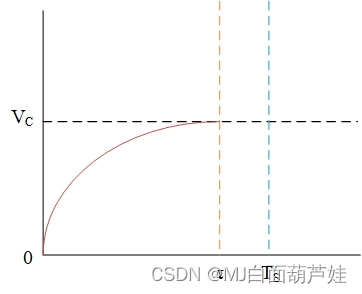

由下图可以看出,中的存储的电荷由0到

,需消耗时间

,若ADC在

存储完成后,采样此时的电压值,可得到与输入电压一致的转换值,即ADC的采样周期

需大于

。在采样周期或采样速率不变的前提下,增加采样精度,可减小

值,即减小R和C。若

和

在模拟电路设计中已经确定不好更改,此时可减小外部输入电阻

。

因此在保证采样精度的条件下,的最大取值在不同采样周期下是不同的,下面以STM32G431系列为例,ADC最大输入阻抗与采样周期之间的关系见下表,这里仅截取了其中3个采样周期。如在ADC时钟频率为60 MHz下,采用2.5T的采用周期,则对于快速通道(Fast channels)而言外部Rin最大为100 Ω。

| Sampling cycle@60 MHz | Sampling time (ns) | Rin max (Ω) | |

| Fast channels | Slow channels | ||

| 2.5 | 41.67 | 100 | N/A |

| 6.5 | 108.33 | 330 | 100 |

| 12.5 | 208.33 | 680 | 470 |

通常还会在输入电阻旁外接个接地电容,如下图所示,以进一步提升采样精度,该电容作用为存储电荷,和与

组成低通滤波。ADC的采样和转化其实就是ADC内部电容的快速充放电,快速充放电的时候,这个电容可以快速给ADC补给电荷,否则ADC的采样值会有振荡,如果在信号源上并联电容,相当于进一步减少了信号源的内阻。

5.ADC应用电路

5.1分压电路采样

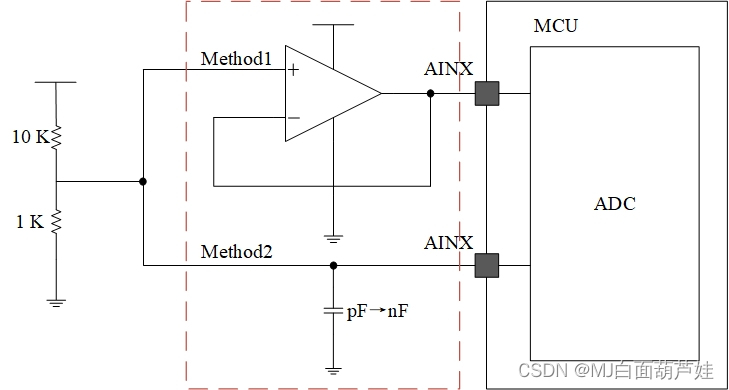

在ADC采样的应用中,通常会外接一个分压电路,来将拟采样信号电压控制在0-VREF之间。特别在电机控制系统的应用中尤为常见,通常采用10 KΩ/1 KΩ的分压比,如下图所示。之所以选用1 KΩ的电阻,这是为了避免有较大的电流流入地,造成功耗的浪费,但如此大的电阻并不能较好地适配于ADC采用,如第4节中提到STM32G431系列中输入电阻在4M采样率中最大仅为100 Ω。因此我们可将滤波电容提升到1-20 nF,以期减少ADC的输入阻抗,或者在分压电路后加入电压跟随器进行阻抗匹配(电压跟随器输入阻抗可达到几兆欧姆,输出阻抗为几欧姆甚至更小)。

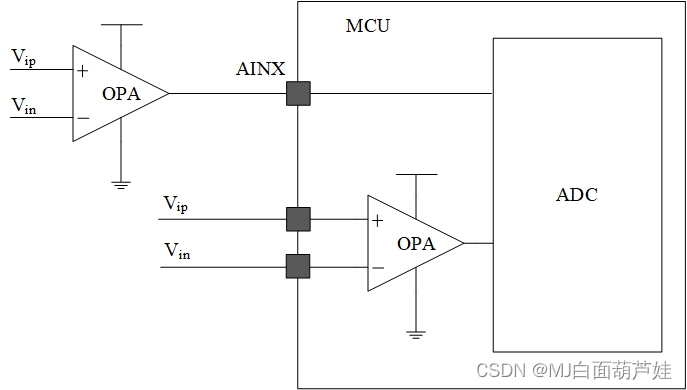

5.2电流采样

在ADC中另一个常见的应用就是电流采样,以防止电流过大损坏芯片。通常需要OPA或PGA将较小的电流信号转换为电压信号并送到ADC中进行采样。有些MCU芯片内有搭载OPA,在芯片内已经有连线将OPA的输出送至ADC的输入端,若MCU内没有OPA,则需在芯片外自建OPA放大电路,如下图所示。

5.2.1内置OPA/PGA电流采样

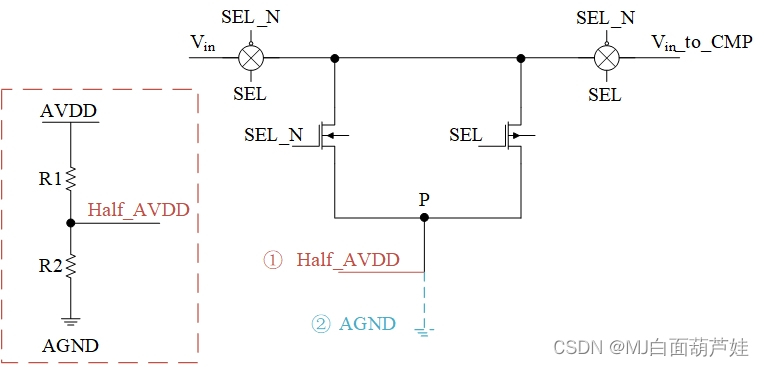

虽然内置OPA,直接输出到ADC,可避免外界诸多干扰,但由于OPA需有高增益,因此其输出阻抗很大,影响ADC的采样精度。因为在芯片内,不可加nF量级的电容,因此可在ADC输入通道前加buffer,以减小ADC的输入阻抗,但因面积和成本的考量,可在ADC输入通道上加下图所示结构,目的是将ADC通道上的初始时刻电压抬升到1/2的模拟电源电压(AVDD),以减小信号恢复时间,增加采样精度。

在初始时刻,SEL为低电平,SEL_N为高电平,输入信号不能传输进ADC中的比较器,此时该通道内电压接到P点,通常接地(AGND)。若AVDD通过电阻分压后,能将1/2的AVDD接到P点,那么此时SEL为高电平,SEL_N为低电平,通道电压将不再由0 V到

,而是由1/2的AVDD到

。

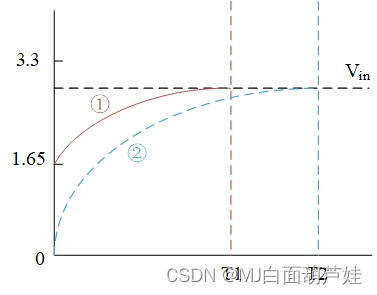

例如,现输入电压为3 V,AVDD等于参考电压(VREF)为3.3 V,若P点接地,如下图蓝色表示,若P点接到1/2的AVDD,由红色表示。由图红色曲线可以看出,输入通道电压达到

的时间更短,在相同采样周期内,更容易采样到稳定的输入电压。

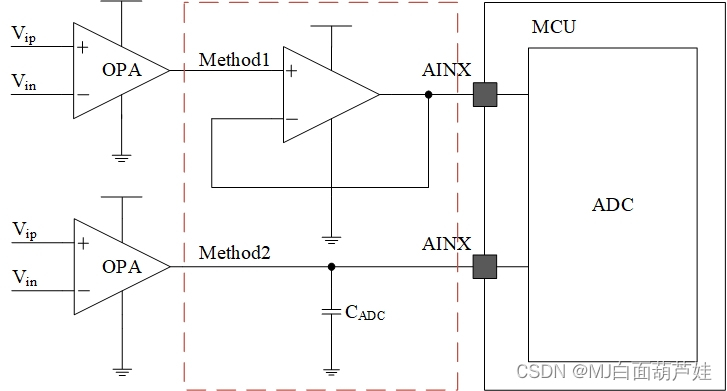

5.2.2外置OPA/PGA电流采样

对于外置OPA进行电流采样,有两种方法提升采样精度,如下图所示。

方法1:在OPA输出和ADC输入之间,加一电压跟随器,以减小ADC的输入阻抗。因为电压跟随器具有具有高输入阻抗,低输出阻抗的优点。输入阻抗很大时,跟随器相当于和前级电路断路,和自恢复保险丝原理一样,通过高阻抗断开电源电路。电压跟随器输出阻抗很低,相当于和后级电路短路。后级电路的输入电压值,等于电压跟随器输出端的电压值。

方法2:在OPA输出和ADC输入之间,外接一接地的电容(nF量级),这个电容可以快速给ADC补给电荷,等效于与输入信号源并联,相当于进一步减少了信号源的内阻。

6.ADC的串扰

串扰描述的是两条或多条信号线产生的耦合现象。对其他线产生影响的线叫作侵略线aggressor net,被其它线所影响的线叫作victim net。由于耦合可能会影响victim net的transition time甚至逻辑值。

在ADC中串扰问题常发生于多输入通道之间,即ADC采样时,前一个通道的采样结果会对后一个通道造成影响,从而导致后一个通道采样结果的误差增大,影响ADC的精度和稳定性。这种串扰问题主要是因为ADC模块的输入阻抗较低,导致输入信号在通道之间相互影响所致。

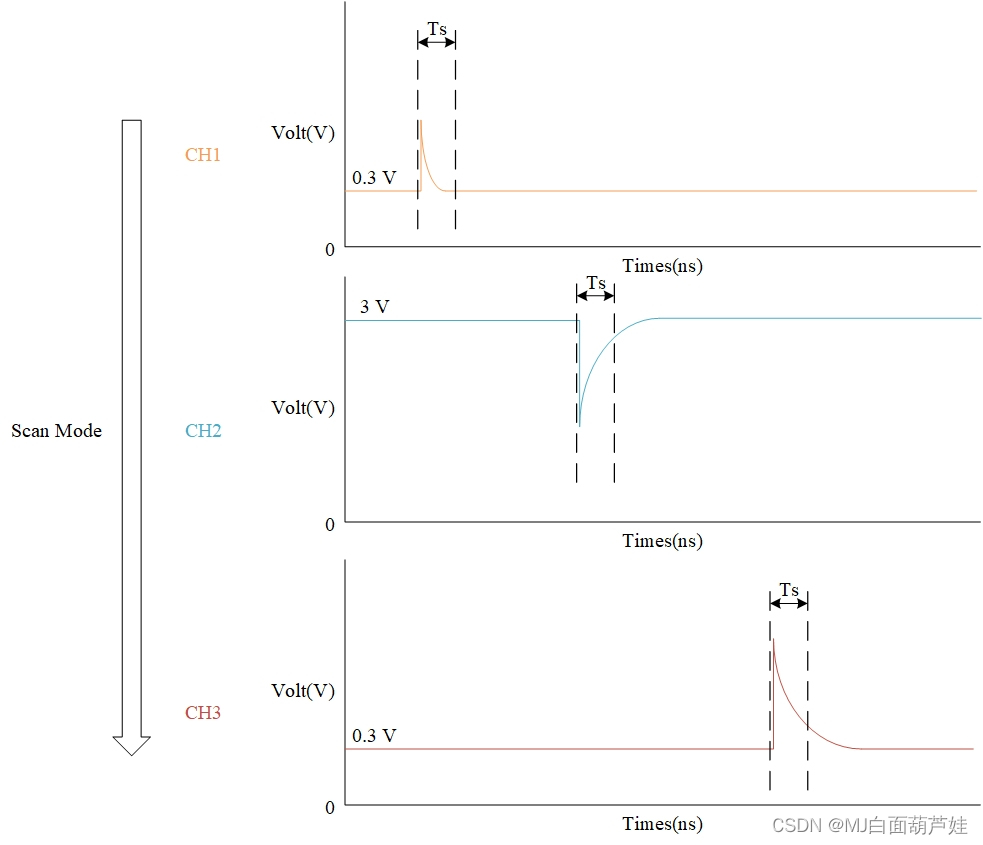

如图X所示,在扫描模式(Scan Model)下,依此采样CH1、CH2和CH,均使用相同的采样周期Ts,其中CH1的输入电压为0.3 V,CH2的输入电压为3 V,CH3的输入电压为0.3 V。由于前一个通道输入电压小于CH2输入电压,因此在采样CH2时,输入电压会有向下的尖峰。尖峰高度取决于前一通道输入电压与现采样通道输入电压的差值,

越大,则尖峰越大,反之尖峰越小。

尖峰的大小影响采样精度,由图X可以看出,采样CH2和CH3时,由于尖峰较高,在信号还未恢复到正常电压时,已经完成采样,因此此时ADC采样到的值大于或小于输入电压。值得注意的是,采样CH1时,其采样尖峰向上,且较小,这是由于该通道为第一个采样通道,初始电压未知,因此其尖峰可能向上可能向下,尖峰大小也较随机。

为解决串扰问题,可采样的方式如下:

1.适当增加采样时间;

2.降低ADC输入阻抗,虽然降低输入阻抗会增加串扰问题,但可加快信号恢复时间,以增加采样精度;

3.采用差分输入模式,差分输入模式可以有效地抵消掉共模干扰,提高ADC的精度和稳定性;

4.采用外部滤波器,在输入信号进入芯片前,可以通过使用外部滤波器来滤除掉信号中的噪声和干扰,从而减少通道间串扰的影响,

5.适当调整通道顺序:在多个ADC通道输入时,可以适当调整通道顺序,将相互影响较大的通道隔开,从而减少串扰的影响。

1642

1642

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?