1. NMOS采样开关

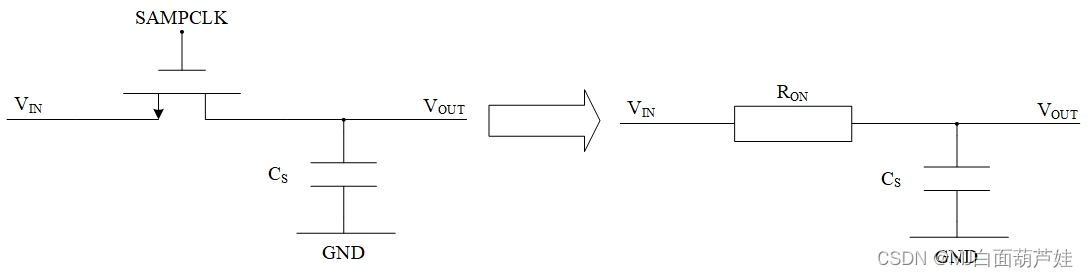

采样开关时完成采样的关键,其精度决定系统精度的上限。理想的采样开关,从断开到闭合与闭合到断开时间应该均为0。 但此为理想情况,一般通过采样时钟信号来控制工作在线性区的MOS管的开关来控制采样。如下图所示,当采样时钟SAMPCLK为高电平时,NMOS管导通,VOUT处于跟随状态;当SAMPCLK为低电平时,NMOS管关断,VOUT处于保持状态。

由于NMOS 管存在一定的导通电阻 Ron,如上图所示,会和采样电容 Cs 形成一阶RC网络,直接影响着采样开关的速度和精度。其次,只有当NMOS管的栅源电压大于其阈值电压时,即Vgs>Vthn时,NMOS管才会导通。当二者电压值相近时,NMOS管则无法完全导通,从而导致采样开关的导通电阻非常大,造成该RC网络存在较大的延时,使采样开关的速度变慢,最终影响采样电路的性能。而且用单个NMOS管传输信号时,由于阈值电压Vthn的存在,其输出无法达到满摆幅。当CLKs为高电平Vdd时,NMOS采样开关的导通电阻为

可以看出,Ron随输入电压的增加而增加,当输入电压接近Vdd时,Ron显著增加,且NMOS管无法采样大于Vdd-Vthn的输入信号;同样PMOS无法采样小于|Vthp|的输入信号。

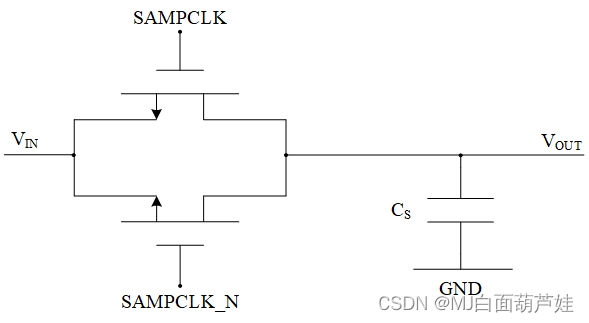

2.CMOS采样开关

因此选择CMOS管作为开关,如下图所示,可达到全摆幅采样,此时导通电阻为

若,此时等效导通电阻与输入信号无关,但由于工艺问题,无法满足,故采样精度不高,一般只用于量化精度低于6位的ADC。

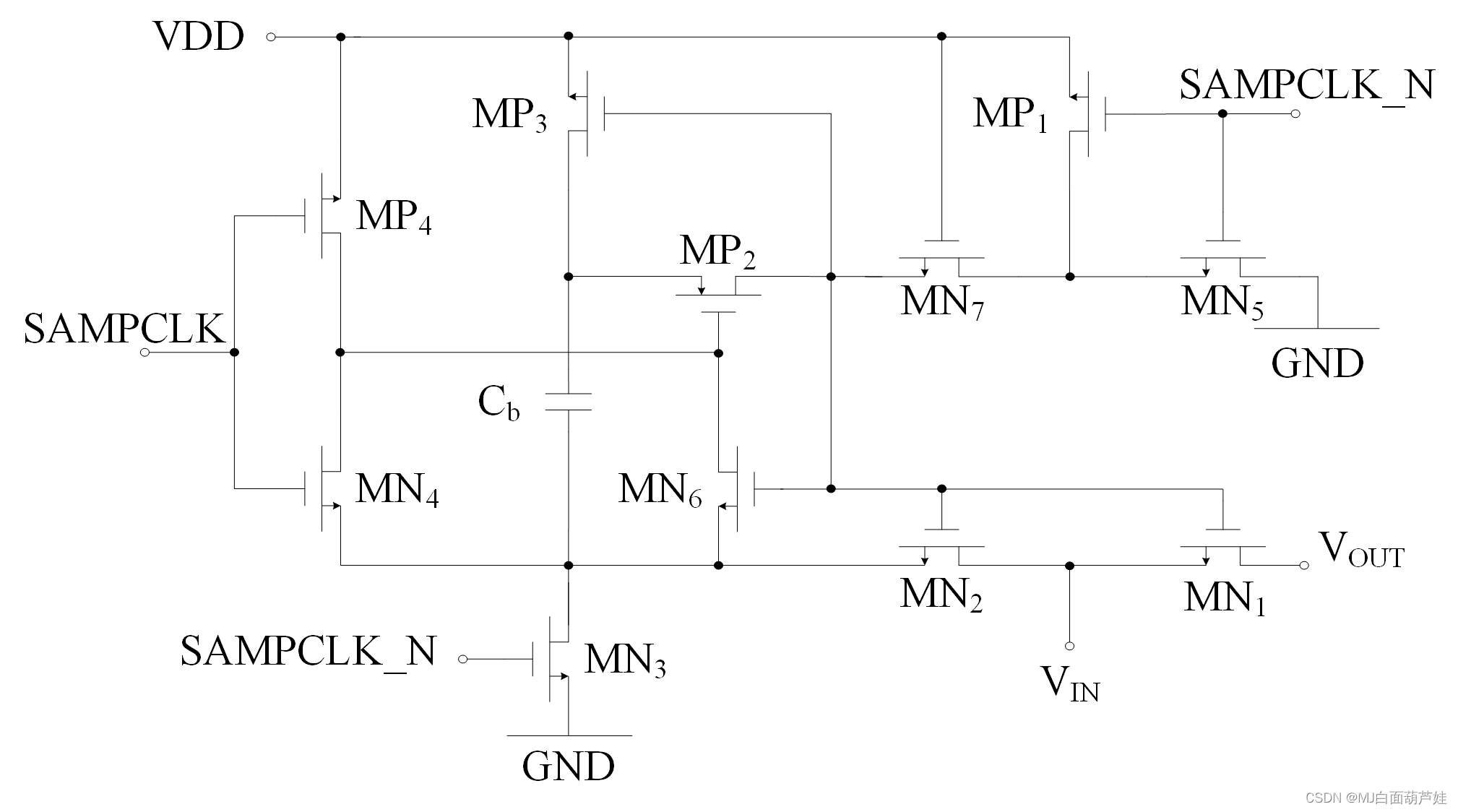

3.栅压自举开关

在高精度采样时,常采样栅压自举开关作为采样器,如下图所示,可使用较小尺寸MOS管实现对采样电容的充放电,且可维持开关管MN1的的Vgs不变,得到恒定的Ron。

当SAMPCLK为0,SAMPCLK_N为1时(保持阶段):MN5、MN7为导通,开关管MN1栅极接地,MN1关断;MN3、MP3导通,Cb上下级板分别接VDD和GND,Cb充电至VDD。

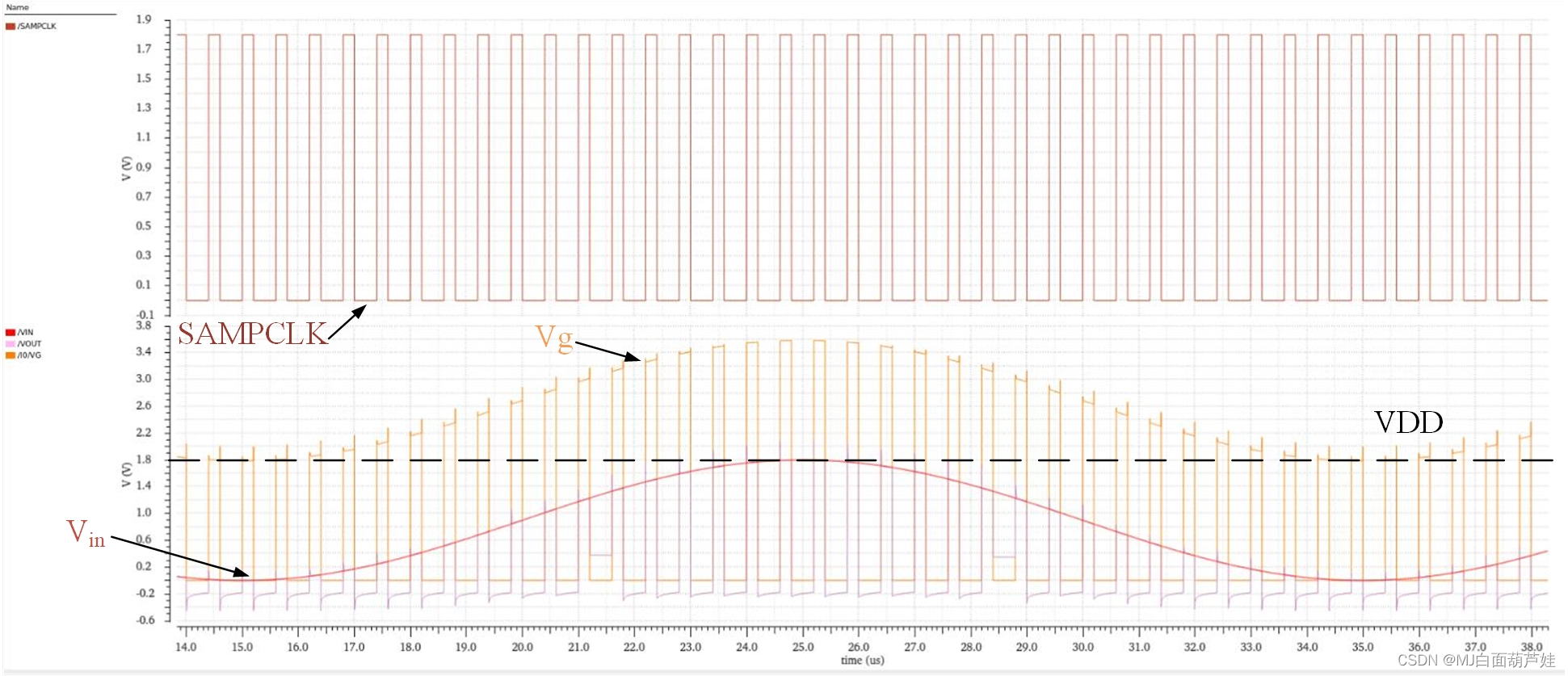

当SAMPCLK为1,SAMPCLK_N为0时(采样阶段):MP3、MN3关断,MP2导通,将VDD传至Cb,电容上级板电压不变,同时MN1、MN2导通,将MN1的源极于Cb下级板相连,由于电荷守恒,此时开关MN1的Vgs维持在VDD,栅极电压被举到Vgs1+VDD,采样开关MN1的Vg与输入电压Vin的波形如下图所示。

8936

8936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?