极好锁相环电路,fractional -N PLL,2.4G用于蓝牙

英文文档加工程文件和PDK

小数分频锁相环

1、用来参考PLL芯片设计,进阶使用最佳,也可用来入门了解

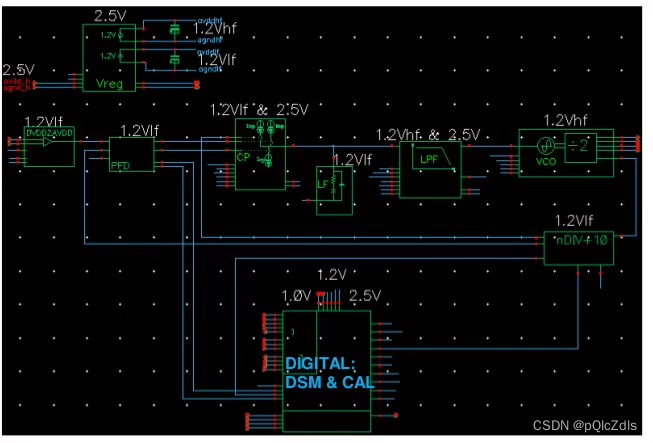

2、原理图系统完整,没版图,但有关键处版图的dummy提示

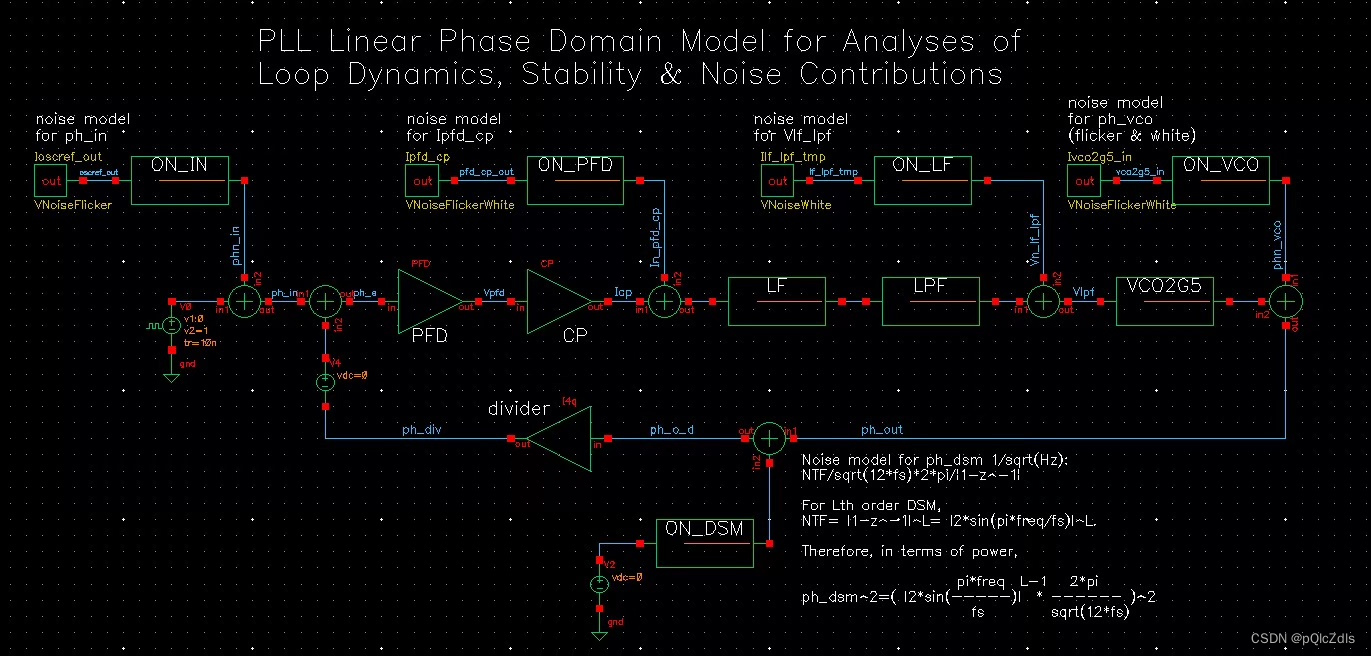

3、有PLL相位裕模型,分析环路动态稳定性和噪声贡献

4、67页英文文档,介绍部分电路的使用方法

5、有源三阶环路滤波器,电阻有trimming电路设计

注意需要有图六的软件

极好锁相环电路,fractional -N PLL,2.4G用于蓝牙的英文文档加工程文件和PDK中的小数分频锁相环是一种用于参考PLL芯片设计的电路。它不仅适用于进阶使用,还可以作为入门了解PLL芯片设计的工具。

该文档包含了完整的原理图系统,尽管没有版图,但提供了关键处版图的dummy提示。这对于工程师们在进行芯片设计时非常有用,因为他们可以根据dummy提示来进行关键处的版图设计。

值得注意的是,该文档中还提供了PLL相位裕模型,用于分析环路动态稳定性和噪声贡献。这对于设计者来说是非常重要的,因为它能够帮助他们评估锁相环的性能并进行必要的优化。

整个文档共有67页,以英文形式呈现。它详细介绍了部分电路的使用方法,对于初学者来说是非常实用的参考资料。

此外,该文档还特别提到了有源三阶环路滤波器的设计。这个环路滤波器中的电阻还包含了trimming电路,这为工程师们提供了调节电阻的灵活性。

需要注意的是,在使用该文档时需要有图六的软件。这个软件是必需的,因为它与文档的内容密切相关,并提供了必要的工具和环境,使工程师们能够更好地理解和应用文档中的内容。

总的来说,这份英文文档加工程文件和PDK提供了对极好锁相环电路、fractional -N PLL和2.4G蓝牙的全面介绍。它不仅适用于专业工程师,还可以作为初学者了解PLL芯片设计的入门参考。内容丰富而详细,涵盖了电路设计、环路动态稳定性分析、噪声贡献评估等多个方面,是一篇非常实用的技术分析文章。

相关代码,程序地址:http://imgcs.cn/lanzoun/747689595852.html

本文档详细介绍了极好锁相环电路和fractional-NPLL在2.4G蓝牙应用中的设计,提供完整原理图、PLL相位裕模型和环路滤波器设计,适合进阶和初学者学习PLL芯片设计。

本文档详细介绍了极好锁相环电路和fractional-NPLL在2.4G蓝牙应用中的设计,提供完整原理图、PLL相位裕模型和环路滤波器设计,适合进阶和初学者学习PLL芯片设计。

331

331

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?