提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

UVM 实战

代码清单2-2

14-15行,while循环不能进入

一、UVM 实战 2.2.1 代码修改

while(!top_tb.rst_n)

@(posedge top_tb.clk);

//作者的意图是rst_n跳变为1之前,阻塞住task

实际的仿真,并不能进入while循环。

原因是:rst_n初始值为x,赋值为0的时候,while循环被跳过去了。

经老师傅指导,在while之前加入一个延迟#0

#0

while(!top_tb.rst_n)

@(posedge top_tb.clk);

等待rst_n赋值完成。

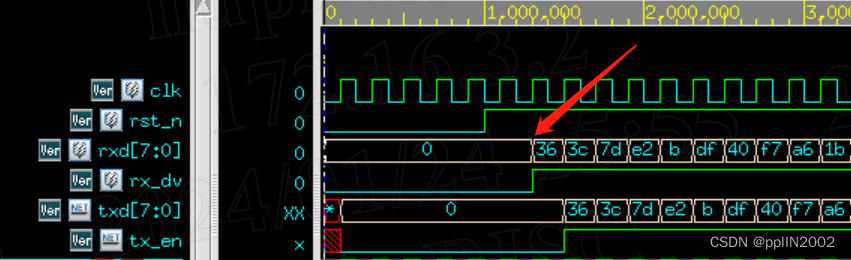

二、成功后的波形图

如下图,红色箭头标识处,可以看到rxd在rst_n跳变为1之后发送数据,而不是从0时刻开始咔哧咔哧乱发了。

总结

这其实是个time slot调度的问题。rst_n 在赋值为0之前,while读到的是 x。

详细原理请参考:

1、绿宝书(SystemVerilog验证, 测试平台编写指南),4.3.5 程序块和时序区域(Timing Region),P76。

2、http://lihuaxi.xjx100.cn/news/1309694.html,详解SystemVerilog中time slot的调度。

3867

3867

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?