可选的DMA控制器

MUSBMHDRC 可以选择包含一个多通道 DMA 控制器,最多可配置 8 个通道。

此 DMA 控制器支持两种 DMA 模式,称为 DMA 模式 0 和 1,它可以处理最大 8k 的数据包大小(用于与第 8.4.1.4 和 8.4 节中描述的 Tx 批量数据包拆分、Rx 批量数据包组合选项结合使用.2.4)

此外,控制器可以编程为使用 INCR4、INCR8 和 INCR16 4/8/16 节拍递增突发而不是未指定长度的突发进行传输。

在 DMA 模式 0 下运行时,DMA 控制器只能被编程为加载/卸载一个数据包,因此通过 USB 传输的每个数据包都需要处理器干预。同步或中断事务(即包括端点 0)。

在 DMA 模式 1 下运行时,可以对 DMA 控制器进行编程以加载/卸载完整的批量传输(可以

是许多数据包)。一旦设置,DMA 控制器将加载/卸载传输的所有数据包,仅在传输完成时中断处理器。DMA 模式 1 只能与使用批量事务的端点一起使用。

每个通道都可以针对选定的操作模式进行独立编程。

DMA总线周期

DMA 控制器在 AHB 上使用递增突发。当它第一次被授予总线控制权时(无论是在 USB 数据包开始时,还是在数据包中途被丢弃后重新获得总线时),它开始一个新的突发。 AHB 地址开始一个新的 1K 字节块 注意:在 1K 边界开始新突发的要求由 DMA 控制器自动处理。

这些突发可能是 4-beat、8-beat、16-beat 或未指定的长度,具体取决于 DMA 通道的编程方式、正在传输的数据包的大小以及相对于下一个 1K 边界的位置。位 D10–9 CNTL 寄存器选择 Burst Mode 0 – 3 依次定义可以使用的突发类型(参见上面的 17.1 节)。例如,选择 Burst Mode 2 允许使用 8-beat (INCR8)、4-beat (INCR4 ) 突发和未指定长度的突发,但不是 16 拍 (INCR16) 突发。

在 DMA 模式 0 或 DMA 模式 1 中为传输选择的突发模式没有限制。

数据包的每次传输通常使用字传输(32 位)进行,但在数据包传输结束时可能会有额外的字节或半字传输。由于起始地址(写入 DMA ADDR (n) 寄存器)必须是字对齐的,数据包传输将从字传输开始,但可以在末尾添加半字和/或字节传输以处理任何残留物。支持 AHB 拆分事务和重试。

BUS ERRORS

如果在 DMA 控制器访问 AHB 上的存储器时发生总线错误,则 DMA 控制器将立即终止 DMA 传输并用 CNTL 寄存器的总线错误 (D8) 位设置中断处理器。

注意:该中断的产生不受 DMA CNTL 寄存器(位 3)中中断允许位的设置的影响。

当 CNTL.D3 = 0 时仍会产生中断。

传输包

使用内置 DMA 控制器访问 MUSBMHDRC FIFO 需要对 DMA 控制器和 MUSBMHDRC 端点进行适当编程。可以有多种变化。以下部分详细介绍了用于传输单个数据包的基本操作的标准设置和多个数据包。

单个数据包:RX ENDPOINT

单个数据包的传输通常使用 DMA 模式 0 进行。

为此,应按如下方式对 MUSBMHDRC Rx 端点进行编程:

IntrRxE 寄存器中的相关中断使能位设置为 1。

相应的 RxCSR 寄存器的 DMAReqEnab 位 (D13) 设置为 0。(注意:无需设置 MUSBMHDRC 以支持此操作的 DMA。)

当 MUSBMHDRC 接收到一个数据包时,它将产生相应的端点中断。

ADDR:存储数据包的内存地址

COUNT:数据包大小(通过读取 MUSBMHDRC RxCount 寄存器确定)

CNTL:DMA 启用 (D0) =1;方向 (D1) =0;DMA 模式 (D2) =0;中断启用 (D3) =1;所需的突发模式 (D10–9)。

然后 DMA 控制器将请求总线控制权并将数据包传输到内存。

将产生一个 DMA 中断(DMA_NINT 拉低),然后处理器应清除 MUSBMHDRC RxCSR 寄存器中的 RxPktRdy 位。

单个数据包:TX ENDPOINT

要使用 DMA 模式 0 执行此操作,应将 MUSBMHDRC Tx 端点编程如下:

IntrTxE 寄存器中的相关中断使能位设置为 1。

相应的 TxCSR 寄存器的 DMAReqEnab 位 (D12) 设置为 0。(注意:无需设置 MUSBMHDRC 以支持此操作的 DMA。)

当 MUSBMHDRC 中的 FIFO 可用时,MUSBMHDRC 将使用适当的 Tx 端点中断来中断处理器。

COUNT :要发送的数据包的大小

CNTL : DMA 使能 (D0) =1; 方向 (D1) =1; DMA 模式 (D2) =0; 中断使能 (D3) =1;

所需的突发模式 (D10–9)。

然后 DMA 控制器将请求总线控制并将数据包传输到 MUSBMHDRC FIFO。当它完成传输时,它将产生一个 DMA 中断。然后处理器应设置 MUSBMHDRC TxCSR 寄存器中的 TxPktRdy 位。

多个数据包:RX ENDPOINT

多个数据包的传输通常使用 DMA 模式 1 进行。

如果要使用 DMA 模式 1 接收多个数据包,则 DMA 控制器应按如下方式编程:

ADDR :存储传输的缓冲区的内存地址

COUNT:数据缓冲区的最大大小

CNTL:DMA 启用 (D0) =1;方向 (D1) =0;DMA 模式 (D2) =1;中断启用 (D3) =1;所需的突发模式 (D10–9)。

并且 MUSBMHDRC Rx 端点应按如下方式编程:

IntrRxE 寄存器中的相关中断使能位应设置为 1。

相应 RxCSR 寄存器的 AutoClear (D15)、DMAReqEnab (D13) 和 DMAReqMode (D11) 位应设置为 1。在主机模式下,AutoReq (D14) 位也应设置为 1,并且应对 RqPktCount 寄存器进行编程与传输中的数据包数。

当 MUSBMHDRC 接收到每个数据包时,DMA 控制器将请求总线控制权并将数据包传输到内存。AutoClear 置位后,MUSBMHDRC 将自动清除 RxPktRdy 位。

在外围模式或 RqPktCount 为零时,此过程将自动继续,直到 MUSBMHDRC 接收到一个“短数据包”(小于端点的最大数据包大小之一),表示传输结束。

由 DMA 控制器传输:相反,MUSBMHDRC 将通过生成适当的端点中断来中断处理器。模式 0 卸载数据包。

在 AutoReq 设置且 RqPktCount 非零的主机模式下,内核将在每次请求后递减 RqPktCount 寄存器中的值。当值从 1 递减到 0 时,AutoReq 位被清除以防止尝试任何进一步的事务。

DMA 控制器 ADDR 寄存器将随着数据包的卸载而增加,因此处理器可以通过将 ADDR 的当前值与内存缓冲区的起始地址进行比较来确定传输的大小。

注意:如果传输的大小超过数据缓冲区大小,DMA 控制器将停止卸载 FIFO 并通过 DMA_NINT 线中断处理器。

多个数据包:TX ENDPOINT

要使用 DMA 模式 1 执行此操作,应将 DMA 控制器编程如下:

ADDR : 要发送的数据块的内存地址

COUNT:数据块的大小

CNTL:DMA 启用 (D0) =1;方向 (D1) =1;DMA 模式 (D2) =1;中断启用 (D3) =1;所需的突发模式 (D10–9)。

并且 MUSBMHDRC Tx 端点应按如下方式编程:

IntrTxE 寄存器中的相关中断使能位应设置为 1(只是为了检测错误)。

相应 TxCSR 寄存器的 AutoSet (D15)、DMAReqEnab (D12) 和 DMAReqMode (D10) 位应设置为 1。

当 MUSBMHDRC 中的 FIFO 可用时,DMA 控制器将请求总线主控权并将数据包传输到 FIFO。AutoSet 设置后,MUSBMHDRC 将自动设置 TxPktRdy 位。MUSBMHDRC。然后,DMA 控制器将中断处理器DMA_NINT 低。如果要加载的最后一个数据包小于端点的最大数据包大小,则不会为该数据包设置 TxPktRdy 位:因此,处理器应通过设置 TxPktRdy 位来响应 DMA 中断以允许最后一个要发送的“短数据包”。如果要加载的最后一个数据包具有最大数据包大小,则要采取的操作取决于传输是否受应用程序(例如 Windows 系统上的大容量存储软件)的控制对发送的单个数据包进行计数。如果传输不受此类控制,处理器仍应响应通过设置 TxPktRdy 位来实现 DMA 中断。这具有发送空数据包的效果,接收软件将其解释为指示传输结束。

VBUS 事件

USB On-The-Go 规范定义了一系列阈值,点对点通信中涉及的设备必须响应这些阈值:

• VBus Valid(要求大于 4.4 和 4.75VV)

• 会话对“A”设备有效(要求在 0.8V 和 2.1V 之间)

• 会话结束(要求在 0.2V 和 0.8V 之间)

(特定设备中使用的实际阈值通过 MUSBMHDRC 内核外部的一系列比较器设置,这些比较器根据 VBus 的电平将相应的 VBUSVALID、AVALID 和 SESSEND 输入设为高或低。)

这些阈值中的哪一个是关键的,以及控制 MUSBMHDRC 的 CPU 需要响应的方式取决于设备是“A”设备还是“B”设备以及事件发生的环境。

作为A设备

VBus > VBus Valid 与由 MUSBMHDRC 发起的会话(即 Vbus[1:0] (DevCtl.[D4:D3]) = 11b, Session bit (DevCtl.D0) set)。当 VBus 变得大于 VBus Valid 时,MUSBMHDRC 选择主机模式并等待设备连接。然后产生连接中断 (IntrUSB.D4)。CPU 应复位并枚举连接的“B”设备。

VBus > 会话有效,会话由“B”设备发起(即 Vbus[1:0] (DevCtl.[D4:D3]) = 10b,会话位 (DevCtl.D0) 清除)。当 VBus 变得大于会话有效时, MUSBMHDRC 将产生会话请求中断 (IntrUSB.D6)。CPU 应设置会话位。然后 MUSBMHDRC 将保持在主机模式或更改为外设模式,具体取决于“B”上的上拉电阻器的状态’ 设备。所选模式将由主机模式位 (DevCtl.D2) 的状态指示。

VBus 低于 VBus 有效,而会话位保持设置(即 Vbus[1:0] (DevCtl.[D4:D3]) ≠ 11b,会话位 (DevCtl.D0) 设置)。这表明 VBus 功率电平存在问题。例如,电池电量可能降得太低,无法维持 VBus Valid。或者,“B”设备消耗的电流可能超过“A”设备所能提供的电流。在任何一种情况下,MUSBMHDRC 都会自动终止会话并生成VBus 错误中断 (IntrUSB.D7)。

作为B设备

VBU> Session Valid

(即vbus [1:0](devctl。[d4:d3])= 10b,session bit(devctl.d0)清晰)。这表示活动中的活动。MusbMHDRC将设置会话位并进行bit dppulldown输出低,以断开D+线上的下拉电阻

vbus < Session Valid while the Session bit remains set

(即vbus [1:0](devctl。[d4:d3])= 01b,session bit(devctl.d0)设置)。这表明“ A”设备已经损失了功率(或断开连接)。MusbMHDRC将会清除会话位(devctl.d0)并生成断开中断(Intusb.d5)。CPU应结束会话。

VBUS < Session End

(即vbus [1:0](devctl。[d4:d3])= 00b)。这是’b’设备可以启动会话请求的条件。如果设置了会话位(devctl.d0),则然后,在总线上2ms的SE0之后,MusBMHDRC将首先脉动数据线,然后脉动VBU(通过将CHRGVBUS提高)来启动SRP。

动态 FIFO 大小

如果需要,可以将MusBMHDRC配置为单个FIFO大小为128、256、512、1K…64K字节,当MusbMHDRC初始化时,可能会分配给不同端点的区域。)

注意:强烈建议您仅在需要不同 FIFO 大小的设备中使用 MUSBMHDRC 时使用此功能。

如果不需要更改FIFO尺寸,则最好通过标准配置选项设置这些尺寸,因为动态FIFO尺寸的选项会显着增加核心的尺寸,并且需要更复杂的固件来处理它。

将 FIFO 空间分配给不同的端点需要每个 Tx 和 Rx 端点的规范:

•RAM块中FIFO的起始地址

• 支持的最大数据包大小

• 是否需要双缓冲

(最后两个一起定义了需要分配给 FIFO 的空间量。)

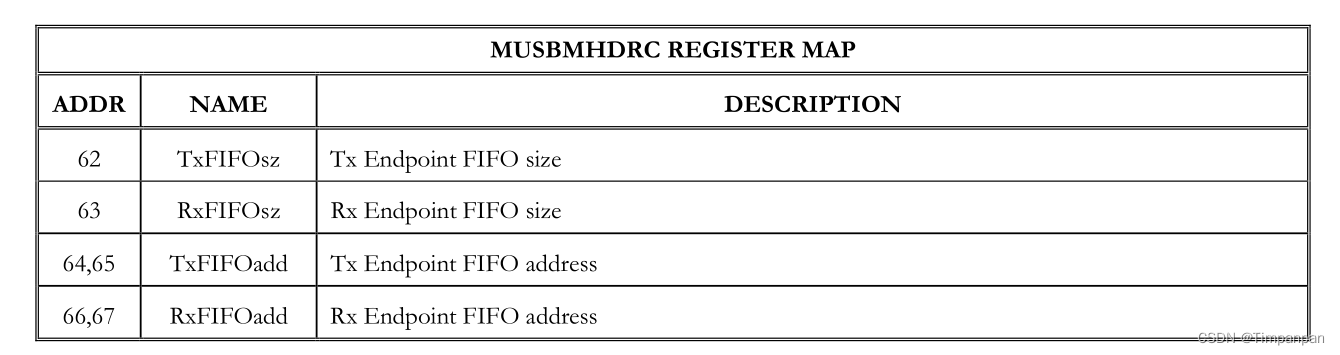

这些细节可以通过以下四个寄存器来指定,它们被添加到MUSBMHDRC的Indexed area

选择动态 FIFO 大小选项时的寄存器映射:

注意: (i) 动态设置 FIFO 大小的选项仅适用于端点 1…15。端点 0 FIFO 具有固定大小(64 字节)和固定位置(起始地址 0)。

(ii) 固件(和系统设计人员)有责任确保在当前 USB 配置中处于活动状态的所有 Tx 和 Rx 端点都有一个专门分配给它们的 RAM 块,该 RAM 块至少与为端点设置的最大数据包大小。

1217

1217

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?