- Module Name : SPI_receive

- Engineer : Bai Fengqiang

- Target Device : EP2C8Q208C8

- Tool versions : Quartus II 13.1

- Create Date : 2017-7-17

- Revision : v1.0

- Description :

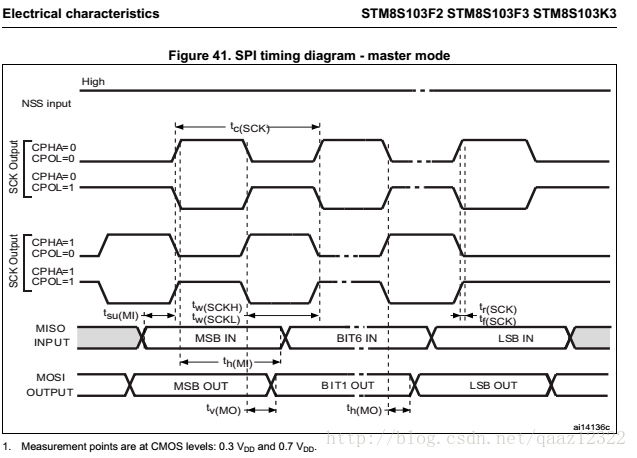

由以上时序图可知,我们采用主机模式,同时SPI作为一种外部串行传输协议,它主要由四根线控制,即SPI_CS(片选信号,有了它可以实现一个主机,多个从机的片间通信,),SPI_SCK(SPI数据串行传输时钟线),SPI_MOSI(从机输入/主机输出数据),SPI_MISO(从机输出/主机输入数据),关于传输协议一共有4种模式,由CPHA与CPOL控制,具体情况,具体分析,在此文中,我门将CPOL配置为0,CPHA配置为1,(CPOL=0,CPHA=1),即时钟上升沿采样。

由时序图可分析如:

1.SPI_CS在低电平时有效,高电平时属于无效状态。

2.SPI_MOSI在片选信号下降沿时有效,并在SPI_CLK上升沿捕获数据。

3.SPI_MISO在片选信号下降沿时有效,并在SPI_CLK上升沿捕获数据。

所以SPI_CLK的上升沿极为重要,我们可以利用脉冲边缘检测法获得,同时从MCU中送入FPGA的各种数据或者信号,属于不同时钟域的,故需要做同步,在脉冲边缘检测时,使用了两个寄存器,故在这里也使用两个,另外为了防止亚稳态的产生,我们这里采用同步释放,异步复位的处理机制。

具体代码如下:

module SPI_receiver(

clk,

rst_n,

spi_cs,

spi_data_in,

spi_clk,

reveice_data,

receiver_flag,

true_rst,

rst_n1,

rst_n2,

spi_clk1,

spi_clk2,

spi_posedge_clk,

spi_cs1,

spi_cs2,

spi_data1,

spi_data2,

spi_cs_true,

spi_true_data,s

pi_receiver_data_finish_flag,

receiver_data_cnt,

receiver_data_r

);

//global input clk and rst_n

input clk;

input rst_n;

//SPI user interface

input spi

该博客详细介绍了如何在SPI协议中使用MCU与FPGA进行片间通信,FPGA作为从机。文章讲解了SPI的基本构成和工作模式,特别强调了CPOL=0,CPHA=1的配置,以及在上升沿采样的重要性。博主通过Verilog代码展示了数据同步和亚稳态避免的方法,并提供了仿真脚本和结果,验证了8'h95和8'hbe数据正确接收。

该博客详细介绍了如何在SPI协议中使用MCU与FPGA进行片间通信,FPGA作为从机。文章讲解了SPI的基本构成和工作模式,特别强调了CPOL=0,CPHA=1的配置,以及在上升沿采样的重要性。博主通过Verilog代码展示了数据同步和亚稳态避免的方法,并提供了仿真脚本和结果,验证了8'h95和8'hbe数据正确接收。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?