文章目录

4.25.1 关于写操作的时序参数

图100以写前导1tCK为例,主要说明DQS信号的时序参数,对于一个有效的burst传输,其所有的DQS边沿都需满足以下时序。

BL=8, WL=9(AL=0, CWL=9)

DES命令在此处只用做解释说明,也可以为其它有效命令。

对于每个时钟的上升沿,都必须满足时序tDQSS。

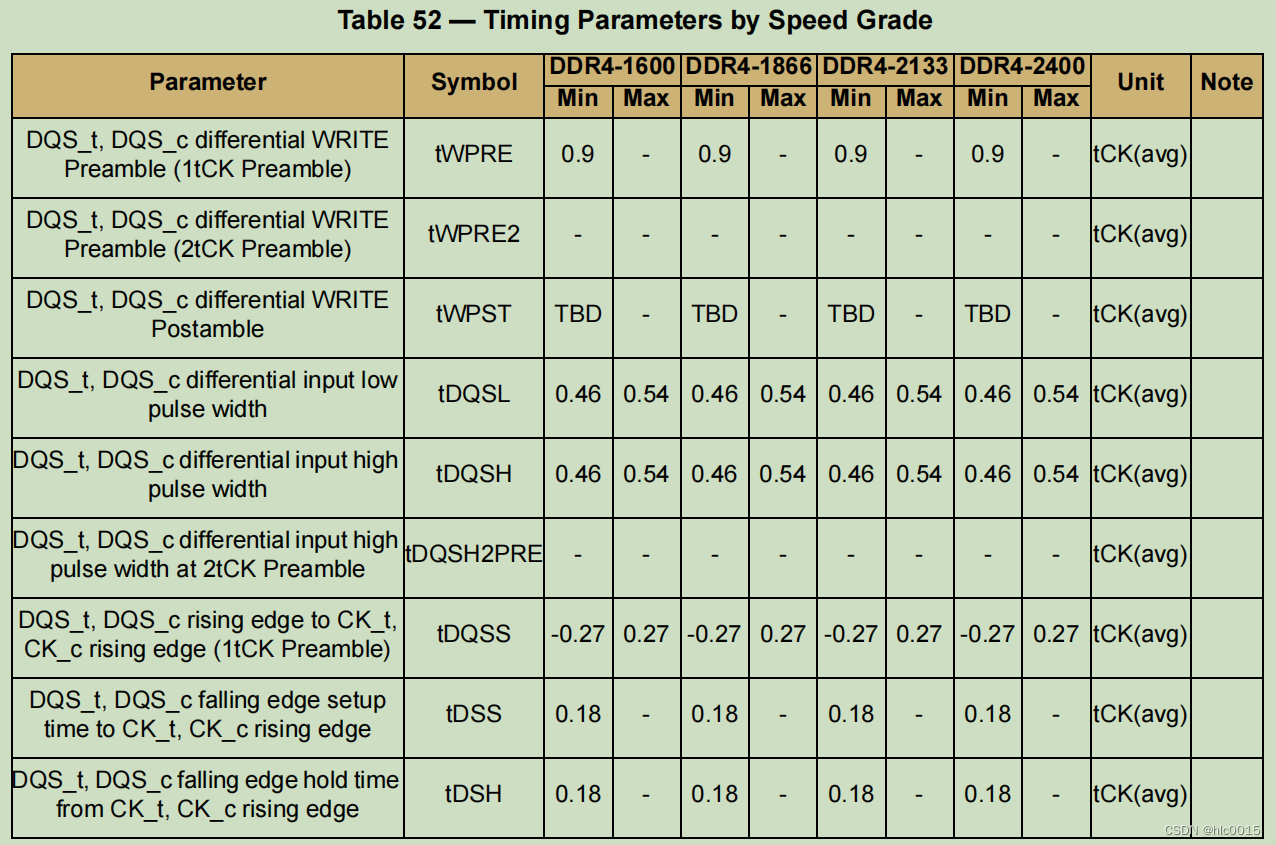

这里直接将手册后续的表52放于此处,用于解释各项参数为何意。

结合图和表,最重要的就是时序tDQSS,这个参数决定了DQS的位置。由于表中tDQSS(简单来讲便是DQS_t上升沿到CK_t上升沿的时间),tDQSS有正负两个取值,故上图中画了3条DQS信号,分别代表tDQSS=-0.27tCK、tDQSS=0和tDQSS=0.27tCK的情况。

表中的tDQSL和tDQSH的最大值值得注意,为0.54tCK,这也是tDQSS的系数为0.27的原因(0.27=0.54/2)。

由于手册中写前导为2tCK模式的图比较模糊,此处不贴图。但是需要注意,当写前导为2tCK时,WL=10(AL=0, CWL=9+1),这是因为在写前导为2tCK时,CWL必须比CWL的最小值至少大1。

4.25.2 关于Write DM

与DDR3一样,DDR4也支持DM。一个DQ线上传输8bit数据,其DM_n信号在某个bit上拉低则指示该bit不写入SDRAM中,如图100所示。在读操作中,不支持DM。DM_n/DBI_n/TDQS三个信号共用一个pin。

4.25.3 tWPRE时序的计算

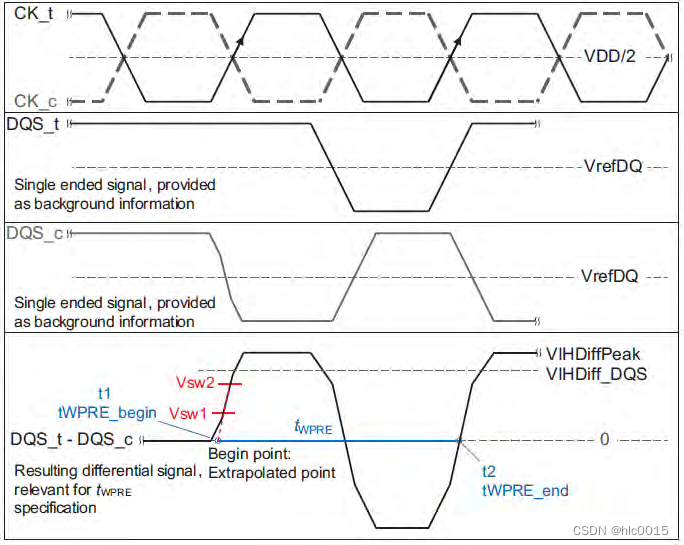

上图展示了tWPRE时序的计算方式。当DQS_t-DQS_c的值从Vsw1到Vsw2处时,两点连线与0的交点为起始点;其值再次变为0的时候为终点,由此得出tWPRE时序。

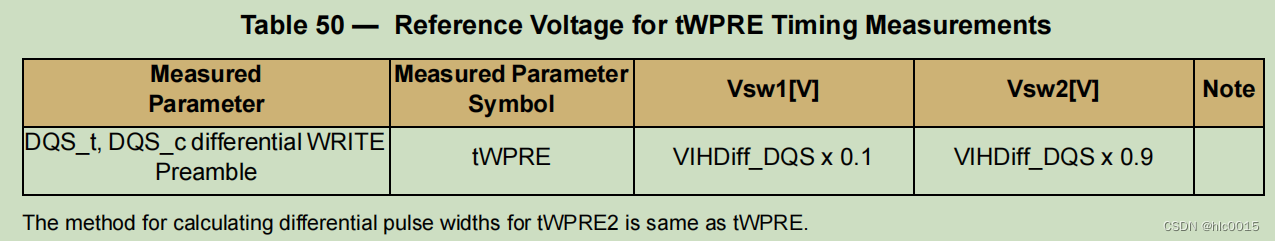

表50表明了Vsw1和Vsw2的取值。

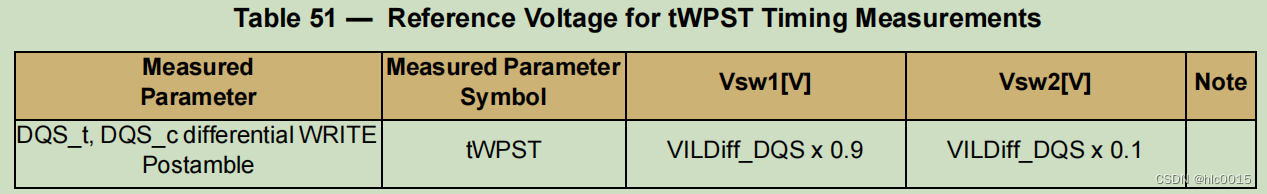

4.25.4 tWPST时序的计算

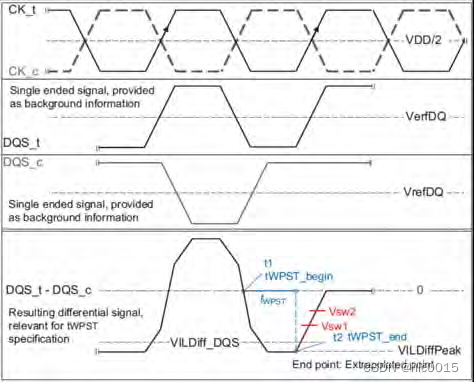

上图有些模糊,展示了tWPST时序的计算过程。其原理和tWPRE的计算方式类似。需要注意的是,终点并不是在DQS_t-DQS_c = 0处。

表51展示了Vsw1和Vsw2的取值点。

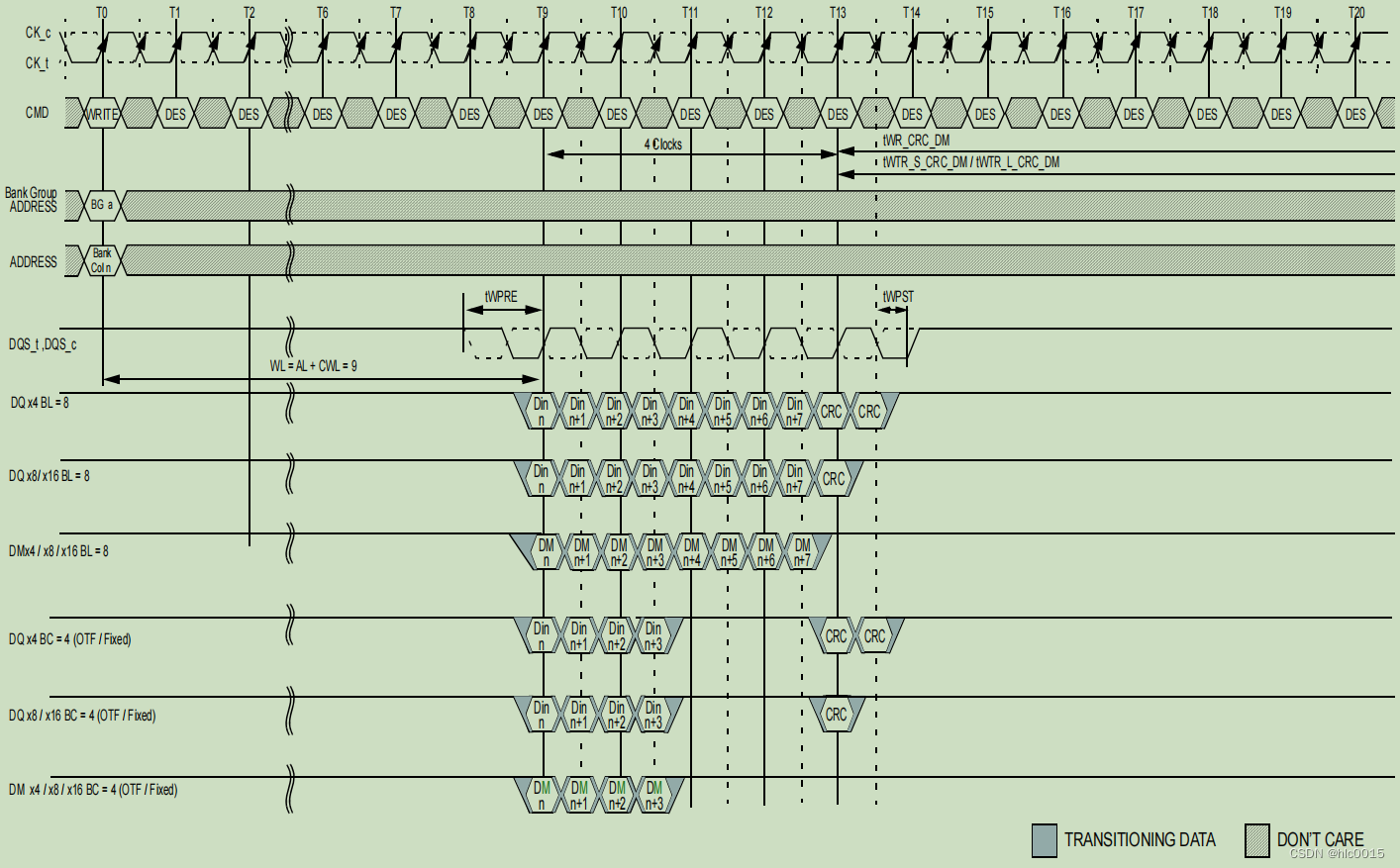

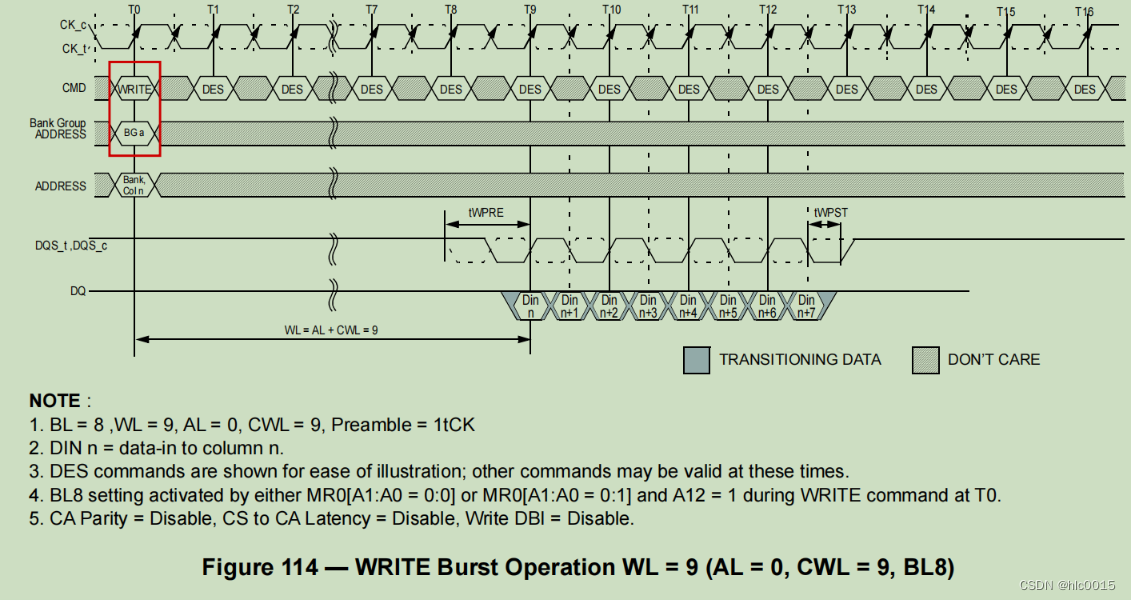

4.25.5 突发写操作

为了方便说明,以下时序图中CK和DQS信号都是对齐的,DQS的上升沿也正好位于DQ信号的中心位置。

以下各图中,若未做特殊说明,其DES命令只是方便做说明,其它的有效命令也可以替换DES命令发送。

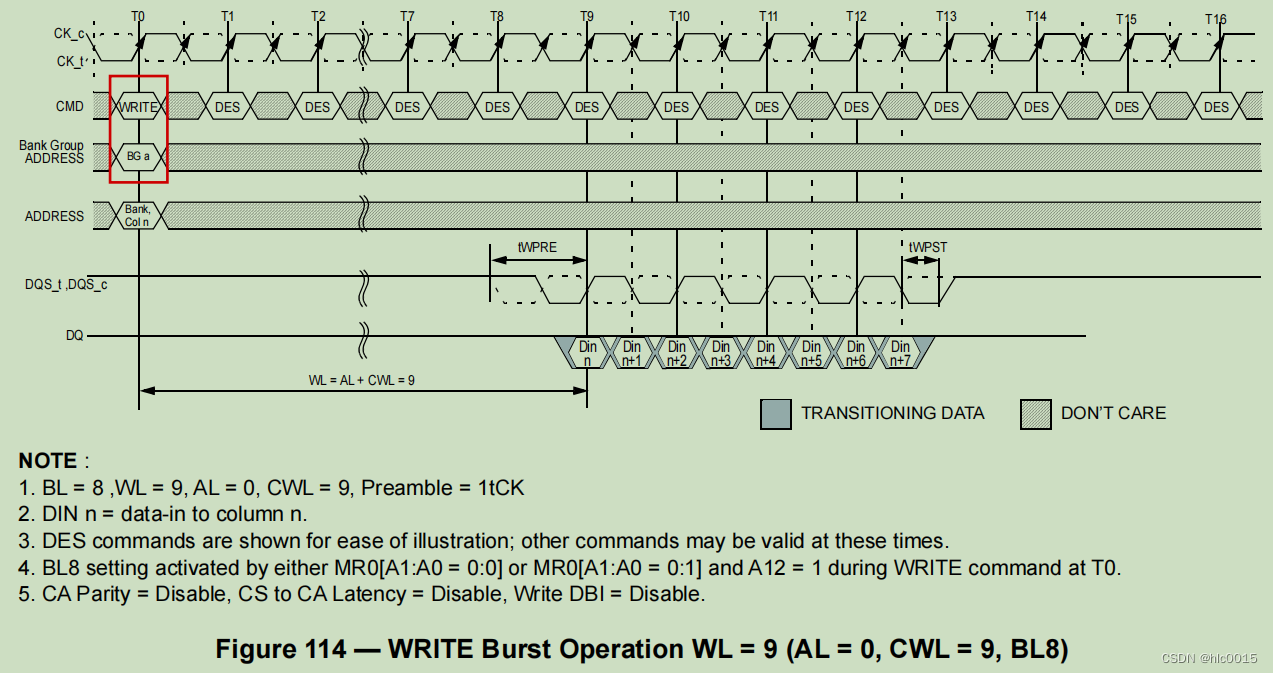

普通的单个写操作

图114表明普通的,对单个BG的一个突发写操作。其中BL=8, WL=9, AL=0, CWL=9, 写前导为1tCK。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

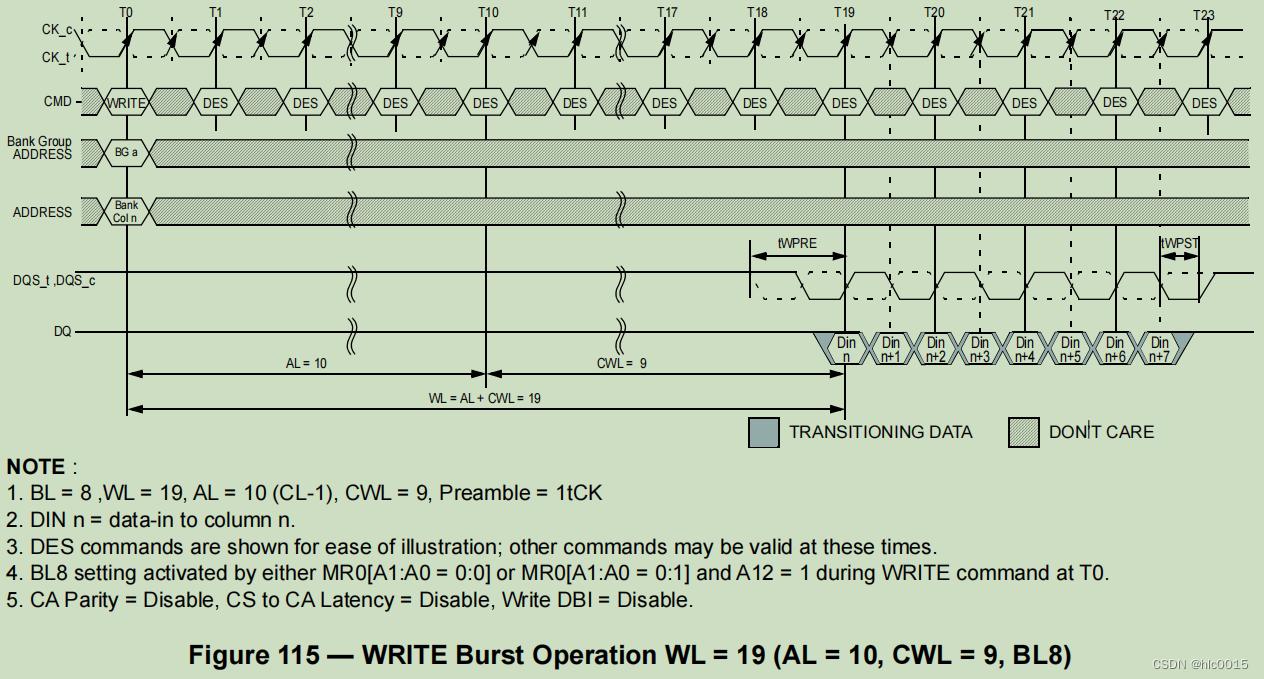

图115与图114相似,仅将AL增加为10。BL=8, WL=9, AL=10, CWL=9, 写前导为1tCK。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

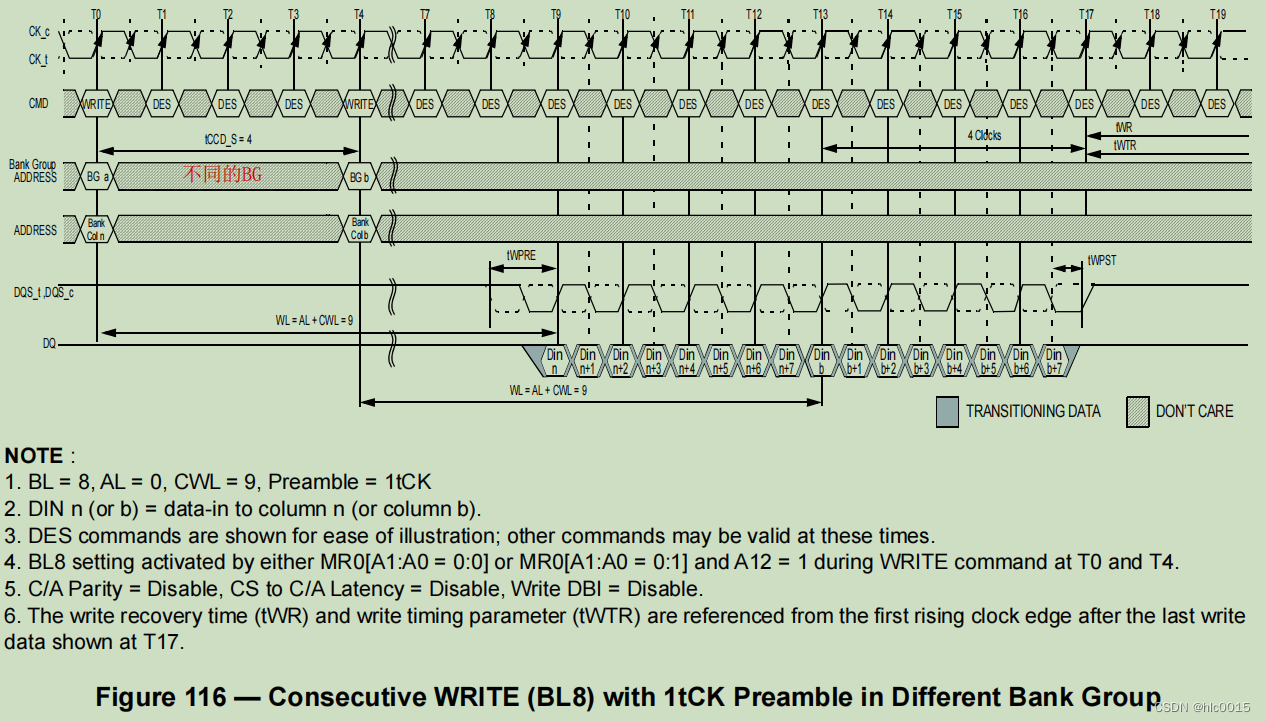

连续写操作

图116表明对不同的BG进行连续写操作。其中突发长度为BL8,WL=9, AL=0, CWL=9, 写前导为1tCK。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写书序参数tWTR从T17时刻开始,该时刻为最后一个写数据之后的CK上升沿。该时刻也可以说成,第二个burst操作的第一个数据,往后延4个CK的时刻。

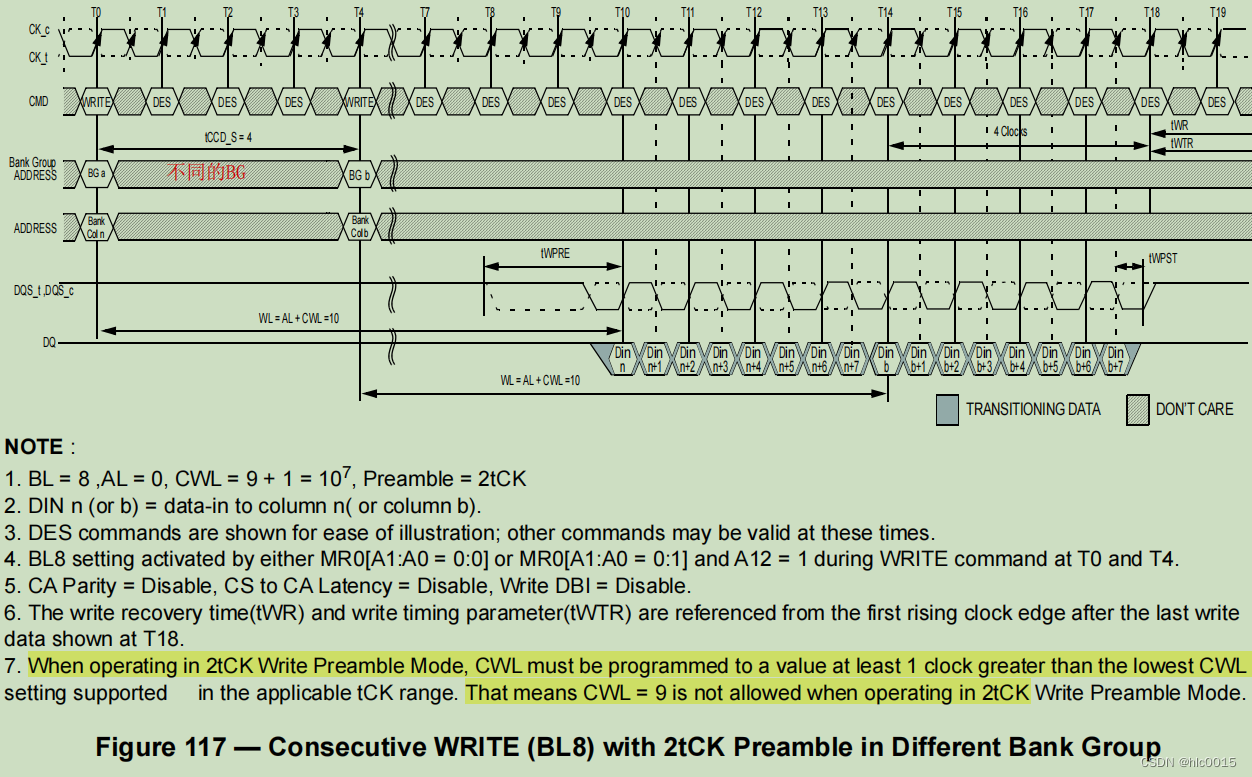

图117与图116类似,仅将写前导更改为2tCK。BL8,WL=9, AL=0, CWL=9+1=10。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写书序参数tWTR从T18时刻开始,该时刻为最后一个写数据之后的CK上升沿。该时刻也可以说成,第二个burst操作的第一个数据,往后延4个CK的时刻。

当写前导为2tCK时,CWL必须比最小的CWL值至少大1,故此图中的CWL=10。

不连续写操作

连续的写Wie两个写命令间隔周期为4个CK周期,而不连续的写为俩写命令周期间隔大于4。由于其大于4,故可以在另一个BG中进行写操作,不一定两次写操作都是相同的BG(同理,俩不连续读也类似)。

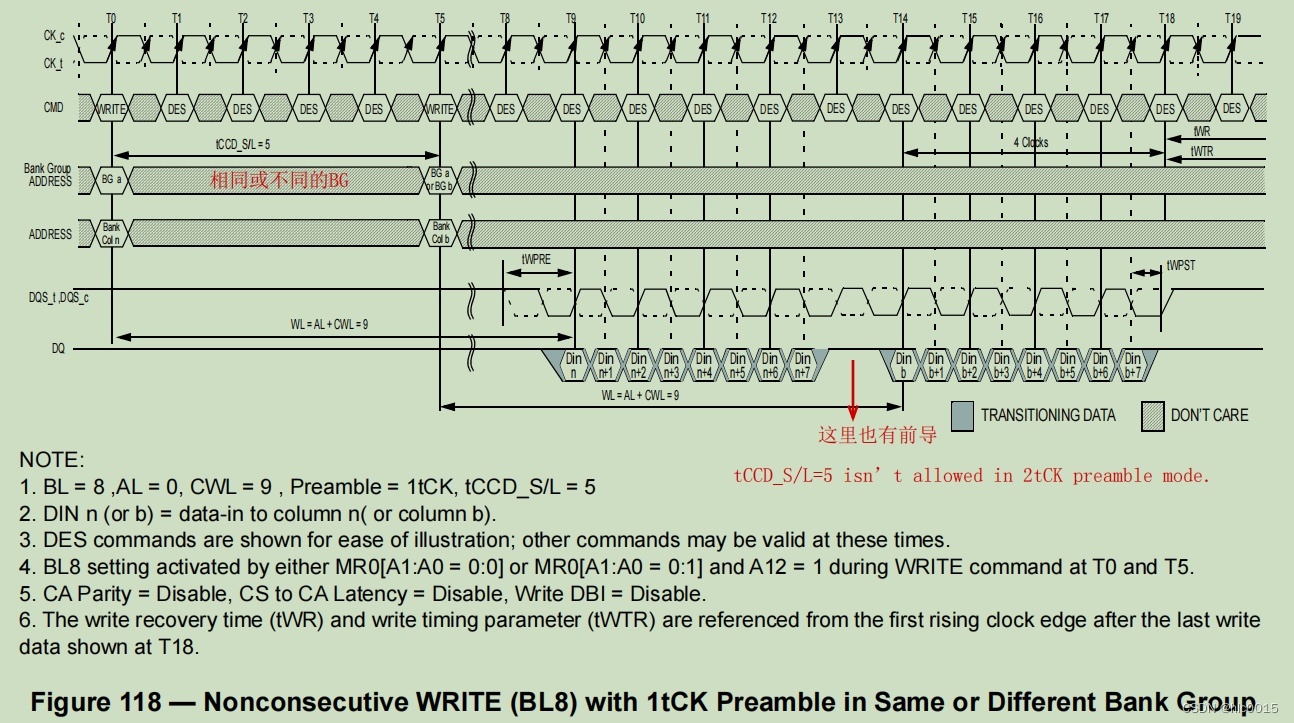

图118表明了两个不连续的写操作。BL=8 ,AL=0, CWL=9, tCCD_S/L = 5, 写前导为1tCK。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写书序参数tWTR从T18时刻开始,该时刻为最后一个写数据之后的CK上升沿。该时刻也可以说成,第二个burst操作的第一个数据,往后延4个CK的时刻。

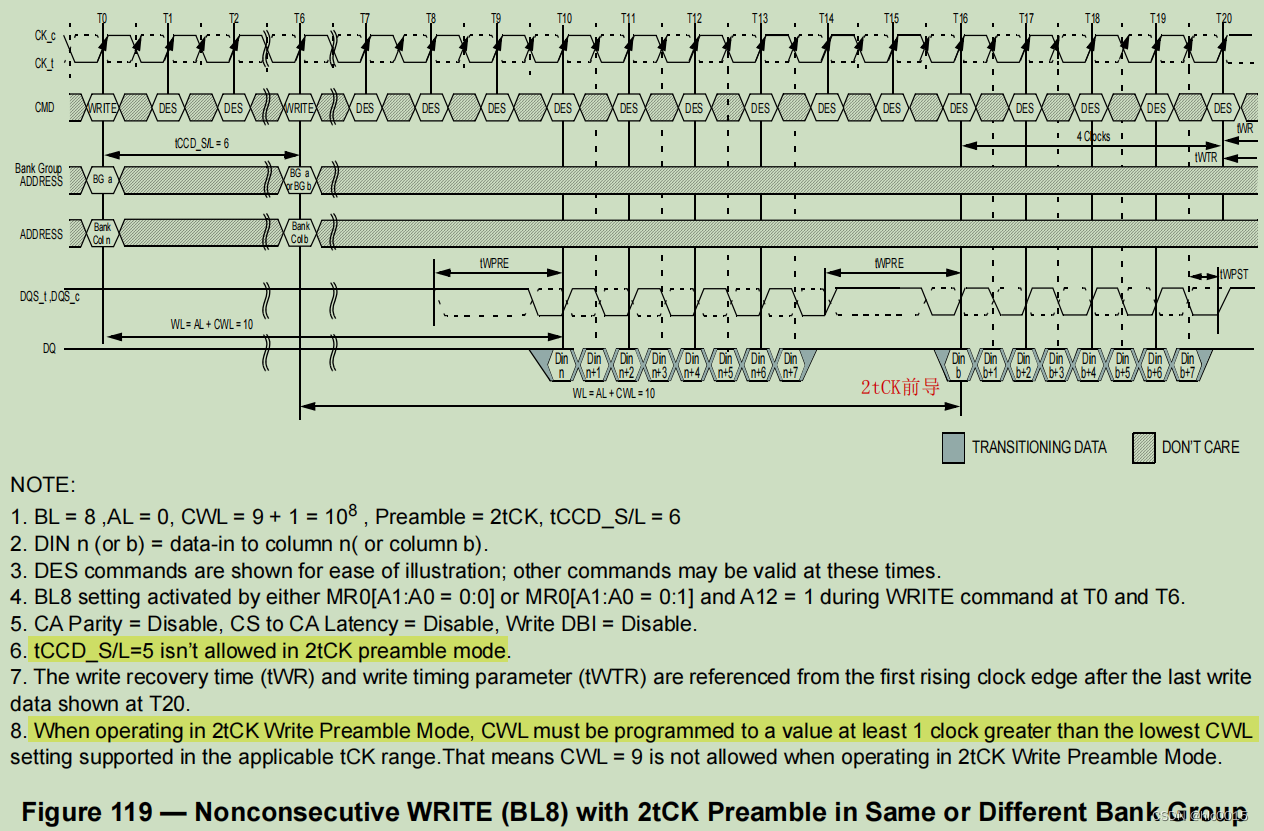

图119与图118类似,写前导改为2tCK,BL=8 ,AL=0, CWL=9+1=10, tCCD_S/L = 6。

tCCDS/L=5时不支持2tCK的写前导。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写书序参数tWTR从T20时刻开始,该时刻为最后一个写数据之后的CK上升沿。该时刻也可以说成,第二个burst操作的第一个数据,往后延4个CK的时刻。

当写前导为2tCK时,CWL必须比最小的CWL值至少大1,故此图中的CWL=10。

BC4 to BC4的写操作

OTF(on the fly) BC4 to BC4

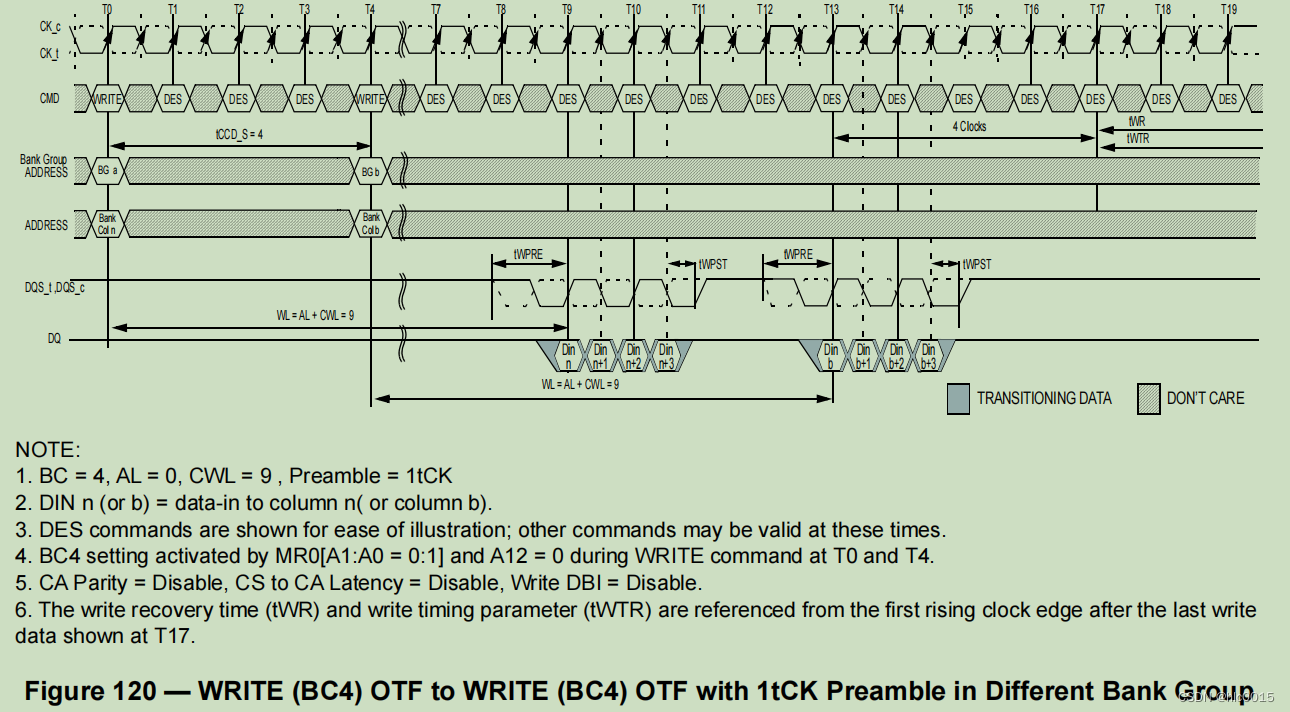

图120表示BC4(OTF)到BC4(OTF)的写操作,由tCCD_S=4可知,其实对不同的BG进行操作。BC=4, AL=0, CWL=9, 写前导为1tCK。

在T0和T4处,BC4(OTF)的设置为MR0的A[1:0]=01 && A12=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写书序参数tWTR从T17时刻开始,由于BC4操作需要占用4个CK周期,与BL8操作所占的时长相同,故tWR和tWTR的起点与BL8操作的起点相同。该时刻也可以说成,第二个burst操作的第一个数据,往后延4个CK的时刻。

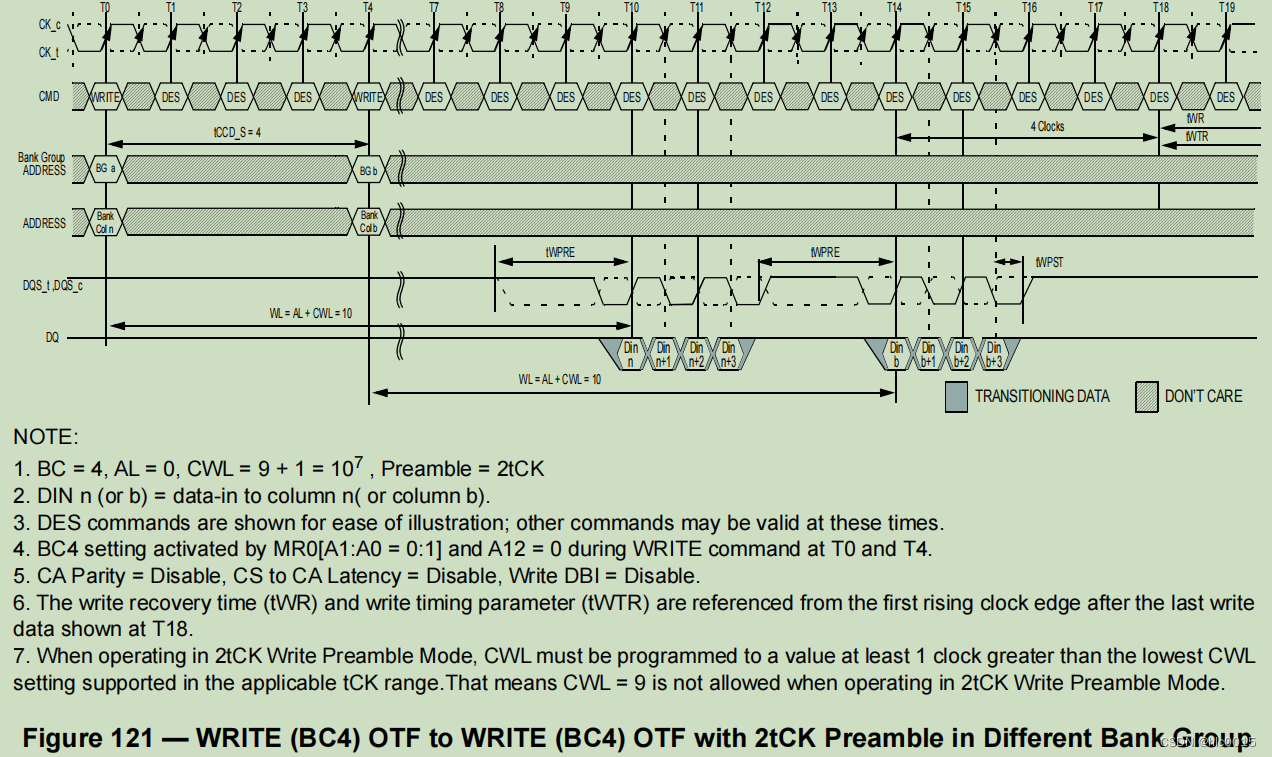

图121与图120类似,写前导改为2tCK。BC=4, AL=0, CWL=9+1=10, tCCD_S=4。

在T0和T4处,BC4(OTF)的设置为MR0的A[1:0]=01 && A12=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写书序参数tWTR从T17时刻开始,由于BC4操作需要占用4个CK周期,与BL8操作所占的时长相同,故tWR和tWTR的起点与BL8操作的起点相同。该时刻也可以说成,第二个burst操作的第一个数据,往后延4个CK的时刻。

当写前导为2tCK时,CWL必须比最小的CWL值至少大1,故此图中的CWL=10。

Fixed BC4 to Fixed BC4

图122与图120类似,其区别在于此处的BC4为Fixed类型的BC4。前导时钟为1tCK,BC=4, AL=0, CWL=9。

由于是BC4 Fixed,故MR0的A[1:0]必须为10。

由于是BC4 Fixed,其传输数据并不像BC4(OTF)那样需要4个CK周期,故回复时间tWR和写时间参数tWTP可以从最后一个写数据之后的CK上升沿作为起点开始计算。换句话说,起点从第二个突发写操作的第一个数据之后,再延两个CK周期,开始计算。

从写到读

BL8 to BL8

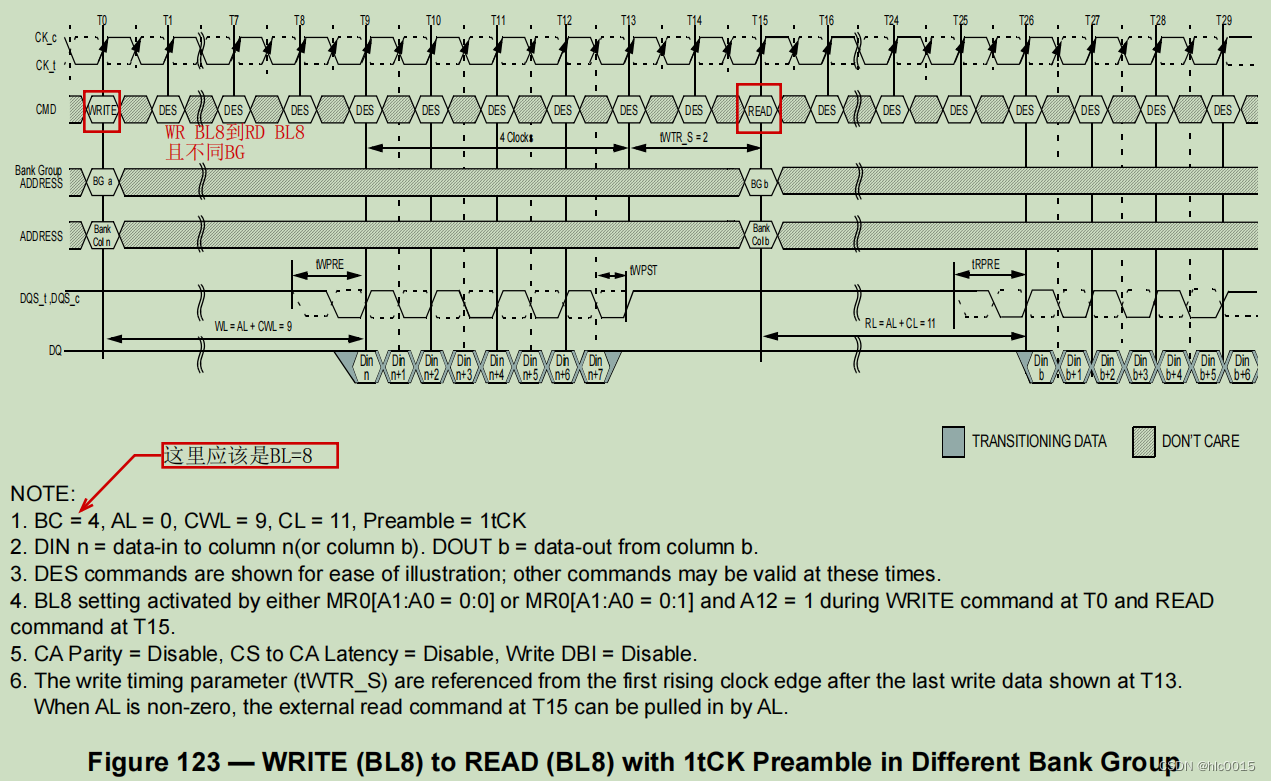

图123展示了在不同的BG下,写命令到读命令的时序,其中BL=8,AL=0, CWL=9, CL=11。读写前导为1tCK。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

时序tWTR_S从T13时刻开始计算,即BL8的最后一个数据之后的第一个CK上升沿。如果AL不等于0,那么T15时刻的读命令还需往后移AL个CK。

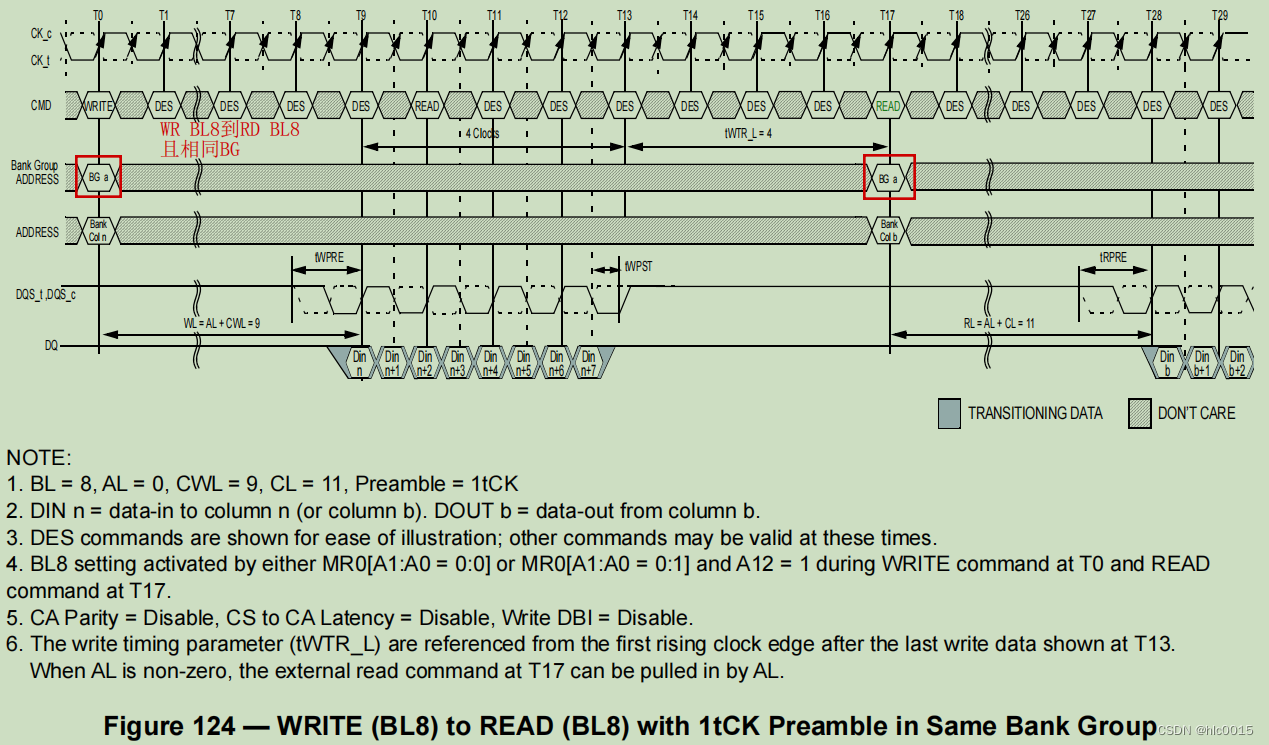

图124展示了在相同的BG下,写命令到读命令的时序,其中BL=8,AL=0, CWL=9, CL=11。读前导为1tCK。由于是在同一个BG下进行操作,故tWTR较长,为4。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

时序tWTR_S从T13时刻开始计算,即BL8的最后一个数据之后的第一个CK上升沿。如果AL不等于0,那么T17时刻的读命令还需往后移AL个CK。

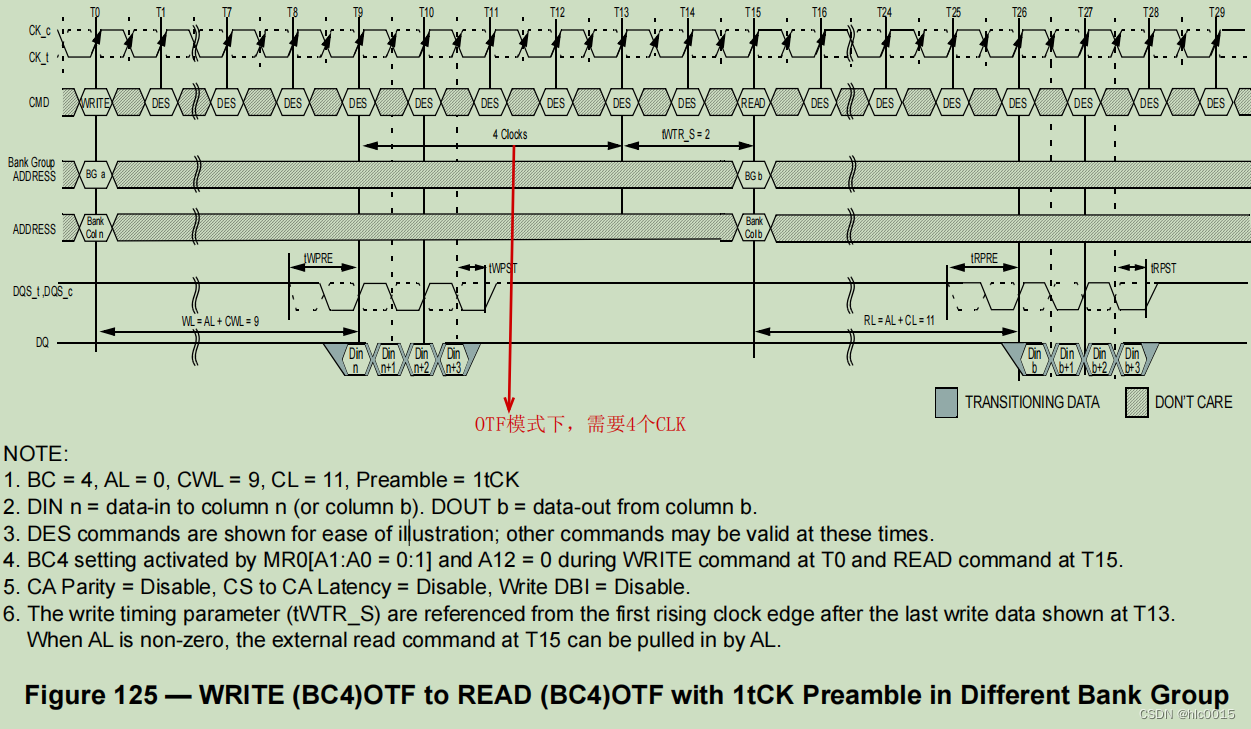

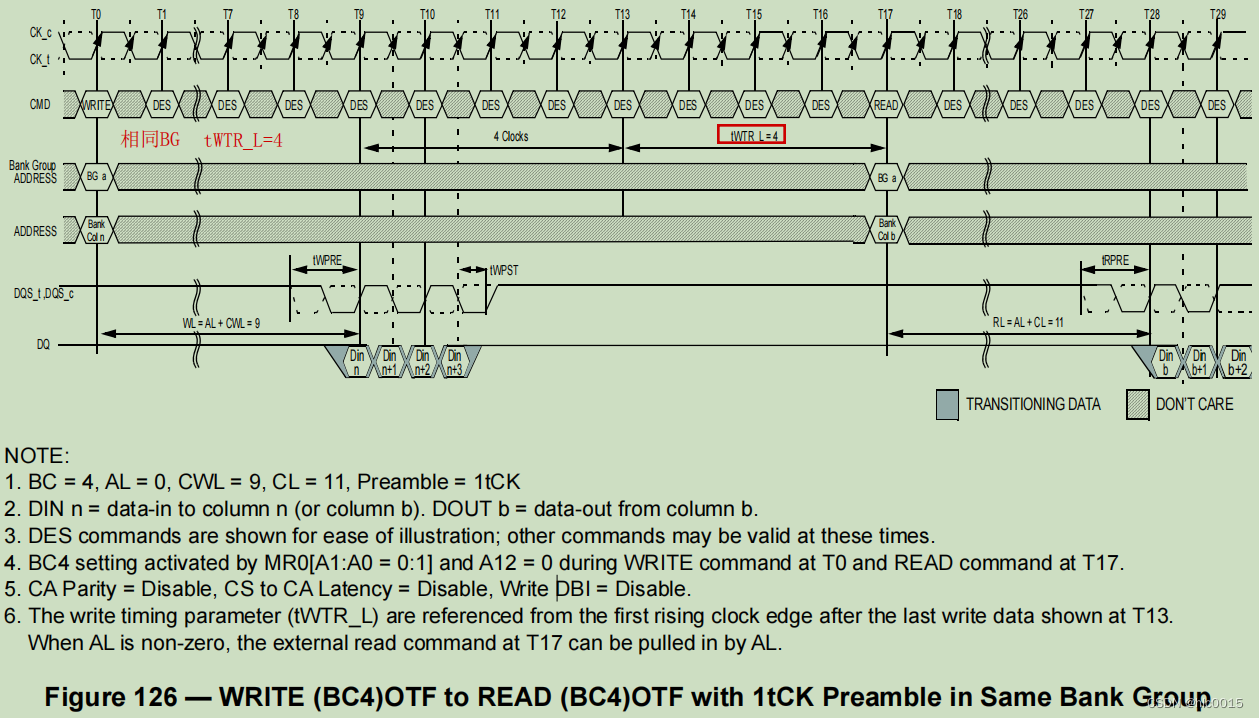

BC4(OTF) to BC4(OTF)

图125展示了在不同BG下,写满了到读命令的时序,其中BC=4,AL=0, CWL=9, CL=11。读写前导为1tCK。由于是OTF模式,即使BC4只传输4个数据(正常情况下传输4个数据只需占据两个CK周期),但仍需占据四个CK周期。tWTR=4。

OTF模式下,MR0的A[1:0]=01,且地址位A12=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

时序tWTR_S从T13时刻开始计算,即BL8的最后一个数据之后的第一个CK上升沿。如果AL不等于0,那么T15时刻的读命令还需往后移AL个CK。

图126与图125类似,仅将读写改为在同一个BG下读写。BC=4,AL=0, CWL=9, CL=11。读写前导为1tCK。tWTR=4。

OTF模式下,MR0的A[1:0]=01,且地址位A12=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

时序tWTR_S从T13时刻开始计算,即BL8的最后一个数据之后的第一个CK上升沿。如果AL不等于0,那么T17时刻的读命令还需往后移AL个CK。

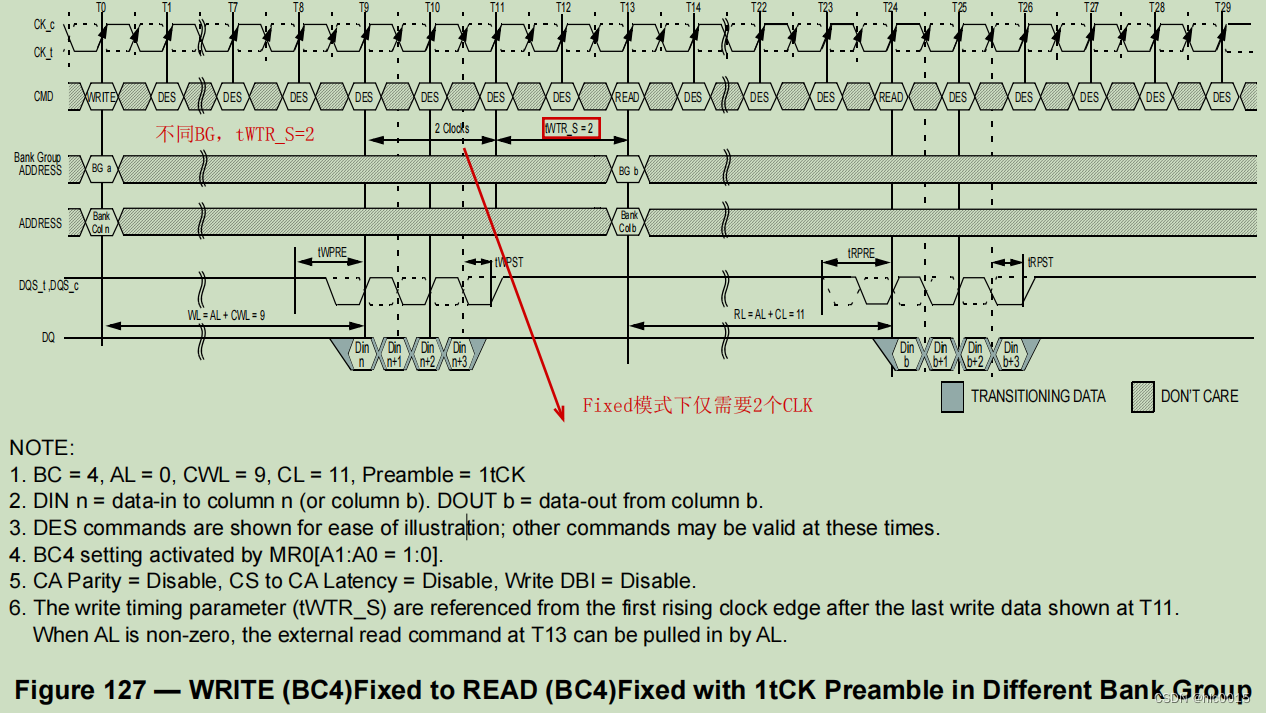

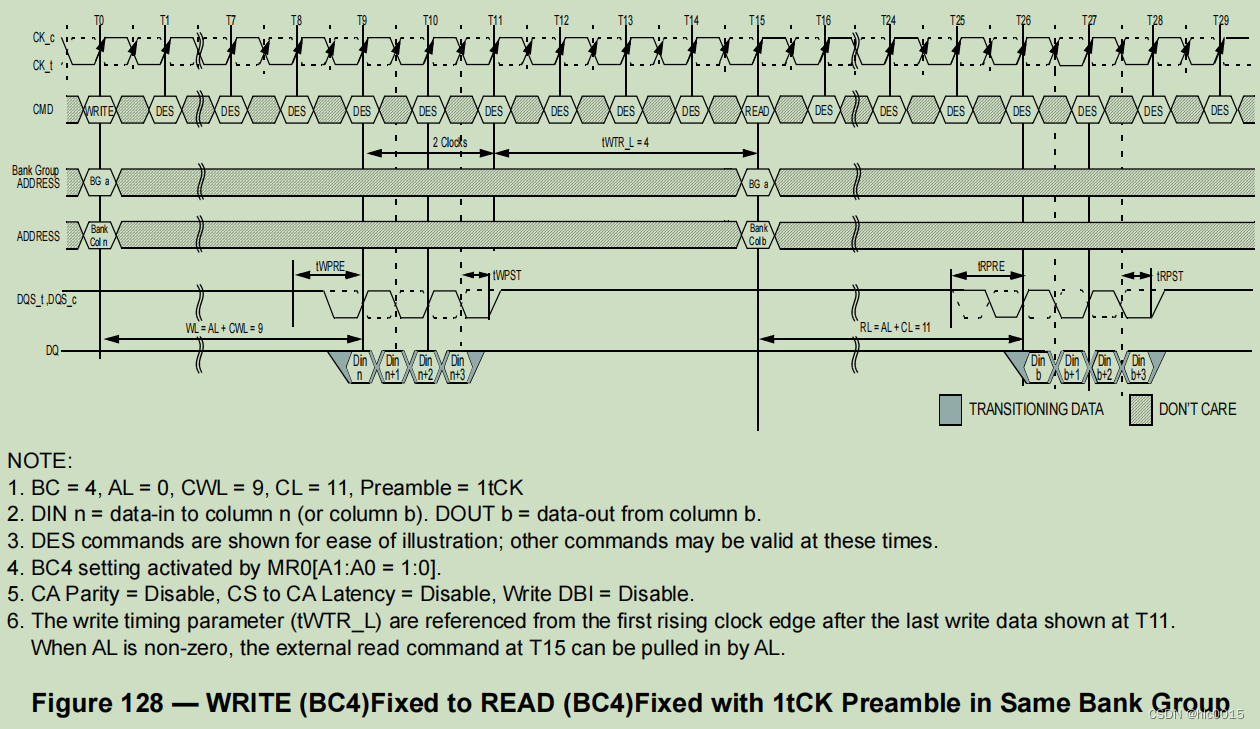

BC4(Fixed) to BC4(Fixed)

图127展示了在不同的BG下,读写突发长度都为BC4(Fixed),BC=4,AL=0, CWL=9, CL=11。读写前导为1tCK。tWTR=2。

由于是Fixed BC4,故其仅需两个CK周期便能将数据传输完成。

Fixed模式下,MR0的A[1:0]=10。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

时序tWTR_S从T11时刻开始计算,即BL8的最后一个数据之后的第一个CK上升沿。如果AL不等于0,那么T13时刻的读命令还需往后移AL个CK。

图128与图127类似,仅将读写改为同一个BG。由于是相同BG,故tWTR会增加,变为4。

Fixed模式下,MR0的A[1:0]=10。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

时序tWTR_S从T11时刻开始计算,即BL8的最后一个数据之后的第一个CK上升沿。如果AL不等于0,那么T15时刻的读命令还需往后移AL个CK。

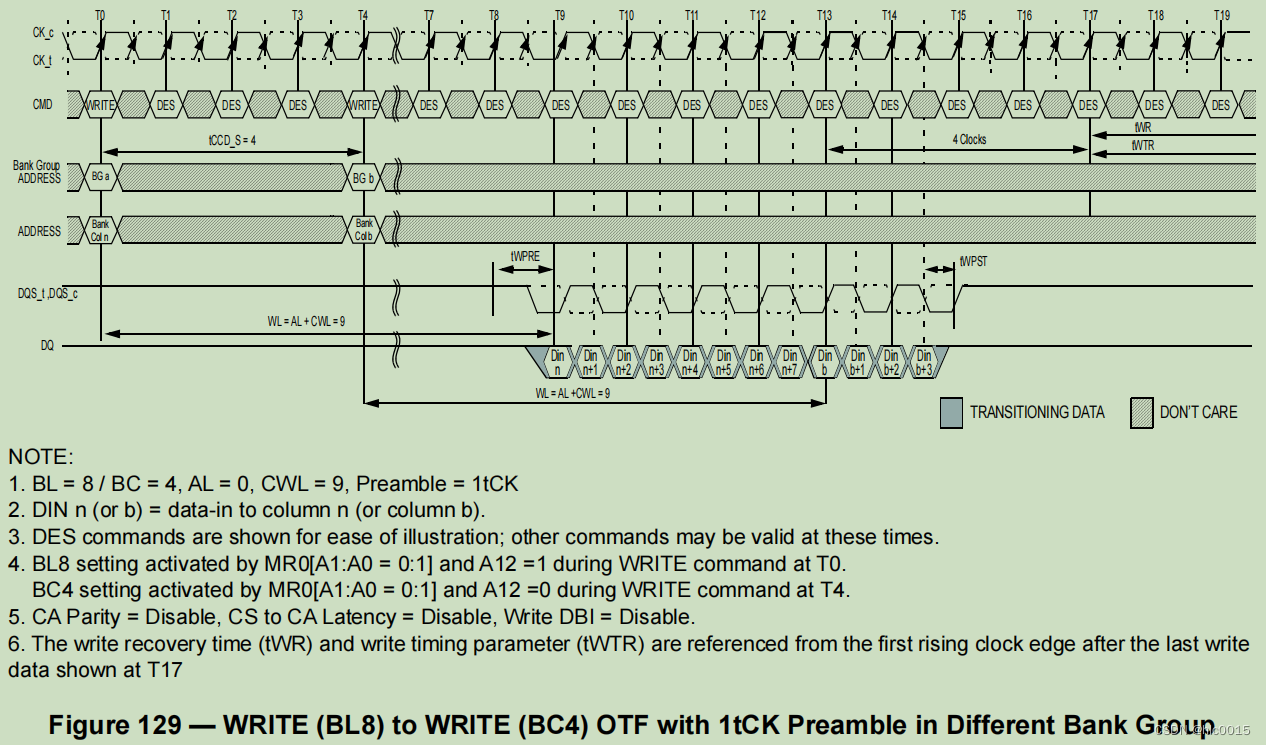

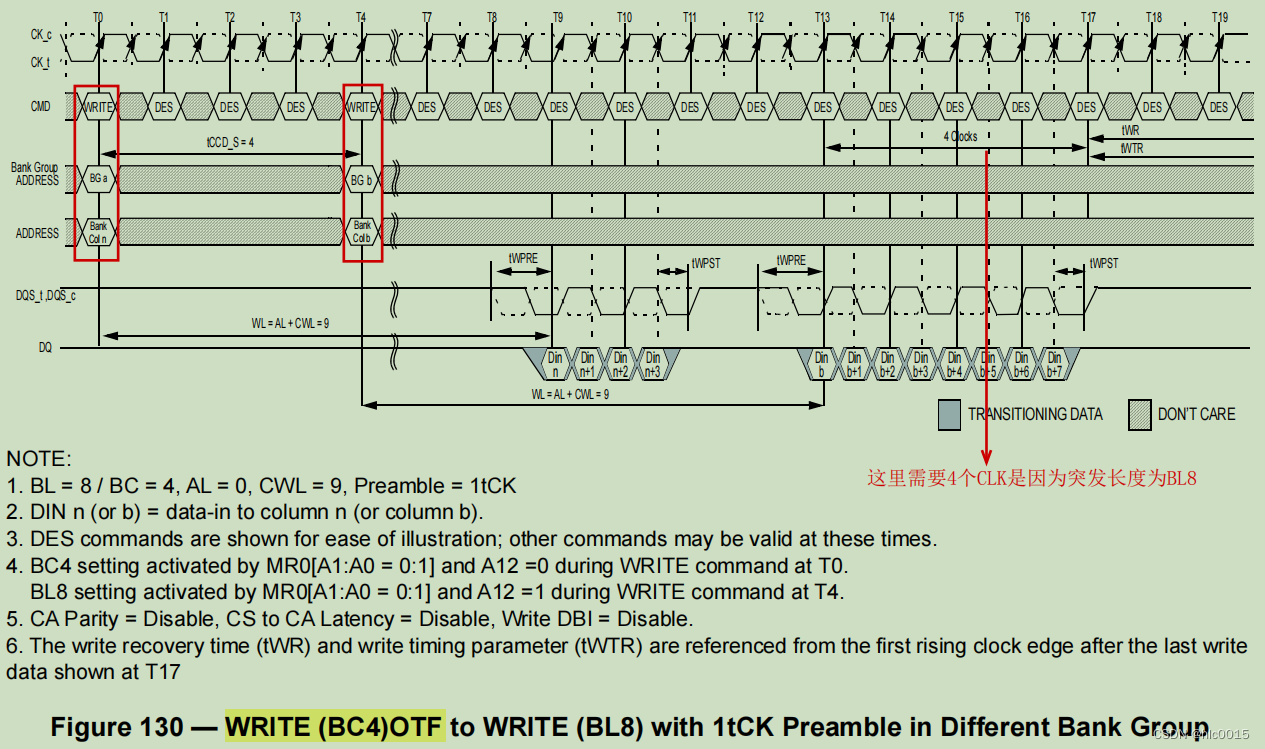

从写到写

图129展示了在不同的BG下,写操作到写操作的时序图,前者突发长度为BL8,后者突发长度为BC4(OTF), AL=0, CWL=9, 读写前导为1tCK。

由于突发长度是变化的,故BL8必定不是Fixed BL8,即BL8由MR0 A[1:0]=01 && A12=1来确定;BC4由MR0 A[1:0]=01 && A12=0确定。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写时序参数tWTR以T17时刻为起点。

图130展示了在不同的BG下,写操作到写操作的时序图,前者突发长度为BC4(OTF),后者突发长度为BL8。AL=0, CWL=9, 读写前导为1tCK。

由于突发长度是变化的,故BL8必定不是Fixed BL8,即BL8由MR0 A[1:0]=01 && A12=1来确定;BC4由MR0 A[1:0]=01 && A12=0确定。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写时序参数tWTR以T17时刻为起点。

第二个突发操作之前,需要插入写前导。

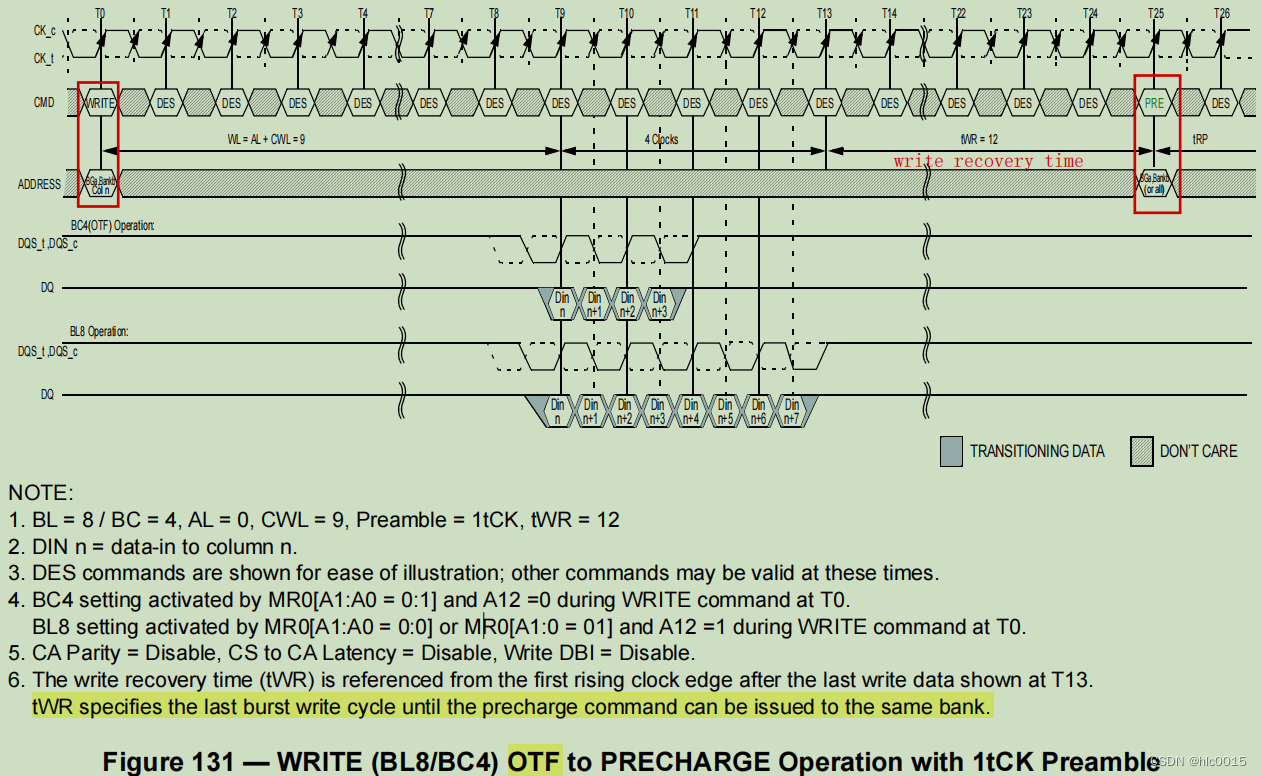

关于Precharge

图131展示了写操作之后进行precharge操作,其中写操作的突发长度可以为BL8,也可以为BC4(OTF)。AL=0, CWL=9, tWR=12,写前导为1tCK。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

BC4的设置必须为OTF,MR0的A[1:0]=01,A21=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时序tWR从T13时刻开始,即写操作的最后一个数据之后的第一个CK上升沿。tWR终点为T25,此刻是对同一个bank进行预充电操作。

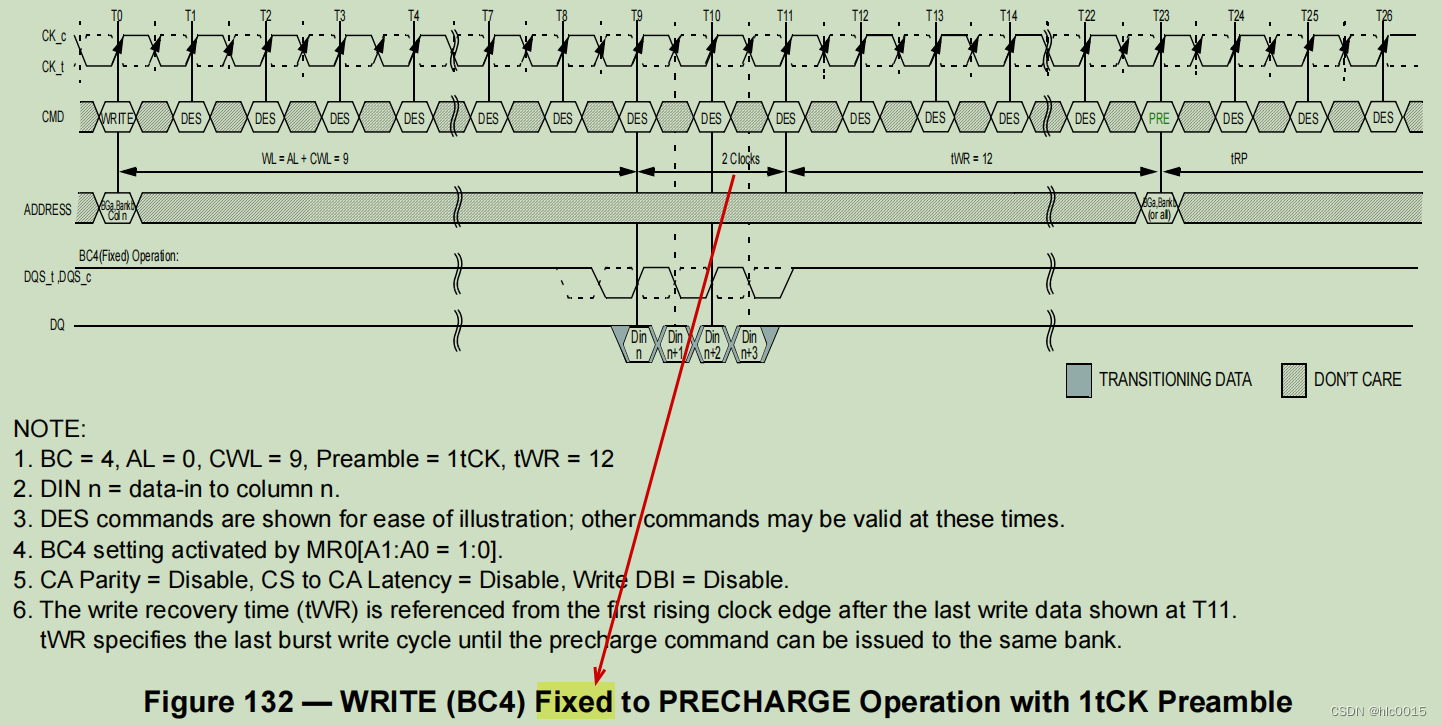

图132展示了写操作之后进行precharge操作,其中写操作的突发长度为BC4(Fixed)。AL=0, CWL=9, tWR=12,写前导为1tCK。

BC4的设置必须为Fixed,MR0的A[1:0]=01。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时序tWR从T11时刻开始,即写操作的最后一个数据之后的第一个CK上升沿。tWR终点为T23,此刻是对同一个bank进行预充电操作。

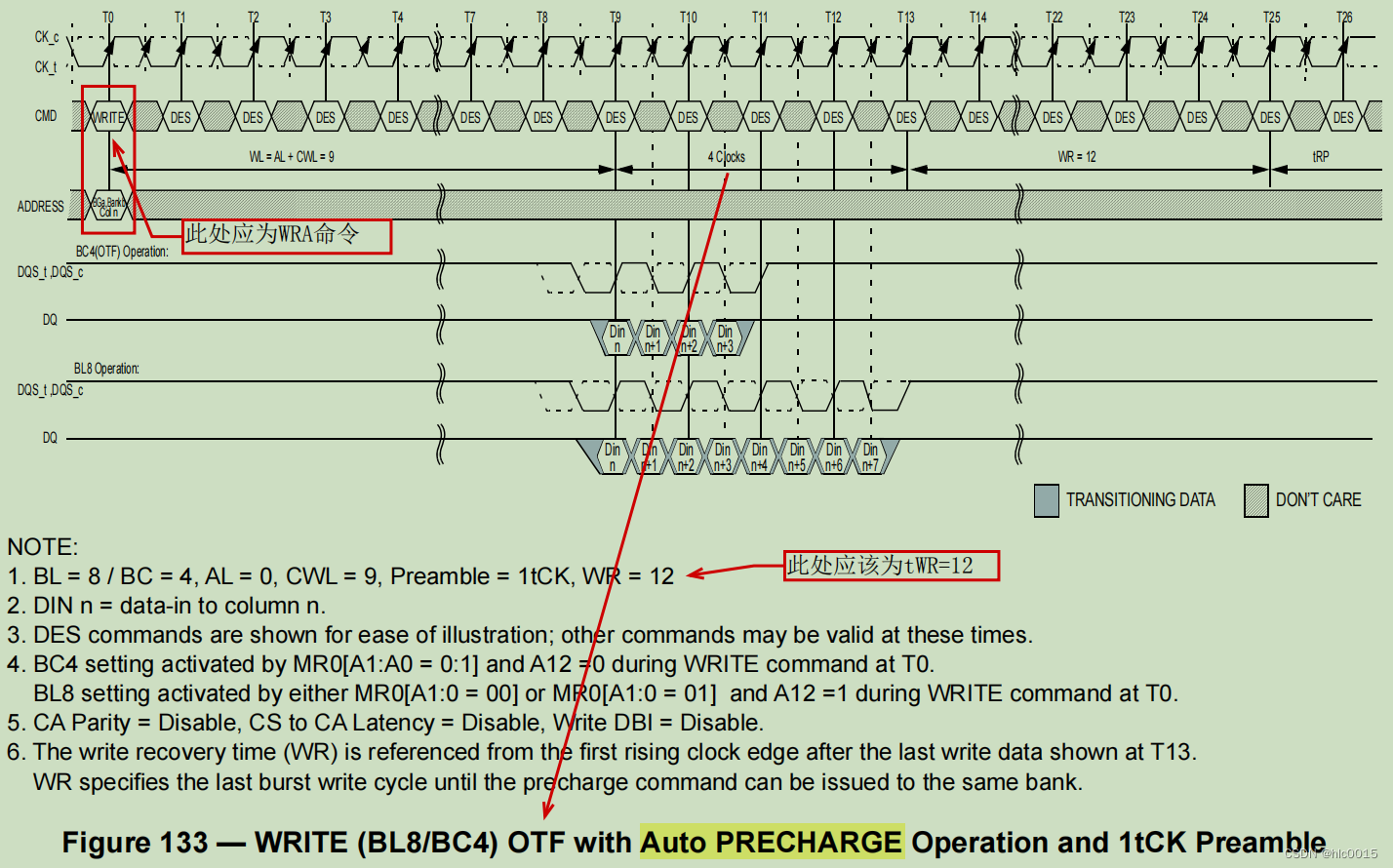

图133与图131类似,只不过并没有主动在T25时刻发送PRE命令,而是在写操作时发送的WRA(带auto precharge的写操作)。所有时序均和图131相同。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

BC4的设置必须为OTF,MR0的A[1:0]=01,A21=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时序tWR从T13时刻开始,即写操作的最后一个数据之后的第一个CK上升沿。tWR终点为T25,此刻是对同一个bank进行预充电操作。

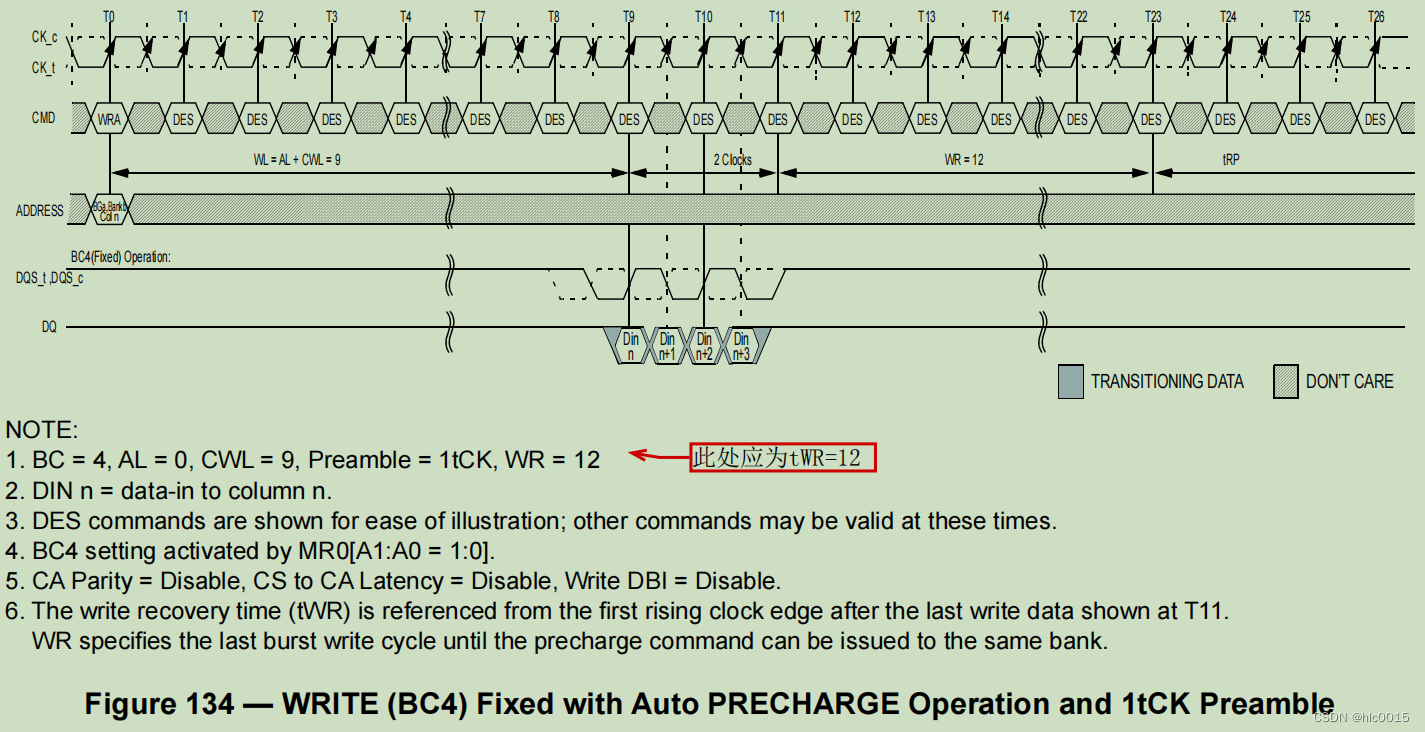

同理,图134与图132类似,在T23时刻并未主动发送PRE命令,而是在写操作时发送 了WRA命令。

BC4的设置必须为Fixed,MR0的A[1:0]=01。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时序tWR从T11时刻开始,即写操作的最后一个数据之后的第一个CK上升沿。tWR终点为T23,此刻是对同一个bank进行预充电操作。

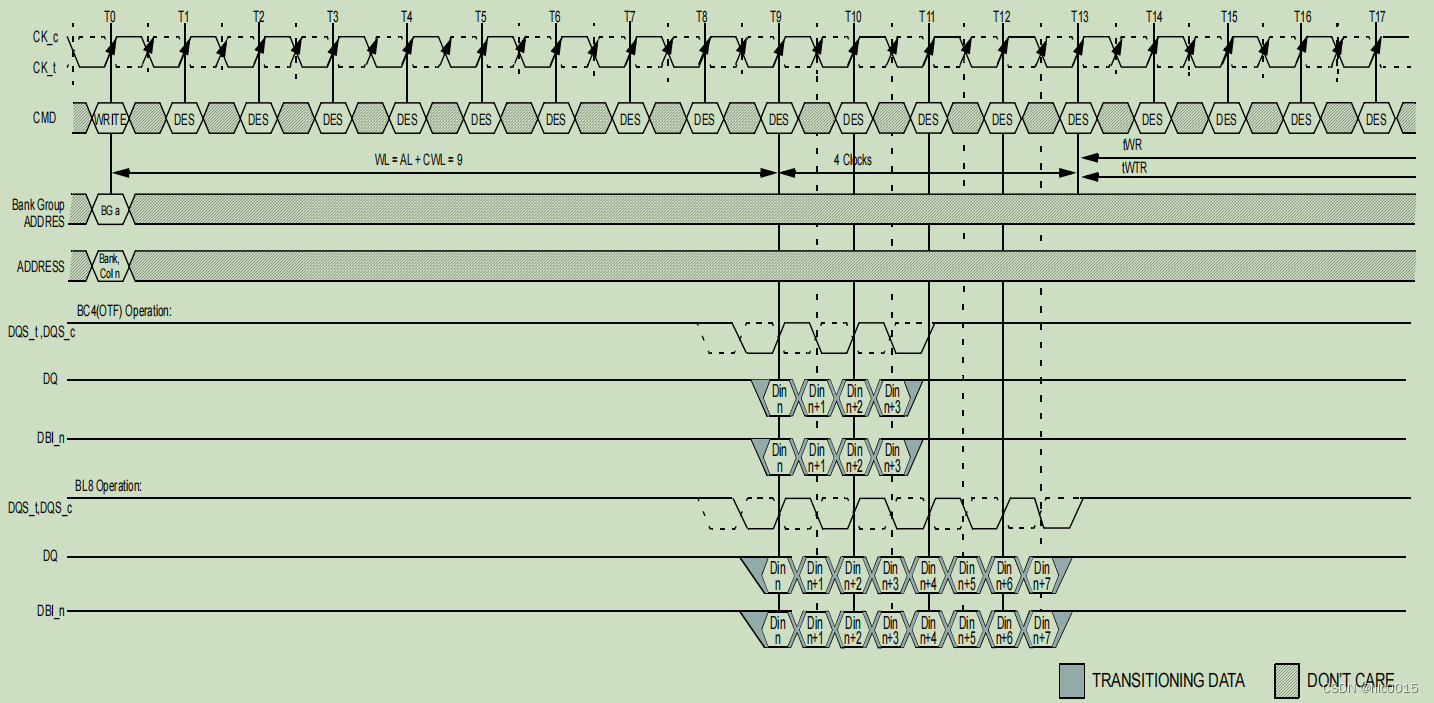

关于DBI

图135展示了带有DBI的写操作,写突发长度可以为BL8,也可以为BC4(OTF),AL=0, CWL=9, 写前导1tCK。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

BC4的设置必须为OTF,MR0的A[1:0]=01,A21=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Enable, CRC = Disable.

写恢复时间tWR_DBI和写时序参数tWTR_DBI从T13时刻开始计算。

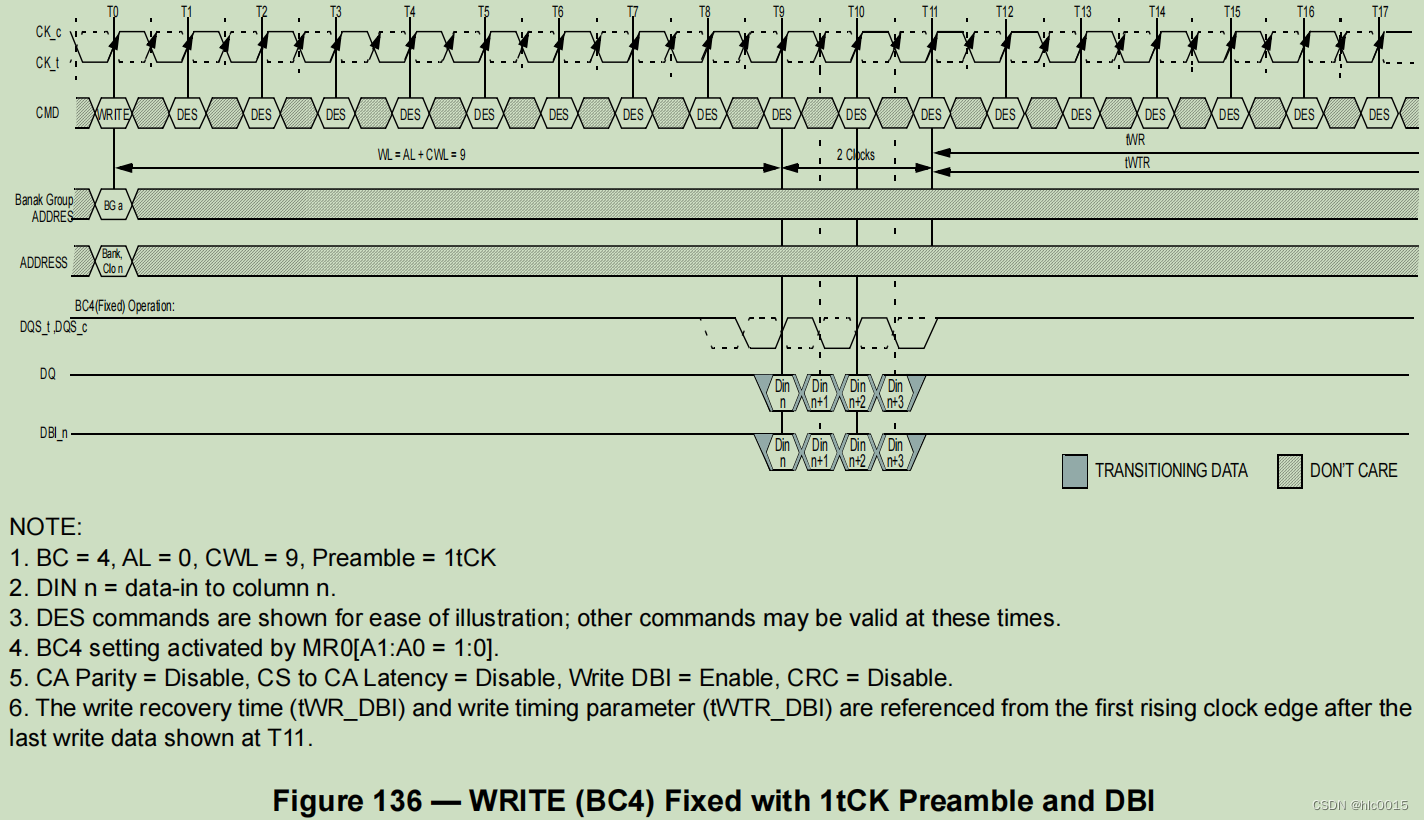

图136展示了带有DBI的写操作,写突发长度为BC4(Fixed),AL=0, CWL=9, 写前导1tCK。由于为BC4 Fixed,故写4个数据只需两个CK周期。

BC4的设置必须为Fixed,MR0的A[1:0]=10。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Enable, CRC = Disable.

写恢复时间tWR_DBI和写时序参数tWTR_DBI从T11时刻开始计算。

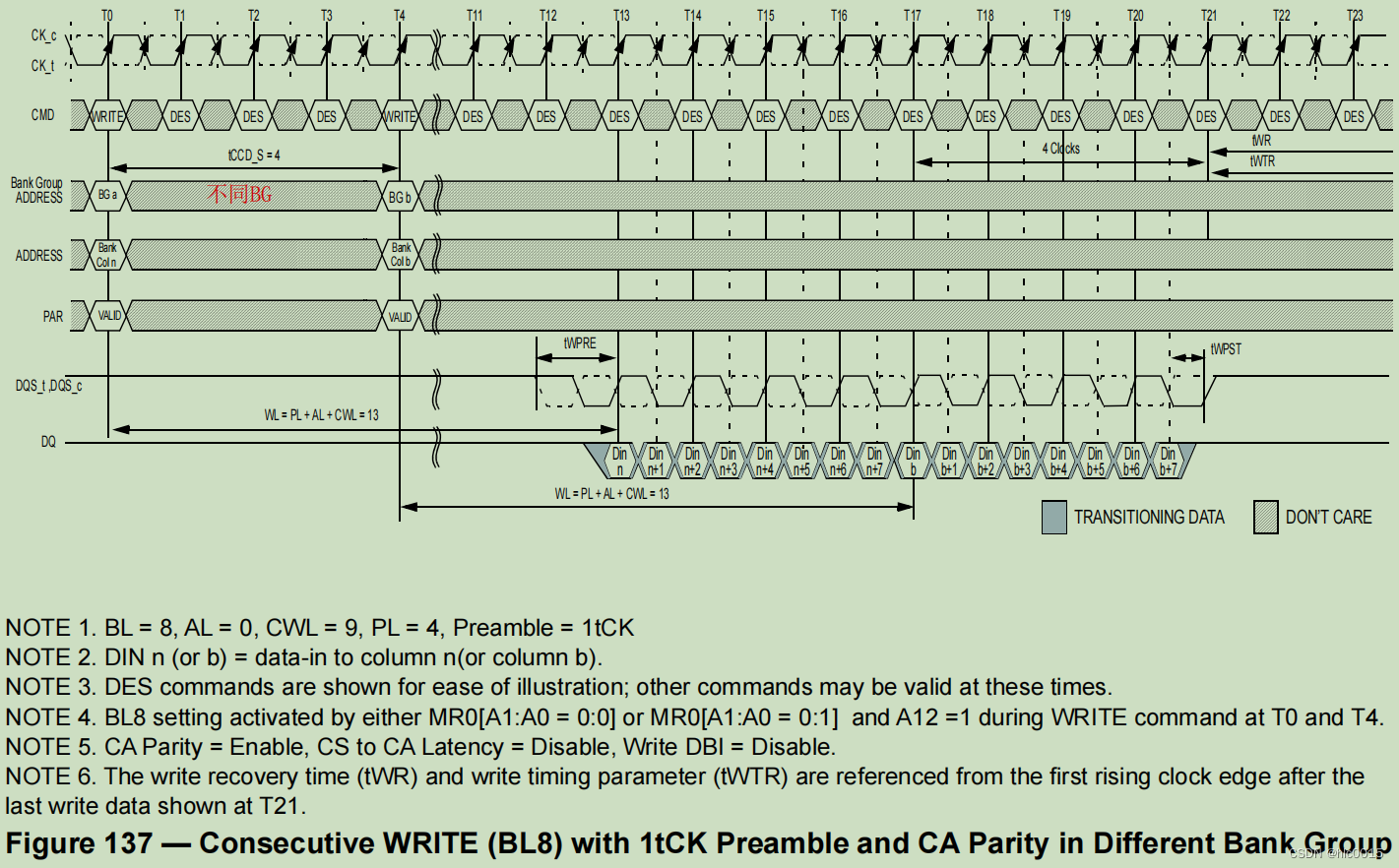

关于CA Parity

下图展示了带有CA Parity的写操作,对不同的BG进行写操作。BL=8,AL=0, CWL=9, PL=4, 写前导为1tCK。WL=PL+AL+CWL=13。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

CA Parity = Enable, CS to CA Latency = Disable, Write DBI = Disable.

写恢复时间tWR和写时序参数tWTR从T21时刻开始算起。

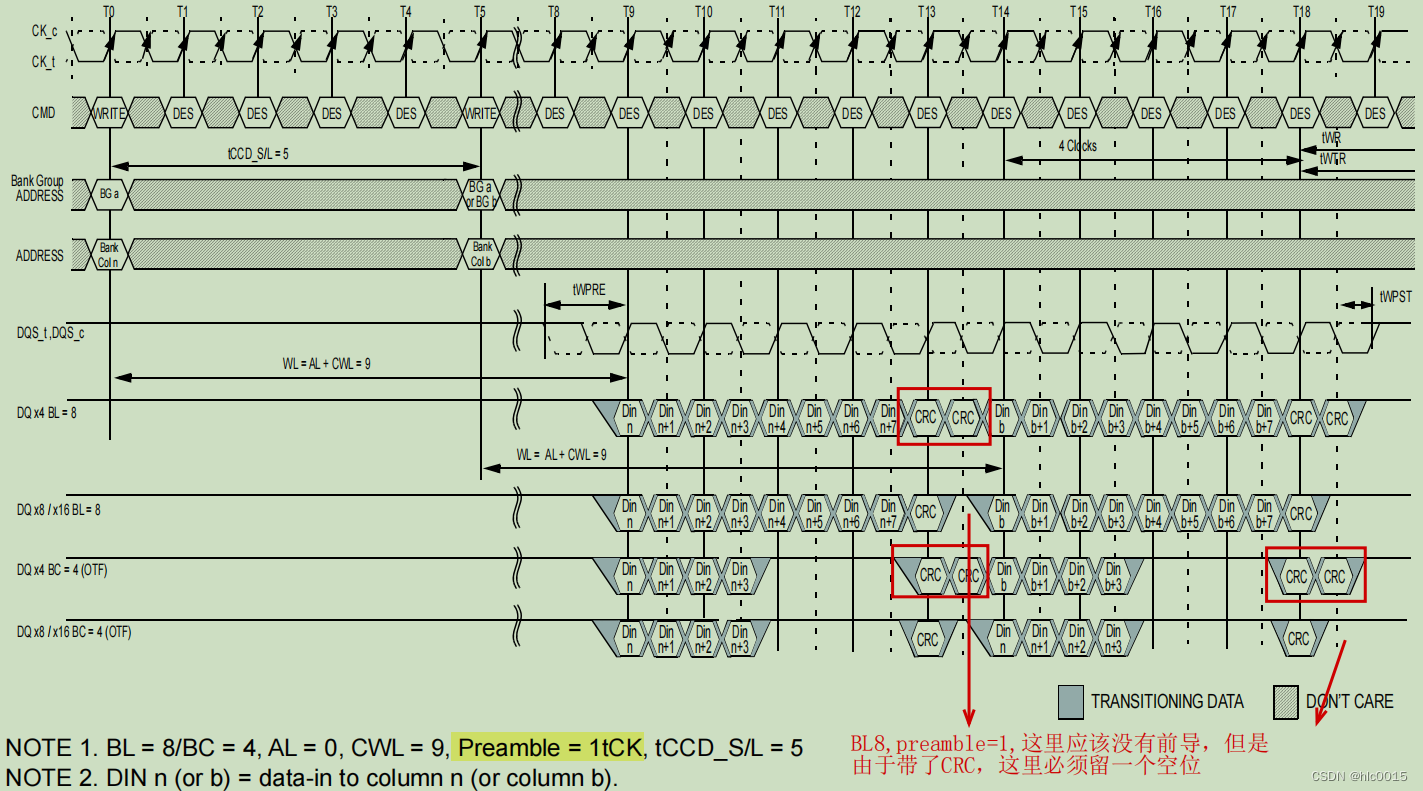

关于CRC

图138展示了不同器件下开启CRC的时序图。由于有了CRC,故tCCD>=5,否则无法在DQ数据线上插入CRC信息。由于此时tCCD的取值为最小值5,故此时的两个写操作为连续写操作;同时,由于tCCD=5,故两个写操作的位置可以为相同的BG,也可以为不同的BG。AL=0, CWL=9, 写前导为1tCK。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

BC4的设置必须为OTF,MR0的A[1:0]=01,A12=0。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable, Write CRC = Enable.

写恢复时间tWR和写时序参数tWTR从T18时刻算起。CRC数据并不算突发传输的最后一个数据。

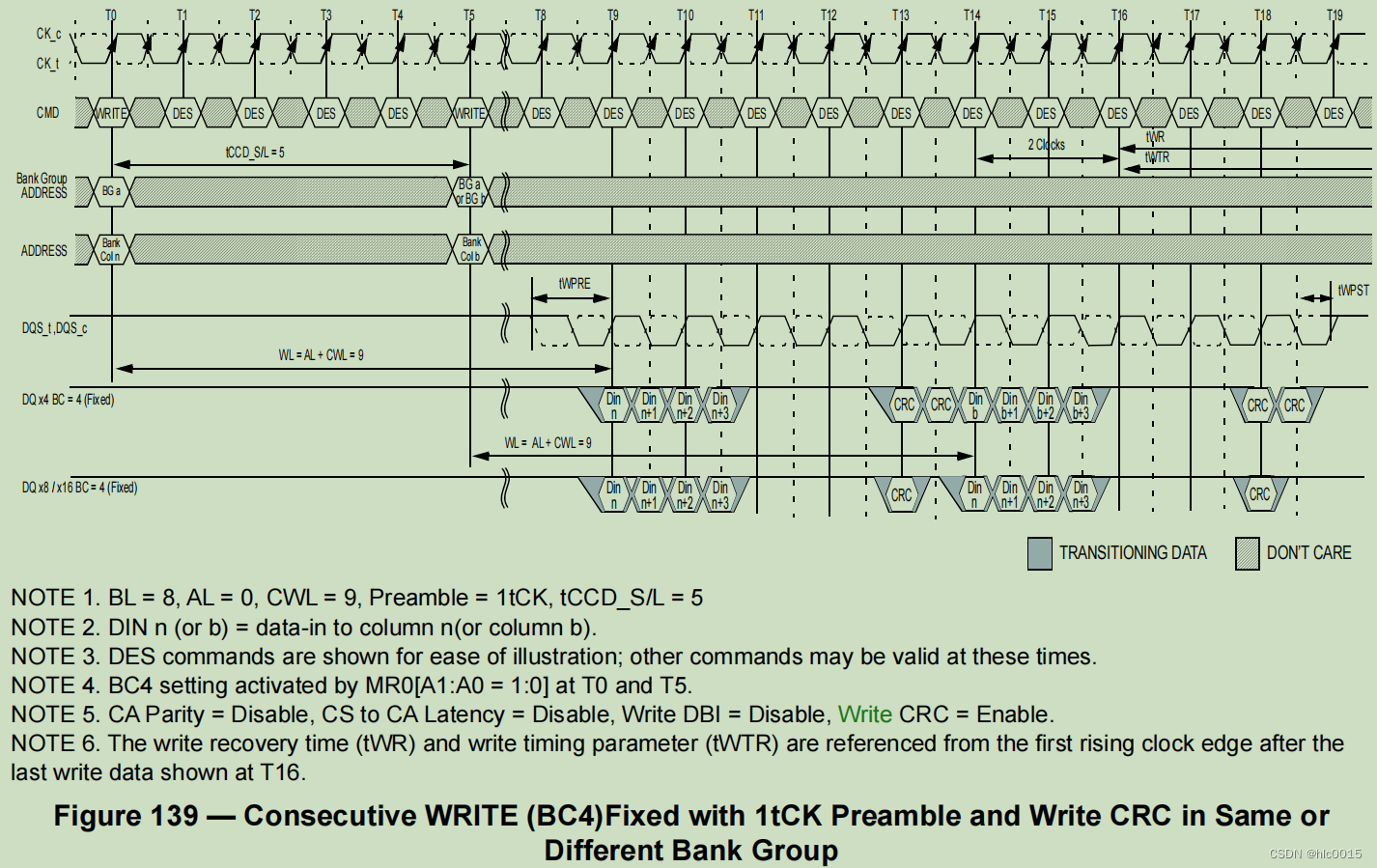

图139展示了不同器件下,开启CRC后,两个写操作突发长度为BC4(Fixed)的时序图。由于此时tCCD的取值为最小值5,故此时的两个写操作为连续写操作;同时,由于tCCD=5,故两个写操作的位置可以为相同的BG,也可以为不同的BG。AL=0, CWL=9, 写前导为1tCK。

BC4的设置必须为Fixed,MR0的A[1:0]=10。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable, Write CRC = Enable.

写恢复时间tWR和写时序参数tWTR从T16时刻算起。CRC数据并不算突发传输的最后一个数据。

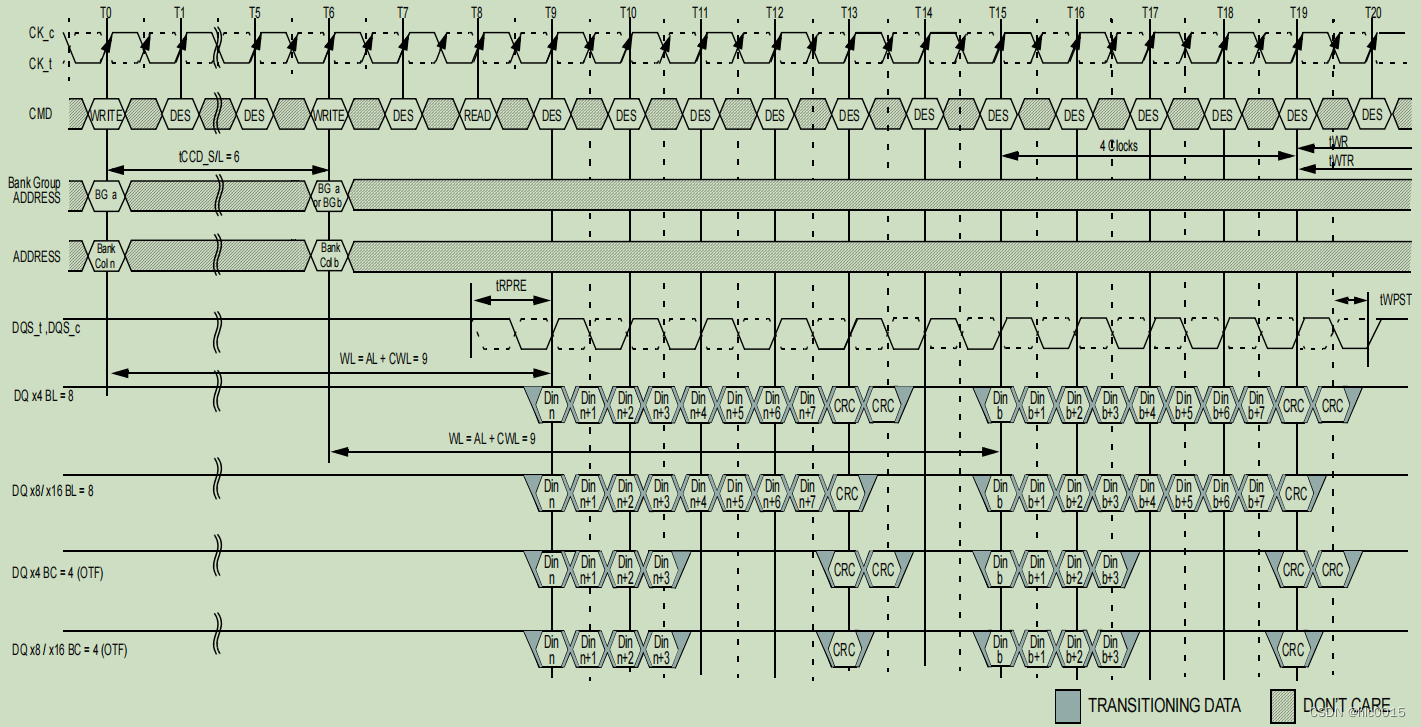

图140展示了不同器件下,开启CRC后,两个写操作的时序图。突发长度可以为BL8,也可以为BC4(OTF),tCCD=6(6大于最小值5,故此时为不连续的写)。写操作对应的BG可以为同一BG,也可以为不同BG。AL=0, CWL=9, 写前导为1tCK。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

BC4的设置必须为OTF,MR0的A[1:0]=01,A12=0。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable, Write CRC = Enable.

写恢复时间tWR和写时序参数tWTR从T19时刻算起。CRC数据并不算突发传输的最后一个数据。

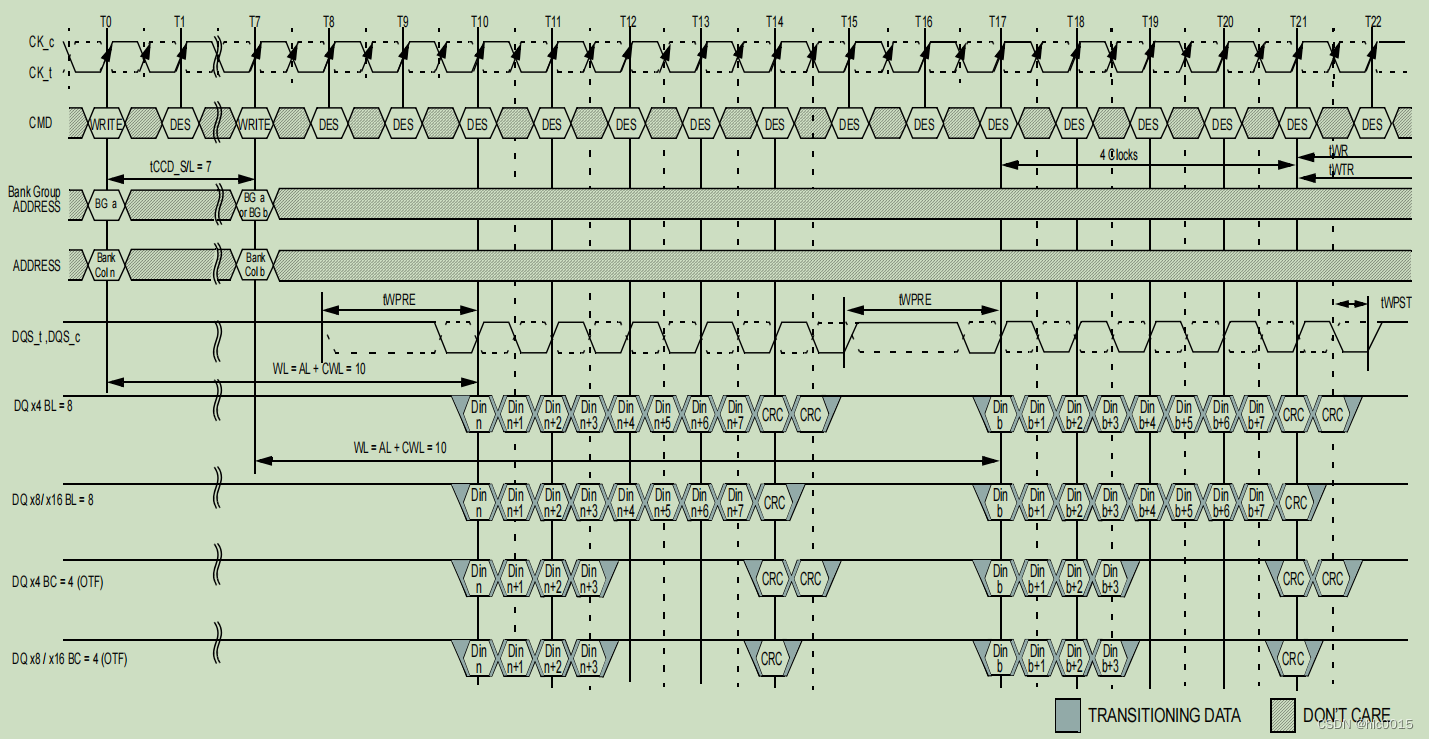

图141与图140类似,只不过将写前导改为了2tCK。由于增加了一个tCK,故tCCD=6+1=7。AL=0, CWL=9+1=10, 写前导为2tCK。由于写前导为2tCK,故CWL必须比其最小值大1,故CWL=10。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

BC4的设置必须为OTF,MR0的A[1:0]=01,A12=0。

C/A Parity = Disable, CS to C/A Latency = Disable, Write DBI = Disable, Write CRC = Enable.

写恢复时间tWR和写时序参数tWTR从T21时刻算起。CRC数据并不算突发传输的最后一个数据。

关于CRC和DM

图142展示了在不同器件下,将CRC和DM都开启时的写操作时序图。AL=0, CWL=9, 写前导1tCK。图中有一个关键信息,即BC4为Fixed模式时,其CRC数据所在的位置依旧与BC4(OTF)的位置一样。

BL8的设置可以为MR0的A[1:0]=00,也可以为MR0 A[1:0]=01 && A12=1。

BC4的设置可以为MR0的A[1:0]=10,也可以为MR0 A[1:0]=01 && A12=0。

CA Parity = Disable, CS to CA Latency = Disable, Write DBI = Disable, Write CRC = Enable, DM = Enable.

写恢复时间tWR和写时序参数tWTR从T13时刻算起。CRC数据并不算突发传输的最后一个数据。

4.25.6 读写命令的间隔

表53展示了从读到写和从写到读的时序间隔。读写操作分为了在同一BG下读写,和在不同BG下读写。

4.25.7 写时序违例

4.25.7.1 Motivation(此处翻译成“动机”应该不合适)

通常来说,如果写操作的时序参数出现违例,则之后会进行复位流程,或者初始化流程来确保DRAM工作正确。然而,对于下述的违例,DRAM是不会宕机的,并且这些违例/错误仅限于这些特定的操作。

下列特定操作中,假设写命令本身(包括ODT等)没有时序违例,且满足下面没有提到的所有的时序要求。

4.25.7.2 数据建立时间和保持时间违例

如果data到data strobe的时序出现违例,即Tdqs_off, Tdqh_off, Tdqs_dd_off, Tdqh_dd_off违例,则该burst操作中,DRAM将会被写入错误的数据,如图114所示。图中,相应的data strobe edge与对应的CK边沿的时刻为T9, T9.5, T10, T10.5, T11, T11.5, T12, T12.5。

后续读取该位置的读操作可能会出现不可预测的数据,但是整个写和读操作中,DRAM依旧是正常工作的。

4.25.7.3 Strobe时序违例和Strobe到CK的时序违例

对于突发写操作,如果strobe的时序违例(即tDQSH, tDQSL, tWPRE, tWPST时序违例),或者strobe到时钟的时序违例(即tDSS, tDSH,

tDQSS时序违例),错误的数据将会被写入DRAM。后续读取该位置,可能会出现不可预测的读数据。但是,DRAM将在以下约束下正常工作:

- Write CRC和OTF模式都关闭了,且除了tDQSH, tDQSL, tWPRE, tWPST, tDSS, tDSH, tDQSS时序违例外,没有其它的时序违例;

- 从write latency结束的地方开始,违规的写strobe信号(以及写前导)不能早于或晚于6个DQS的变化沿到来。

- 此错误的写操作之后可以发送读命令,可以读任何open的bank。

- 在错误的写操作之后的tCCD_L时序之后,发送一个或多个WR命令或发送一个WRA命令(写同一个bank),将会导致写入错误的数据;再后续的WR和WRA命令写入DRAM中,可能会出错,也可能不会出错(subsequent WR and WRA can be either offending or non-offending Writes)。从这些写入的地方读数据可能会出错。

- 在错误的写操作之后,再过tCCD_S后,对另一个bank(不同于错误写操作的bank)发送一个或多个WR,或者发送一个WRA命令,都会导致错误的数据被写入;再后续的WR和WRA命令写入DRAM中,可能会出错,也可能不会出错(subsequent WR and WRA can be either offending or non-offending Writes)。从这些写入的地方读数据可能会出错。

- 在错误的写操作后发送一个或多个precharge命令(PRE或PREA),则后续的写操作将会写入正确的数据。

本文详细阐述了DDR4内存中关于写操作的时序参数,包括WriteDM、tWPRE和tWPST的计算方法,突发写操作的不同类型,以及从写到读和写到写的时序间隔。此外,还讨论了预充电、DBI、CAParity、CRC等相关时序和异常处理情况。

本文详细阐述了DDR4内存中关于写操作的时序参数,包括WriteDM、tWPRE和tWPST的计算方法,突发写操作的不同类型,以及从写到读和写到写的时序间隔。此外,还讨论了预充电、DBI、CAParity、CRC等相关时序和异常处理情况。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?