手册4.32和4.33章节主要讲述了封装后修复的内容,之前在印象笔记中记录了Post Package Repair(PPR)的笔记,现在搬运至此,作为补充。

PPR全称为Post Package Repair,中文直译为封装后修复,其意为当一个row损坏后,利用算法将损坏的row映射到冗余的row上,利用冗余的row来进行数据传输。PPR有两种修复方式,一种为hPPR,一种为sPPR。

hPPR为硬件修复,修复后不可更改,内存控制器需要记录此次修复,因为此次修复无法更改,坏道已经映射到了冗余的通道上,若下次再发送相同的hPPR操作,DRAM将无法执行此操作。修复是在硬件层面上的走线更改,好处是修复了这一次后就一劳永逸,掉电后不丢失,重新启动后,不用再次修复。

sPPR为软件修复,是更改颗粒里面的软路由,并且还可以被其它的sPPR命令以及hPPR命令更改。掉电后丢失,且下次启动后发现仍然有坏row,仍然要启动sPPR进行修复。

在DDR4的标准手册中,定义了PPR修复功能在4Gb容量中是可选的,但是8Gb以及8Gb以上的容量,必须配备PPR功能,即配备冗余的row。并且还说明,PPR功能需要视每个内存生产商而定,这给了生产商很大的自由度。

美光PPR与JEDEC PPR不同点

| JEDEC | 美光 |

| 4Gb选配PPR,8Gb及以上标配 | 4Gb及以上标配 |

| 每个bank group中只有一个冗余row | 每个bank中有至少一个冗余row |

| hPPR开始前需复位sPPR的row修复地址 | 不需要此操作 |

| PPR中BG的每个bank都是独立的 |

三星DDR4 PPR

三星的DDR4 datasheet只在Feature中介绍了其产品支持PPR,但是通篇没有对PPR进行介绍。

海力士DDR4 PPR

海力士的DDR4,datesheet中不提及PPR,Feature中也没有对PPR的罗列

参考资料

百度网盘,提取码:s4d5

4.32 封装后修复(硬件级的封装后修复)

在DDR4的标准手册中,定义了PPR修复功能在4Gb容量中是可选的,但是8Gb以及8Gb以上的容量,必须配备PPR功能,即配备冗余的row。并且还说明,PPR功能需要视每个内存生产商而定,这给了生产商很大的自由度。

在hPPR中,DDR4可以对每个BG进行一个Row的修复,也就是说每个BG有一个冗余的Row。内存控制器需对每次hPPR的修复进行记录。

有两种方法可以进行hPPR,一种为利用WRA命令,其后进行REF操作从而保证数据不被改变(正在修复坏道的bank的数据不会被保留,此时BA[0] Don‘t Care)(因为hPPR用时较长,故为了保持DRAM中的数据不丢失,可以在发送WRA命令后发送REF命令)。另一种为直接发送WR命令,不发送REF命令,此情况下,由于没有REF命令,故不能保证DRAM中的数据仍旧能够保持。

当进入hPPR或sPPR模式时,需要通过一系列的MRS设置来避免非法的hPPR/sPPR操作,这个一系列的MRS设置称为Guard Key。

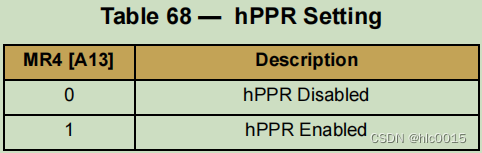

在进入hPPR模式(MR4的A13=1)后需要立即设置4个MRS命令来设置MR0,从而启动Guard Key。在对MR0进行四个连续的MRS命令设置时,不允许其他命令发送,也不允许对其它的MR寄存器进行设置的MRS命令,必须将MR0全部设置完成后,上了锁之后在发送其它命令。假设在设置MR0时被其它命令中断(这个命令称为offending command),或者在设置MR0时未按照规定的顺序进行设置,则不会进入hPPR/sPPR模式,offending command可能会执行错误,offending command不会造成DRAM锁定(lock up)。

另外,当进入hPPR或sPPR的顺序被中断,后续的ACT和WR命令将会被视作正常操作DRAM的命令。如果hPPR操作过早地、贸然地被终止,则发送后续的hPPR或sPPR操作前,MR4的A13必须设置为0;如果sPPR操作过早地、贸然地被终止,则发送后续的sPPR或hPPR操作前,MR4的A5必须被设置为0。如果未能按照规定的顺序启动Guard Key,DRAM并不会提供一个错误指示信号。

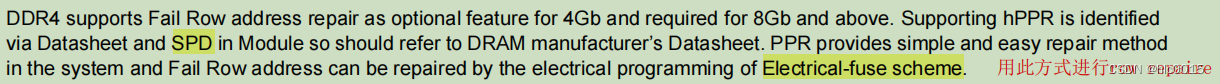

表67展示了进入Guard Key的顺序,MRS需要对MR0进行四次设置。

NOTE3表示,当hPPR和sPPR模式完成后,如果想要读写DRAM,MR0必须保持为进入PPR模式之前的设置。

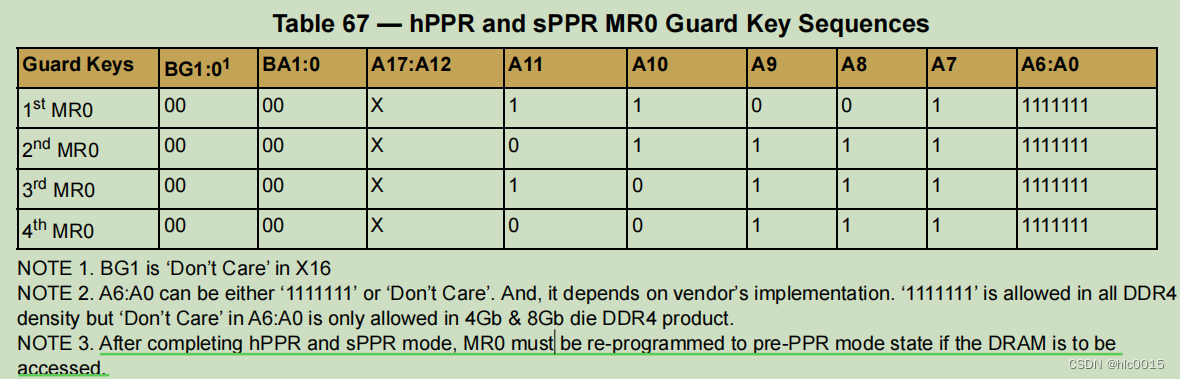

4.32.1 以WRA命令进行hPPR(可以发送REF)

- 在进入hPPR模式之前,所有的bank都必须Precharge;必须关闭DBI和CRC。

- 将MR4的A13设置为1,并等待tMOD时长。

- 启动Guard Key:按表67发送4个MR0的MRS命令,每个MRS命令需等待tMOD时长。

- 在发送ACT命令时指明要修复的Bank和Row地址。写数据用于选择Rank中的具体的DRAM。

- 在tRCD时长后,发送WRA,并跟随一个有效地址。虽然是一个有效地址,但DRAM在此时Don't Care。

- 等待WL后(WL=CWL+AL+PL),修复坏道的DRAM的所有DQ pin将会拉低四个CK周期。如果DRAM的所有DQ持续拉高大于或等于两个CK周期,那么DRAM将不会执行sPPR操作,如果发送了REF命令,DRAM的数据将会保持;如果所有的DQ没有保持四个CK的低电平,也没有保持大于等于两个周期的高电平,则sPPR操作是否执行了未可知。

- 等待tWR时长,DRAM在此时间内会进行内部修复坏道,之后发送PRE命令。

- 在PRE命令后等待20ns。

- 通过设置MR4的A5=0来退出hPPR。

- 对于相同的BG发送多个sPPR请求,最近的sPPR及其对应的地址将会覆盖掉先前发送的地址;对于不同的BG进行sPPR,重复步骤2到9。在发送hPPR前,可以进行sPPR。

- 如果有多个row地址损坏,重复2到9步骤。

图171为上述过程的时序图。

另外,在hPPR模式下,当之前发送的命令为WRA时,后续可以发送REF命令,具体时间为在发送WRA命令后的PL+WL+BL/2+tWR+tRP时间之后,且REF命令需要在tPGM和tPGMPST时间内发送。可以按tREFI时间间隔正常发送REF命令,也可以按照tREFI/2的间隔发送,也可以按tREFI/4的间隔发送,但是时间间隔不能更小了。发送REF命令后,DRAM将会正常执行REF命令,除了正在修复的坏道的bank,其它的bank数据都可以被保留,当然在此过程中BA[0] don't care。在tPGM时间内只允许发送REF命令,否则无法完成hPPR修复。

一旦退出hPPR修复模式,为了验证对应的坏道是否映射到了冗余的通道上,用户可以给对应的坏道进行写数据操作,并将其回读,从而查看是否修复完成。当然,上述操作需要在hPPR退出后的tPGMPST时长后才能进行。

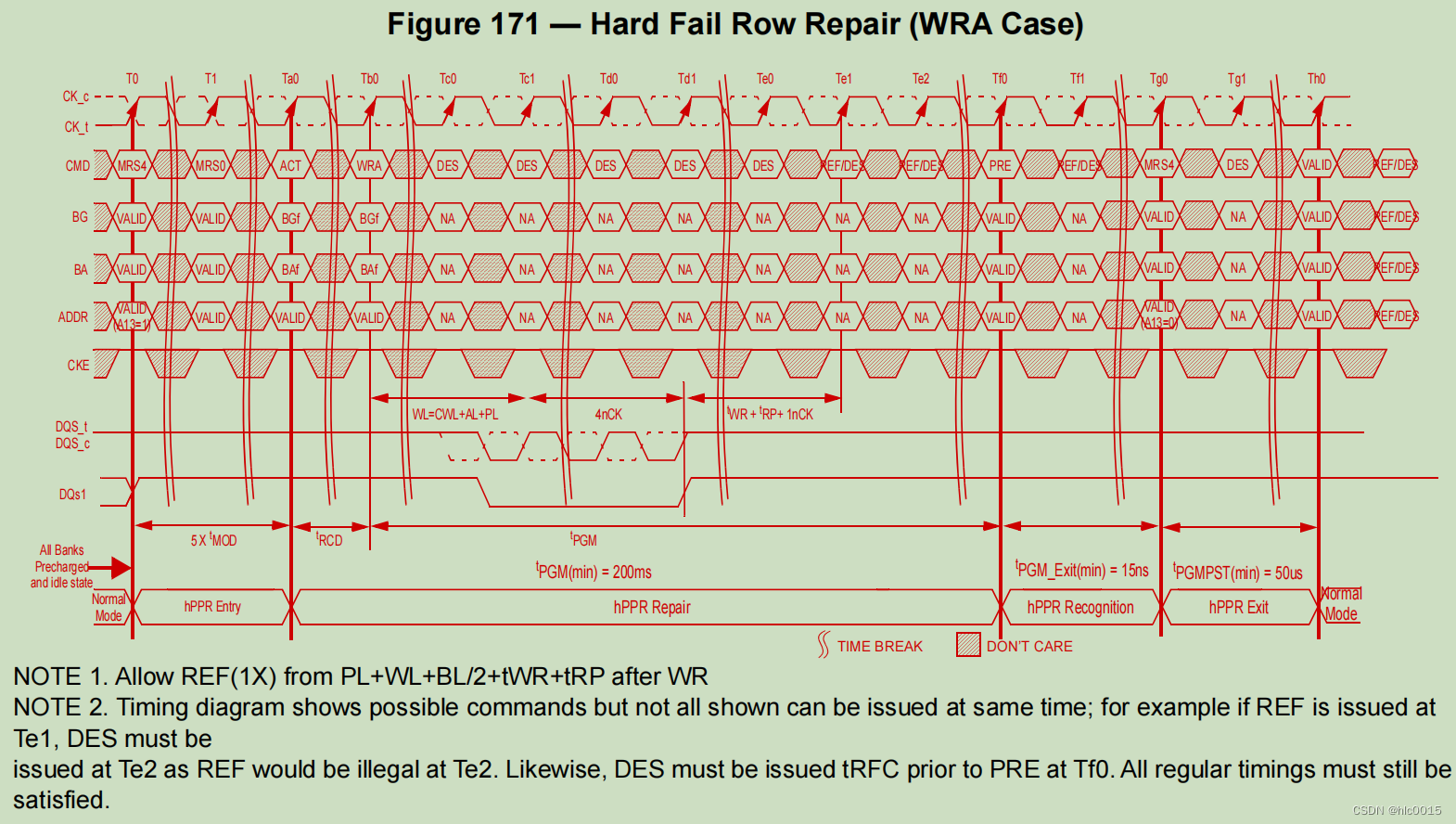

4.32.2 以WR命令进行hPPR(不允许发送REF)

在手册中,4.32.2章节所述的步骤是完全照抄4.32.1章节的步骤,根本没有改动,最主要体现在没有删除第六步的关于REF命令的操作的话语。尽管手册上在步骤11之后的下一段写了一句“不允许REF命令”。

- 在进入hPPR模式之前,所有的bank都必须Precharge;必须关闭DBI和CRC。

- 将MR4的A13设置为1,并等待tMOD时长。

- 启动Guard Key:按表67发送4个MR0的MRS命令,每个MRS命令需等待tMOD时长。

- 在发送ACT命令时指明要修复的Bank和Row地址。

- 在tRCD时长后,发送WR,并跟随一个有效地址。虽然是一个有效地址,但DRAM在此时Don't Care。

- 等待WL后(WL=CWL+AL+PL),修复坏道的DRAM的所有DQ pin将会拉低四个CK周期。如果DRAM的所有DQ持续拉高大于或等于两个CK周期,那么DRAM将不会执行hPPR操作;如果所有的DQ没有保持四个CK的低电平,也没有保持大于等于两个周期的高电平,则hPPR操作是否执行了未可知。

- 等待tPGM时长,DRAM在此时间内会进行内部修复坏道。发送PRE命令。

- 在PRE命令后等待tPGM_Exit时长。

- 通过设置MR4的A13=0来退出hPPR。

- 在tPGMPST时间后,DDR4可以正常操作。

- 如果有多个row地址损坏,重复2到9步骤。

在上述操作中,在进入hPPR后和退出hPPR模式前不允许发送REF命令。

一旦退出hPPR修复模式,为了验证对应的坏道是否映射到了冗余的通道上,用户可以给对应的坏道进行写数据操作,并将其回读,从而查看是否修复完成。当然,上述操作需要在hPPR退出后的tPGMPST时长后才能进行。

图172为上述时序过程。

4.32.3 MR bit的指示

4.32.4 通过MPR0 Page2确定DRAM是否支持hPPR/sPPR

如题,当支持hPPR时,MPR Page2中的bit7=1,不支持hPPR时,bit7=0;当支持sPPR时,MPR Page2中的bit6=1,不支持sPPR时,bit6=0。

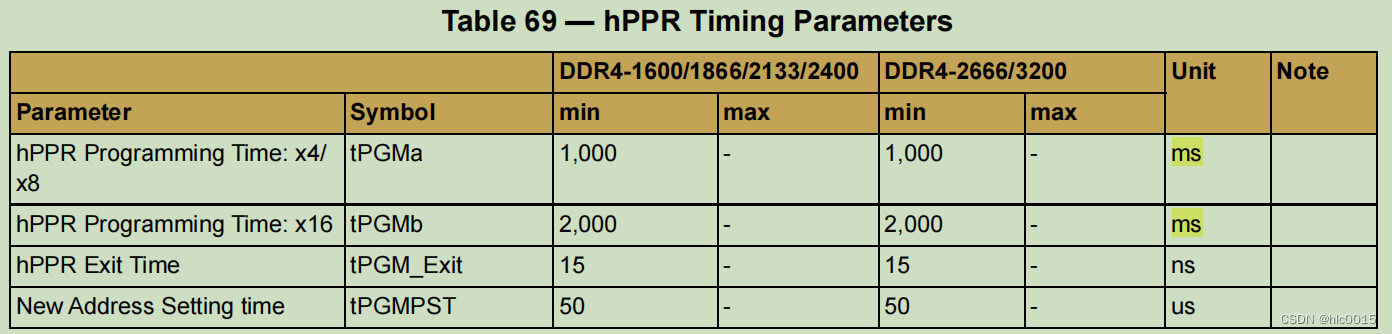

4.32.5 要求的时序参数

如表69所示。

4.33 封装后修复(软件级的封装后修复)

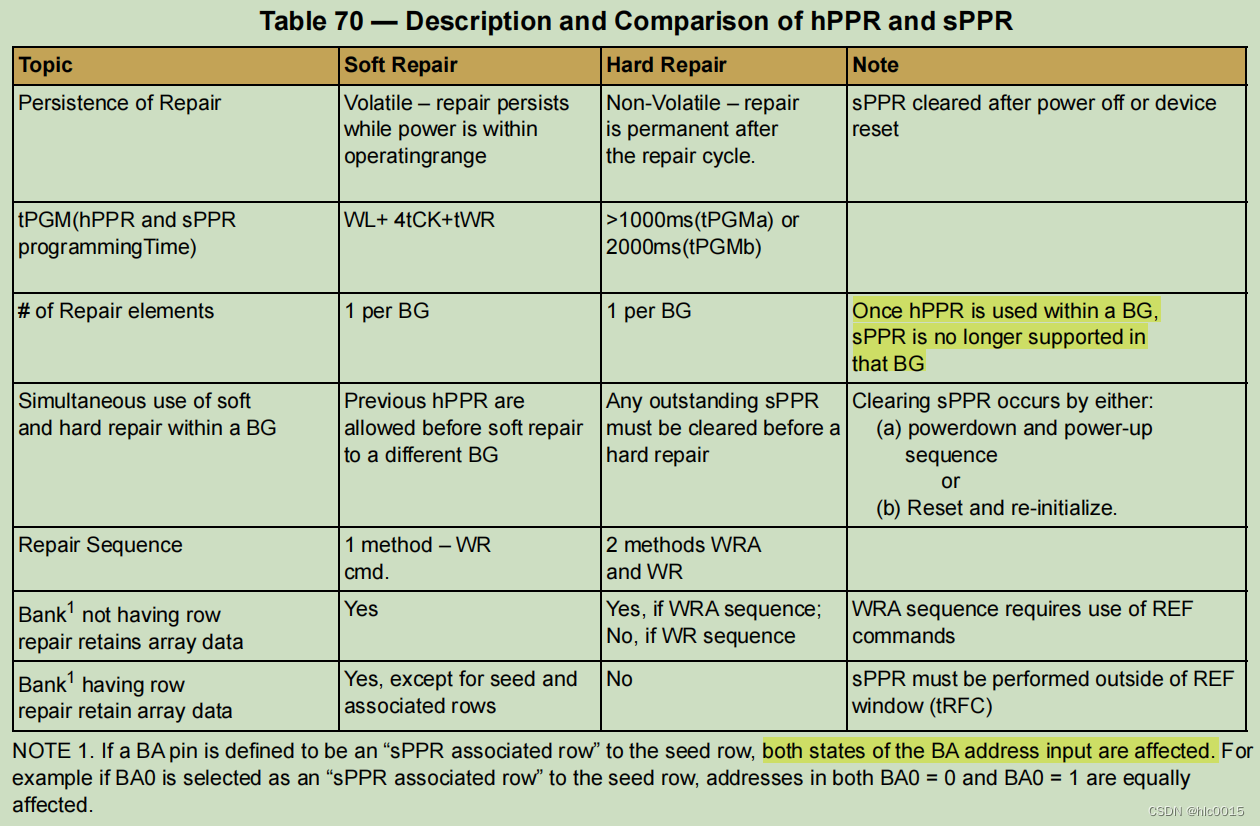

相较于hPPR,sPPR修复所需的时间更短,但其并不像hPPR一样修复之后一劳永逸,sPPR修复后,掉电或者复位操作,会丢失修复的结果。表70展示了两者之间的联系与区别。

表格的翻译如下:

| Topic | sPPR | hPPR | Note |

| 修复后可保持的时间 | 非永久性修复 | 永久性修复 | 在下电或复位后,sPPR的修复信息会被丢失 |

| tPGM,修复所需时间 | WL+4tCK+tWR | >1000ms(tPGMa) >2000ms(tPGMb) | |

| 每个BG可修复的row | 1个row/BG | 1个row/BG | |

| 在同一BG内同时使用sPPR和hPPR | 在sPPR对另一不同的BG进行修复前,可以发送hPPR(这个框里的内容总感觉与Topic不一致) | 在进行hPPR之前需清除sPPR的信息。 | 清除sPPR有两种方式

|

| 修复所需的方式 | 发送WR命令 | 发送WRA或WR命令 | |

| 未进行修复的bank在修复期间是否能保留原有数据 | 可以 |

| WRA命令需要配合REF命令一起使用 |

| 需要修复的bank在在修复期间是否能保留原有数据 | 可以,除了需要修复的row不能保留原有数据。 | 无法保留 | sPPR需要在REF发送后的tREF时长后进行 |

NOTE1中的seed row为需要修复的row。NOTE1还是不知如何翻译。

sPPR借助MR4的A5进入sPPR,与hPPR相同,sPPR也需要表67所述的Guard Key来让sPPR成功执行。在进入sPPR之前,需要发送hPPR退出命令以及sPPR退出命令。计入sPPR后,需要发送ACT命令来确定目标bank以及需要修复的目标row。在tRCD时序后,可以发送WR命令进行修复。经过写恢复时间和PRE所需的时间后,可以退出sPPR模式,之后便可对DRAM进行正常操作。只要VDD电压保持在正常的工作范围内,则DRAM将会保留sPPR修复的结果。如果DRAM掉电,或DRAM进行了复位,则sPPR修复的结果将会丢失。在进入hPPR模式前,必须通过下电操作或复位后重新初始化的操作来清除sPPR的修复结果。

DDR4的sPPR可以对每个BG进行一个row的修复,然而,当hPPR修复占用了BG中这个冗余row的资源,那么将不能再使用sPPR对此BG进行修复。如果BG中的冗余row已经被占用了,也就是说没有可供利用的row进行hPPR或sPPR修复,则DRAM将会忽略对该BG发送的PPR操作。对于4Gb和8Gb容量的DRAM,sPPR是选配的,但是对于大于8Gb的DRAM,必须配备sPPR模式。

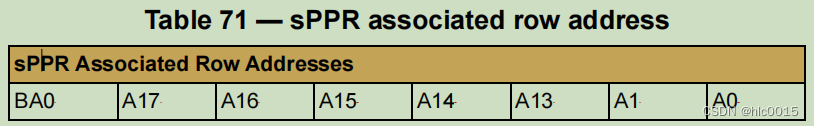

当接收到sPPR时,除了需要修复的目标row以及associated row,bank将会保存DRAM其它阵列中的数据(此对于大于8Gb的DRAM是这样的,对于小于等于8Gb的DRAM,这种情况是可选的)。如果用户并不要求在sPPR下保存阵列中的数据,则对associated row的操作会被忽略。如果要求将数据保存在bank中,则在执行sPPR之前,目标row和associated row应该备份起来并在sPPR结束后恢复其存储的数据(具体如何操作,手册上未提及)。sPPR的associated row地址如下表所示。

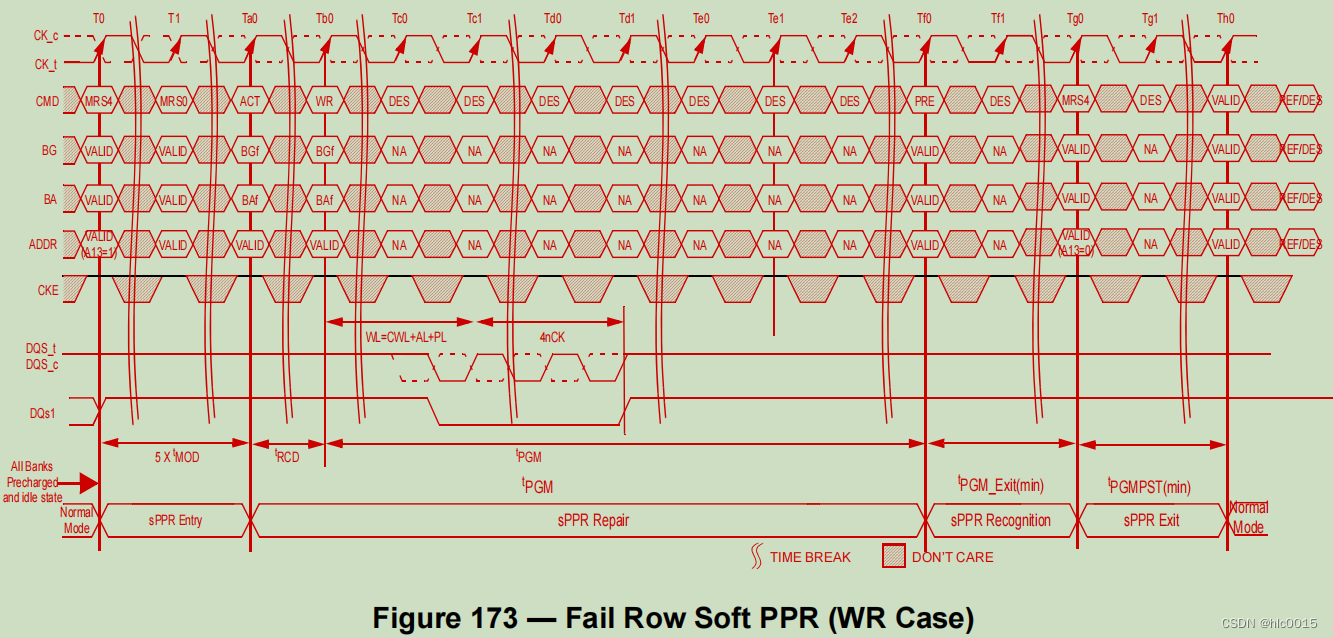

4.33.1 sPPR操作流程

在sPPR操作器件,不允许发送REF命令。

- 在进入sPPR模式之前,所有的bank都必须Precharge;必须关闭DBI和CRC。

- 将MR4的A5设置为1,并等待tMOD时长。

- 启动Guard Key:按表67发送4个MR0的MRS命令,每个MRS命令需等待tMOD时长。

- 在发送ACT命令时指明要修复Bank和Row地址。

- 在tRCD时长后,发送WR,并跟随一个有效地址。虽然是一个有效地址,但DRAM在此时Don't Care。

- 等待WL后(WL=CWL+AL+PL),修复坏道的DRAM的所有DQ pin将会拉低四个CK周期。如果DRAM的所有DQ持续拉高大于或等于两个CK周期,那么DRAM将不会执行sPPR操作;如果所有的DQ没有保持四个CK的低电平,也没有保持大于等于两个周期的高电平,则sPPR操作是否执行了未可知。

- 等待tWR时长,DRAM在此时间内会进行内部修复坏道。发送PRE命令。

- 在PRE命令后等待20ns。

- 通过设置MR4的A5=0来退出sPPR。

- 在对BG进行hPPR之前可以进行sPPR操作。当多个sPPR请求发送到同一个BG,则最后的一个sPPR对应的地址将会覆盖之前的地址。对于不同的BG进行sPPR操作,重复步骤2到9。

退出sPPR后,为了验证其是否修复完成,可以写数据并读数据来进行确认。图173为sPPR的时序。

1327

1327

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?