FPGA的调试过程是一个迭代过程,会不断的发现bug,然后编译,再调试。调试过程中最耗时间的可能往往是编译,即使是一个小的改动都需要对工程进行一次重编译,所以如何减少工程编译时间是提高工作效率的关键之一。

主要可以通过以下几个方面减少编译时间,电脑配置、文件引用、增量编译和编译策略。

1 电脑配置

电脑配置越好,编译时间越短,这一点是毋庸置疑的。

另外需要注意的是,在编译的时候尽量关闭其他占用CPU和内存较大的应用,否则编译软件会和这些应用抢资源。

如果实在不能关闭,而又需要减少编译时间,可在进程中找到编译的进程,右键选择设置优先级 > 提高编译进程的优先级,这样计算机会将CPU和内存资源向编译过程倾斜,达到减少编译时间的目的。

2 文件引用

在建立FPGA工程的时候需要将源文件加入到工程中,包括.v、.vhd、.sv文件、约束文件及IP核等文件。如果工程中加入了非常多的无效文件(没有用到的文件),也会增加编译时间,因为综合工具需要去分析这些文件是否有用。

下图是同一个工程,在清理了无效文件之后的编译时间与原工程的对比,可以看到清理了无效文件之后,编译时间减少了很多。当然这也与该工程包含了太多无效文件有关,如果无效文件并不是很多的话,效果则不会很明显。

环境是Quartu II 14.1,将.qsf(quartus setting file)文件中无效的引用全部删除或者注释。

3 增量编译

相对于上面两个方法,增量编译更有效,更具有操作性。这里主要讲Quartus软件的增量编译,包括Smart Compile、Rapid Recompile和Design Partition。

Note: 某些器件或者Quartus版本不支持Smart Compile或Rapid Recompile。如Arria10器件不支持Smart Compile,Quartus 15.1 standard edition不支持Rapid Recompile,Quartus 15.1 Pro edition不支持Design Partition。

3.1 Smart Compile

在任何Quartus的编译流程中,都可以使用Smart Compilation。当Smart Compilation功能打开,如果设计原文件没有任何改动,则编译过程会自动跳过Analysis and Synthesis,而如果有任何改动,则不会跳过任何步骤,相当于没有该功能。

3.2 Rapid Recompile

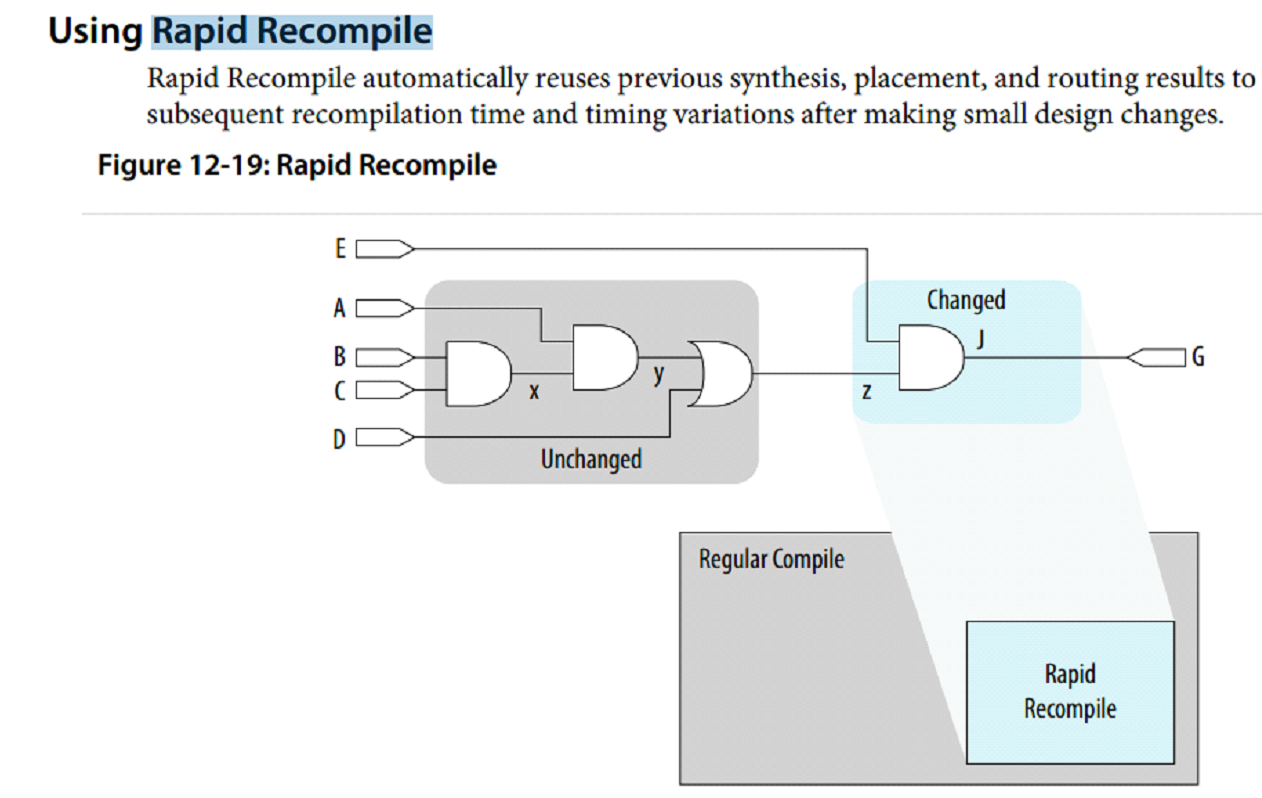

Quartus软件提供Rapid Recompile功能,让编译器可以重用上一次的编译结果,并保留性能,可以节省微小改动或隔离设计改动的编译时间,编译器会自动决定哪个部分需要重新编译,哪个部分不需要。

点击Processing > Start > Start Rapid Recompile

对于微小改动,如取反、位宽、移位、加减等小bug改动,建议使用Rapid Recompile。

3.3 Design Partition

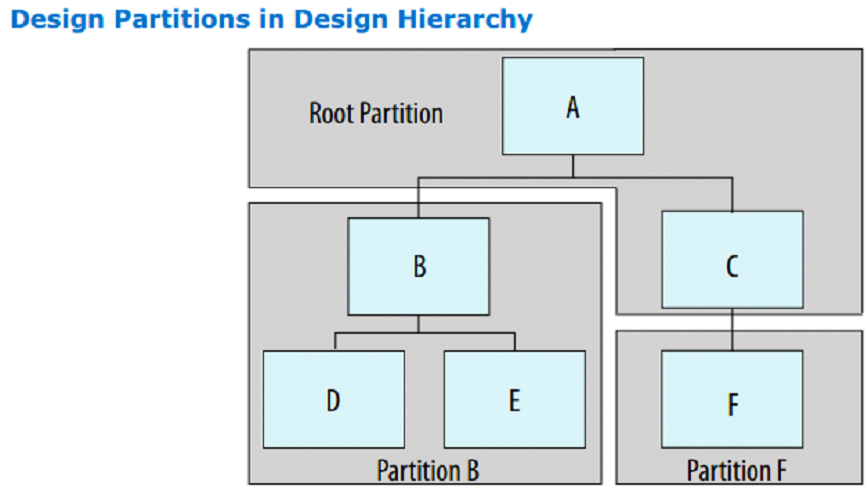

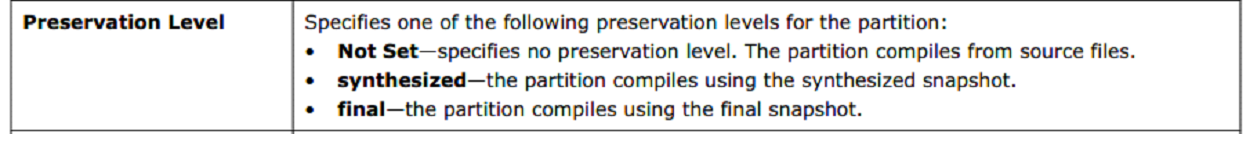

设计分区,将设计分为不同的块,可以选择保留综合(synthesized)的结果或者布局布线(final)的结果,编译时,如果只修改了其中一块的逻辑,则其他块使用之前编译的结果,以此节省编译时间。

参考文档:Intel® Quartus® Prime Pro Edition User Guide: Design Compilation

4 编译策略

如果设计已经达到了性能要求,则可以关闭某些优化选项,特别是在调试过程当中,不需要很高的Fmax,关闭优化选项可以节省不少编译时间。

与该原理类似的还可以选择更高速度等级的器件,因为综合工具需要不断的尝试不同的布局布线方式以达到时序收敛的目的,更高速度等级的器件意味着时序收敛更容易,而一旦时序收敛,综合工具就可以停止尝试,这样也就达到了减少编译时间的目的。

.

.

.

.

.

92

92

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?