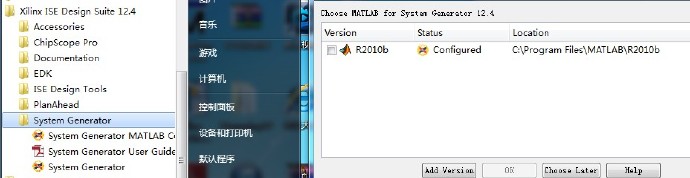

首先安装好对应版本的ISE 和matlab,然后要在simulink中使用xilinx库,要在

这里用管理员方式打开matlab configure。设置对应版本的matlab。

然后打开system generator,会自动弹出matlab和simulink。

或者打开Matlab→Simulink,可以发现左侧的Simulink Library Browser出现了Xilinx的三个工具箱菜单:Xilinx Blockset,Xilinx Reference Blockset,Xilinx XtremDSP Kit。

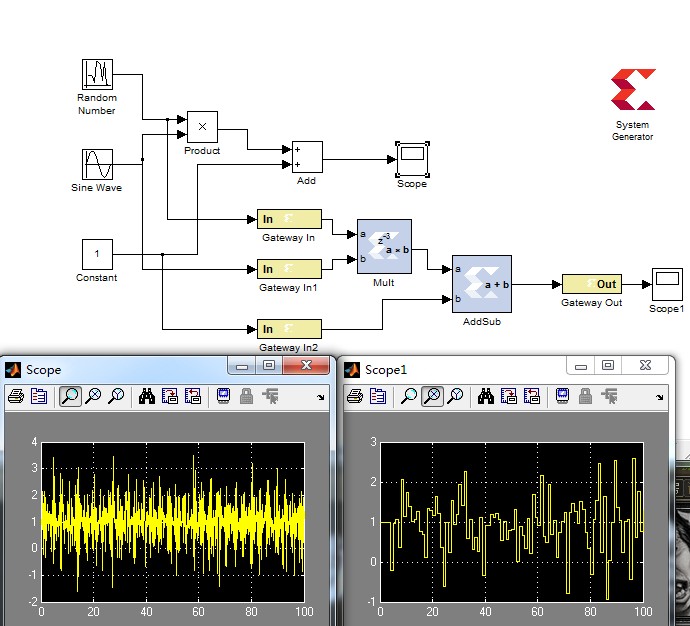

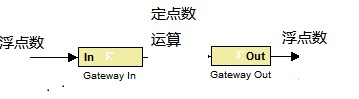

新建一个模型如下并仿真:

system generator 仿真结果。

不知道大家有没有注意到上图中gateway in

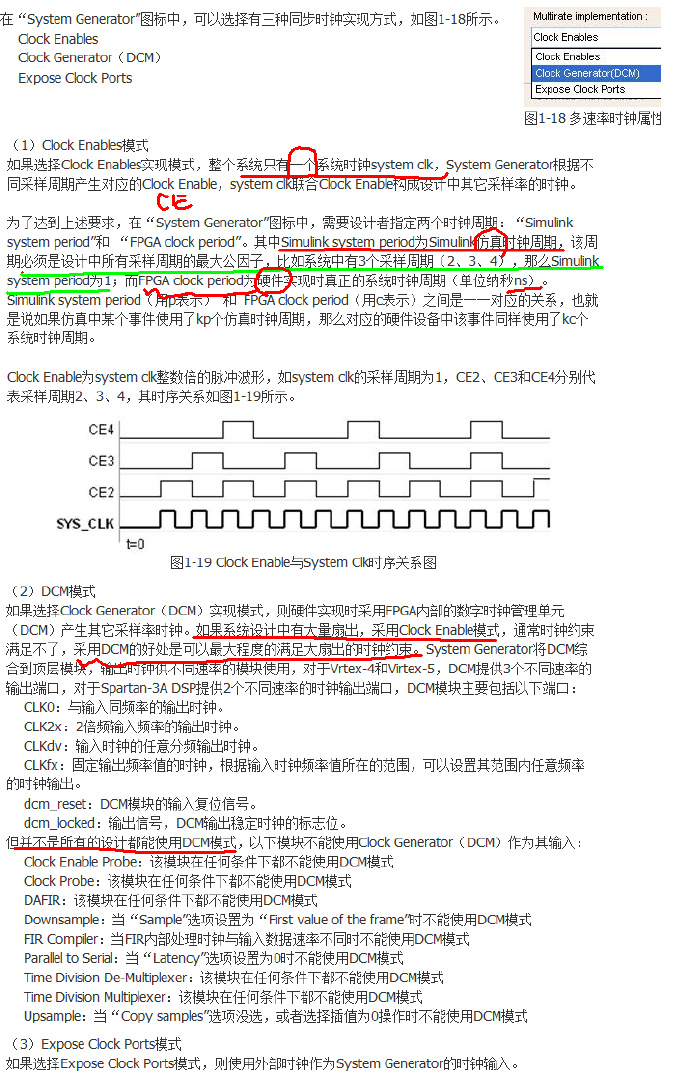

首先,每个工程里面都要有一个System Generator的工具箱(在Xilinx Blocket—tools里面),双击那个system generator的红色按钮,在这里可以配置的有

[1]. System Generator生成的工程类型,比如ISE工程、EDK工程等,甚至可以直接生产.bit配置文件;

[2]. 器件的型号,包括封装、速度等;

[3]. System Generator的输出路径(文件夹);

[4]. 综合工具(如XST、Synplify等,经常找不到Synplify,干脆就XST好了);

[5]. 编程语言选择:只有VHDL和Verilog HDL;

[6]. 可以选择是否生产测试文件;

[7]. 配置FPGA的时钟,并选择时钟管理方式,这里给出了时钟管脚的配置,不过应该先不填,不然在后面的综合中会有很多警告;其次是若选择了DCM方式,则只能支持Virtex4\5的器件(用Spartan3、3E编译时提示的;奇怪是为什么没有说支持最新的Spartan6、Virtex6器件);

[8]. 最后是选择Simulink的仿真周期,以及各个模块的显示方式(比如选择default显示各个模块的默认值,选择Sampling Frequency则在各模块的输入输出引脚上显示其时钟频率,如50MHz、10MHz等)。

点击下面的generator按钮,进行生成。生成的文件夹中是包含一个ISE的工程文件的。

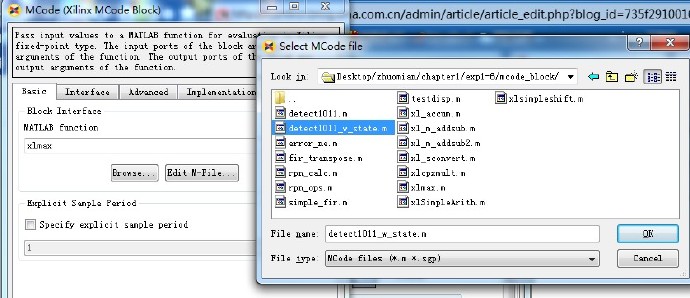

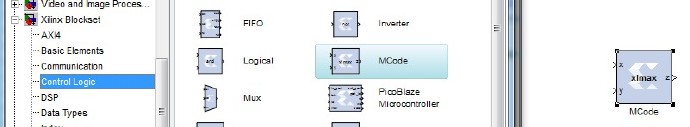

Mcode模块的使用

Xilinx Blockset中的Mcode模块,能将MATLAB的M代码文件转换成可综合的System Generator模块,模块的每一个输入端口对应M函数中的一个输入参数,每一个输出端口对应函数中的一个返回值。

当然,并不是所有的M函数都能导入MCode模块,MCode模块支持一类MATLAB语言的有限子集,一般来说使用MCode模块实现算术运算、有限状态机和逻辑控制非常有用。

使用Mcode模块,首先必须实现编写M函数,且代码文件必须和System Generator模型文件放在同一个文件夹中,或者处于MATLAB路径上的文件夹中。

首先新建一个文件,将Mcode模块拖入到文件中,

双击Mcode模块,根据下图选择实现编写好的M文件,导入并保存。

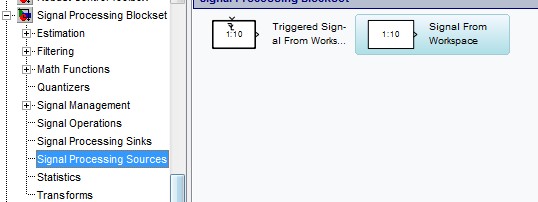

完成剩余的工程,并使用signal from workspace 模块产生测试向量

序列

最后仿真得出正确结果。

提高设计性能的方法:

(1)输入和输出加上寄存器

使用过HDL设计硬件的开发者知道,输入、输出加上寄存器对整个逻辑设计和布局布线都是非常有帮助的。所以建议在Gateway In模块后或者Gateway Out模块前加入Delay block(设为1)或者Register block。当然如果输入、输出加上两个寄存器更好,一个用于缓冲I/O端口数据,一个用于衔接到FPGA内部其它逻辑模块。

(2)尽量多使用流水线结构

在所有可能的设计中尽量使用流水线结构,可以提高FPGA内部时钟速率和FPGA设计的稳定性。

(3)多使用Timing Analysis Tool工具 <br />

多使用System Generator的Timing Analysis Tool分析当前设计的时钟约束。Timing Analysis Tool能显示出当前FPGA设计中最慢的路径和不满足时钟约束的路径,从而让设计者通过修改不满足约束的路径来优化系统设计。

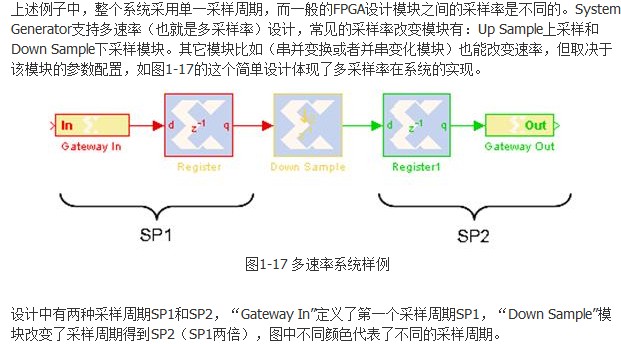

(5)设定所有Gateway的Data Rate选项

在Gateway In和Gateway Out的IOB timing constraint项中,选中Data Rate,这样IOB的时钟速率和I/O输入数据速率相同,有利于时钟同步上数据。

(6)尽量减少Clock Enable (CE)的扇出

在System Generator图标的属性选项中,如果选用Clock Enable作为时钟条件,那么要尽量减少Clock Enable(CE)的扇出。如果扇出过多,在MAP或者布局布线后可能满足不了时钟约束。如果使用ISE布局布线,那么建议将下面的选项设置为相应的值。这时采用DCM模式。

扇出(fan-out)一个逻辑门电路能驱动与之同类逻辑门的个数.

这里有个蛮好的视频

还有个比较详细的例子介绍

569

569

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?