一、集成电路的基本结构

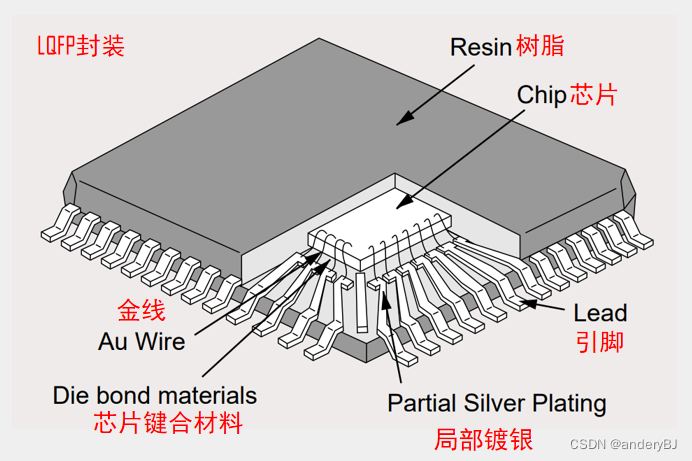

图1 集成电路的基本结构

一般地,从物理层面看,一颗完整的集成电路由晶片、金线、芯片键合材料、局部镀银引脚以及集成电路外部的封装树脂组成。

当然,对于集成电路的结构有着不同的划分方法,但是上述从物理层面对集成电路结构进行划分的方法有助于后续集成电路电磁兼容测试结果的仿真建模分析,尤其是集成电路传导发射特性模型的建立,有着举足轻重的作用,因此,对于后续理解和学习集成电路电磁兼容(IC-EMC)也就具有十分重要的意义。

二、集成电路和芯片的概念

为了弄清楚集成电路和芯片的基本概念,我查询了GB/T 9178-1988《集成电路术语》,在该标准中给出了集成电路(Integrated Circuit)、芯片(Chip)、衬底(Substrate)、晶片(Wafer)的概念。

- 集成电路(Integrated Circuit)将若干电路元件不可分割地联在一起,并且在电气上互连,以致就规范、试验、贸易和维修而言,被视为不可分割的一种电路。

- 芯片(Chip)从含有器件或电路阵列的晶片上分割的至少包含有一个电路的部分。

- 衬底(Substrate)在其表面和内部制造器件或电路元件的材料。 基片(Substrate)对膜电路元器件和(或)外贴元器件形成支撑基体的片状材料。

- 晶片(Wafer)一种半导体材料或将这种半导体材料沉积到衬底上面形成的薄片或扁平圆片,在它上面可同时制作出一个或若干个器件,然后将它分割成芯片。

由此可见,图1所示的整体为集成电路,而其最里面的核心部分为芯片,而衬底是芯片的基本材料,而晶片则是衬底的核心材料,其通过特殊加工工艺而制成芯片。

三、集成电路电磁兼容的基本概念

在说集成电路电磁兼容概念之前,先复习一下电磁兼容的概念:电磁兼容性(设备或系统级)——设备或系统在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁干扰的能力。

显然,集成电路电磁兼容性(芯片级)——集成电路在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁干扰的能力。

四、集成电路电磁兼容的意义

集成电路电磁兼容测试的必要性:

- IC作为电子系统的组成部分,其影响电子系统的EMC;

- IC可产生骚扰信号,为骚扰源,例如可将给其供电的直流电源转换为高频电流或电压,从而产生无用发射;

- IC也易受过电压或过电流而损坏,例如耦合到IC引脚的噪声也会使其发生故障。

集成电路电磁兼容测试的意义:

- 基于此,要对IC的测试进行标准化;

- 通过测试,设计人员能够选择发射低、抗扰度高的IC;

- 评估IC的设计;

- 优化IC的设计等。

作者信息:朱赛,18210821611,zhusai@cesi.cn

1878

1878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?