一.基本单元

CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT(内部封装了2个5输入LUT)和8个寄存器,2个F7选择器,1个F8选择器,一个由多个与非门所组成的进位链.slice也分为SliceM和SliceL,其中M是Memory的首字母,L是Logic的首字母,比较SliceM和SliceL,他们的区别就是SliceM的查找表具有RAM和ROM的功能,而SliceL的则不具备。所以SliceM比SliceL多的功能就是做存储器和移位。。

二.LUT

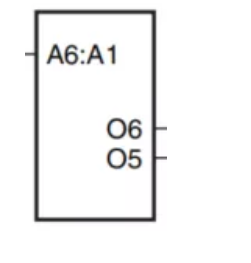

7系列的FPGA的LUT有6个输入端口(A1-6),然后有两个输出端口(O5,O6)。下图是SLICEL里面的LUT。

其可以实现6输入的布尔组合逻辑函数,输入信号为A1,A2,A3,A4,A5,A6,输出端口为O6。如下

O6=f(A1,A2,A3,A4,A5,A6)

其实现方式就是将输入(A1,A2...A6)对应的输出在LUT里面预存好(这一步在我们用bit文件配置FPGA时实现),然后把输入信号当作地址信号去把对应的输出信号调出来。

同样其还可以构成两个5输入的布尔组合逻辑函数,其中这两个函数共用5个输入信号(A1,A2,A3,A4,A5),A6被拉高,O5,O6分别是两个布尔逻辑的输出。

O5=f(A1,A2,A3,A4,A5)

O6=f(A1,A2,A3,A4,A5)

故这也相当于实现的是一个5输入2输出的逻辑函数。

[O5,O6]=f(A1,A2,A3,A4,A5)

总结一下,就好比单个LUT里面可以预存 2^6=64个结果。那么单个LUT可以实现

(1)输入信号最多为6bit,输出信号为1bit的的布尔逻辑函数;

(2)输入信号最多为5bit,输出信号为2bit的逻辑。

一个SLICE里面有四个LUT故最多可以预存的输出信号个数为 2^6*4=2^8。

因此在一个SLICE里面,借助选择器将多个LUT进行互连,可以实现输入数,输出数最多为如下所示的逻辑。

(1)2个LUT通过互连可以构成7bit输入,单bit输出的逻辑。实现方式为两个LUT的输入信号A1,A2,A3,A4,A5,A6接到一起,输出信号经过选择器选择输出,选择器的选择信号也是逻辑函数的一个输入信号。

将逻辑函数的输出送到Storage Element便可以形成同步时序逻辑。

三.MUX

mux将多个LUT组合到一起,构成7,8,9输入的任意函数,F7链接两个LUT组成8:1多路器,F8链接两个F7组成16:1多路器

四 .bram

单片块RAM的容量为18k比特,即位宽为18比特、深度为1024,可以根据需要改变其位宽和深度,但要满足两个原则:首先,修改后的容量(位宽 深度)不能大于18k比特;其次,位宽最大不能超过36比特。当然,可以将多片块RAM级联起来形成更大的RAM,此时只受限于芯片内块RAM的数量,而 不再受上面两条原则约束。

五.bufg

全局时钟缓冲器,综合器自动推断,用于链接全局时钟或者复位信号等高扇出网络

2113

2113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?