XILINX FPGA DDR3 verilog代码,将DDR3配置成一个大型FIFO,使用简单方便,可用于大数据量的

缓存,直接联系默认为DDR3。

同时也有8通道的DDR4驱动(需单沟通):Xilinx DDR4多通道读写防冲突设计,可实现8个通道同时读写DDR且不冲突问题,每个通道读写接口简单,操作独立,可同时实现最高8个通道的读写请求,有设计说明文档

ID:52100673834971358

FPGA_2049

XILINX FPGA DDR3 verilog代码:实现大型FIFO的配置方案

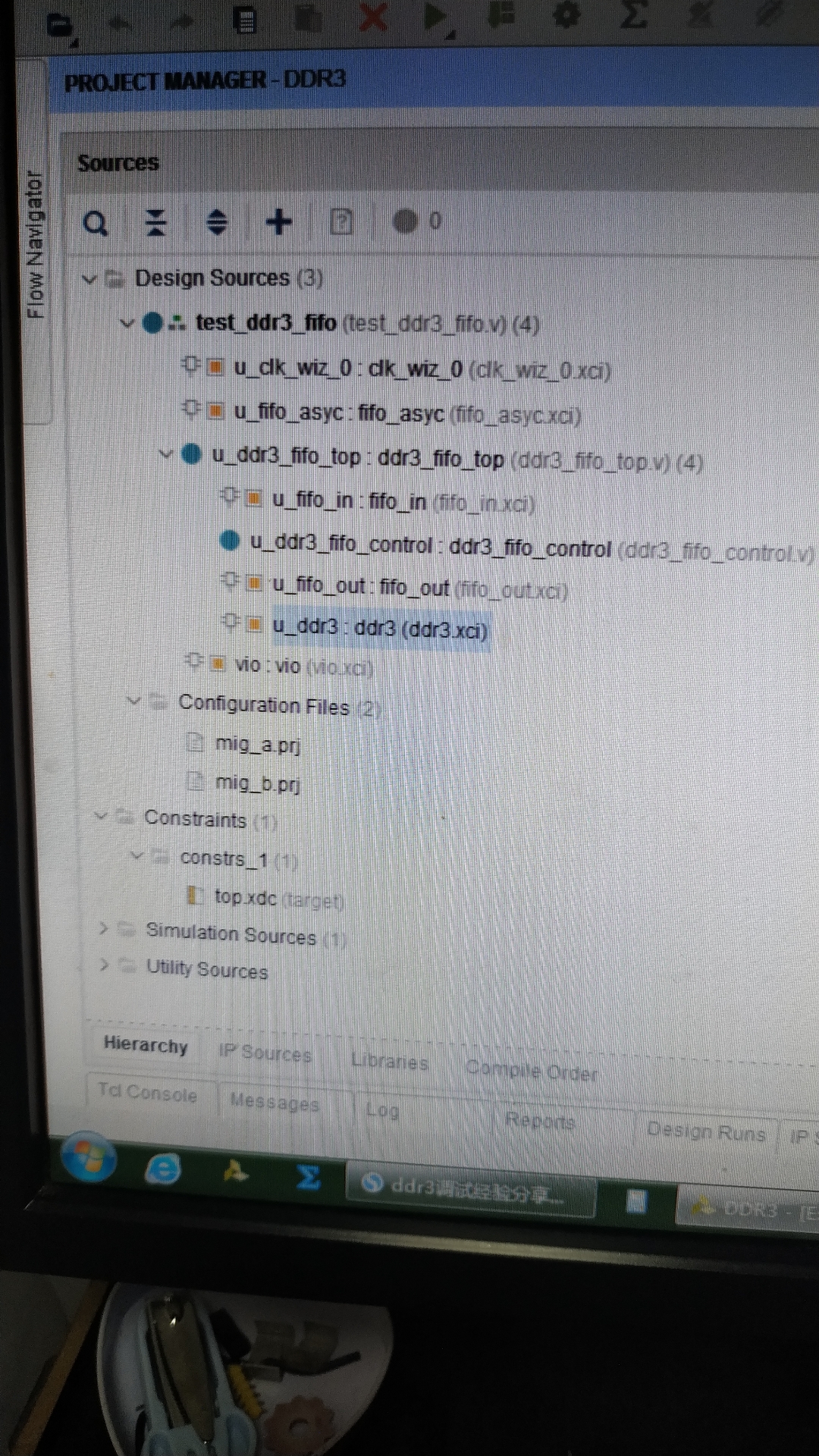

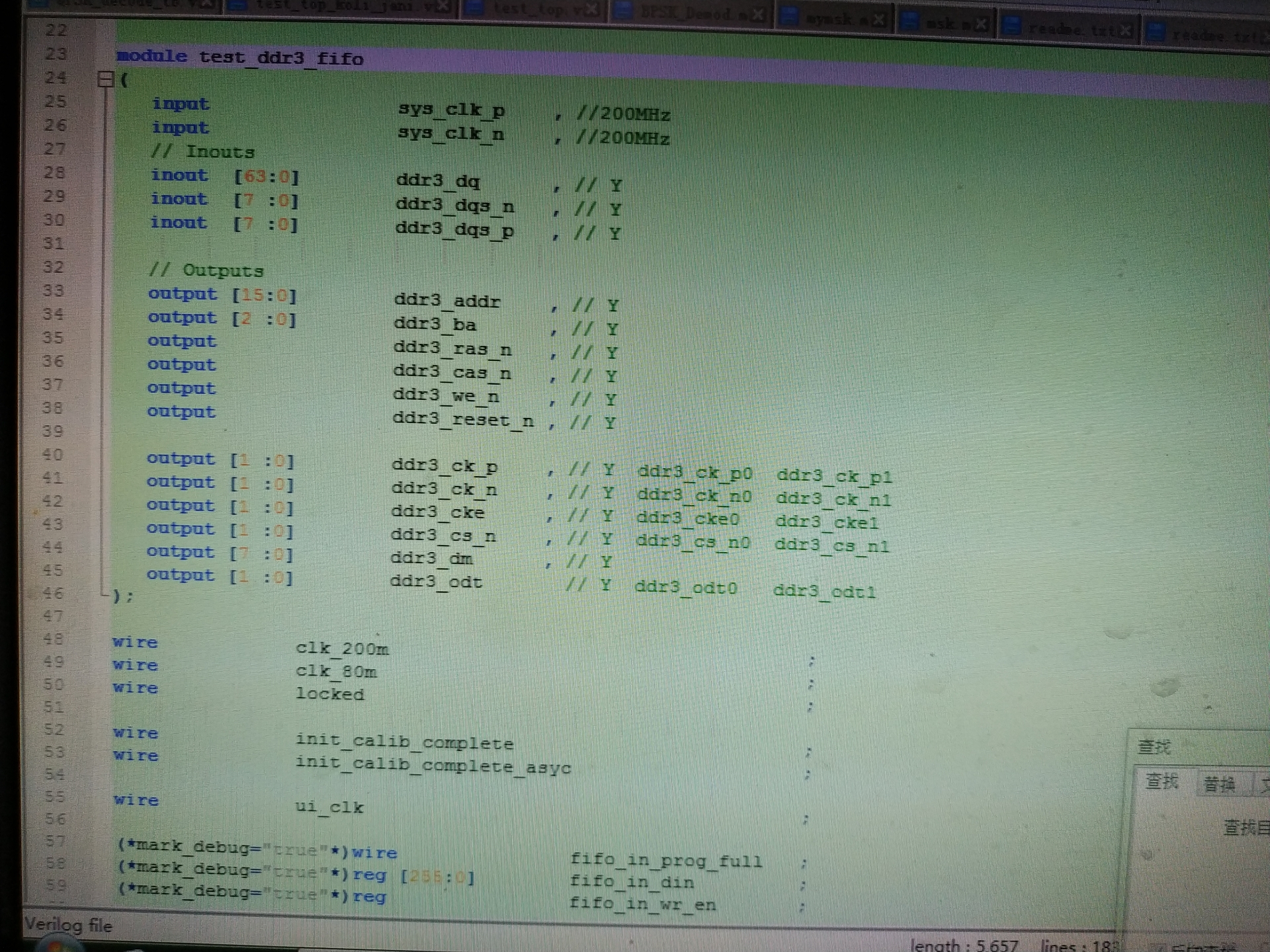

在现代计算机系统中,大数据量的处理和传输已成为一项重要任务。为了有效地处理这些数据,我们需要高效的缓存机制。DDR3(Double Data Rate 3)作为一种高速动态随机存储器,具有高带宽和低延迟的特点,成为了一种理想的选择。在本文中,我们将介绍如何使用Xilinx FPGA(Field-Programmable Gate Array)的DDR3 verilog代码将DDR3配置成一个可以满足大数据量缓存需求的大型FIFO。

首先,我们需要了解DDR3的基本结构和工作原理。DDR3采用了具有高速时钟信号的双数据传输技术,通过在上升和下降沿传输数据,以达到提高带宽的目的。在配置DDR3时,我们需要确保时序和控制信号的准确性,以确保数据的稳定传输和正确读写。

在Xilinx FPGA的设计中,我们可以使用verilog代码来实现DDR3的配置。通过编写适当的代码,我们可以设置DDR3的参数和寄存器,以满足我们的需求。例如,我们可以设置读写时钟的频率和时序,设置读写通道的数量和宽度,以及配置FIFO的深度等。在配置过程中,我们需要根据DDR3的规格手册和FPGA的技术文档来确定正确的参数和设置。

一旦DDR3被正确配置成一个大型FIFO,我们就可以使用它来处理大数据量的缓存任务。通过将数据写入FIFO,我们可以暂存需要处理的数据,并在需要时读取出来。DDR3的高带宽和低延迟特性可以保证数据的高效传输和处理,从而提高系统性能。

除了DDR3的配置,Xilinx FPGA还提供了8通道的DDR4驱动设计。DDR4作为DDR3的升级版本,具有更高的带宽和更低的功耗。通过使用Xilinx FPGA的DDR4驱动设计,我们可以实现八个通道同时读写DDR,并解决读写冲突的问题。每个通道的读写接口都是独立的,操作简单,可以同时满足八个通道的高速读写请求。此外,还提供了设计说明文档,方便用户了解和使用。

总结起来,通过Xilinx FPGA的DDR3和DDR4驱动设计,我们可以实现高性能的大型FIFO缓存系统。通过合理配置DDR3的参数和设置,我们可以满足大数据量的缓存需求,并通过DDR4的多通道读写设计实现高效的数据处理。这些技术的应用可以帮助程序员在处理大数据量时提高系统的性能和效率,为计算机系统的发展做出贡献。

(文章字数:484)

相关的代码,程序地址如下:http://wekup.cn/673834971358.html

369

369

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?