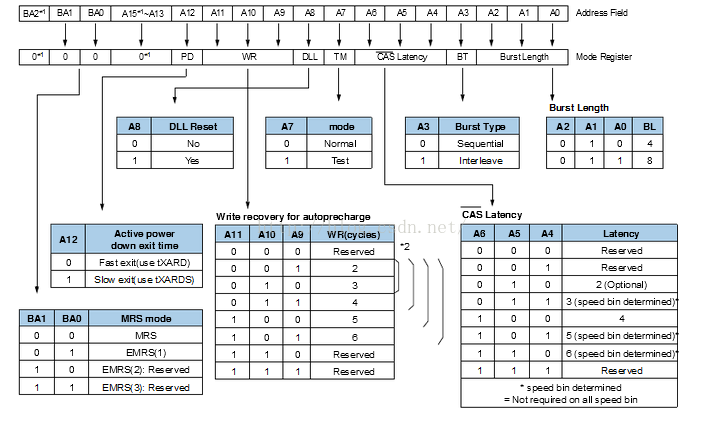

DDR Mode Register Set(MRS)

burst Length:连续读出字节数

burst Type: Sequential (memory device 中bank1 中的地址为0x00,0x01,依次排列);InterLeave(交错模式,bank1的地址为0x00,bank2的地址为0x01)。

CAS Latency:

WR:

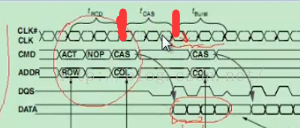

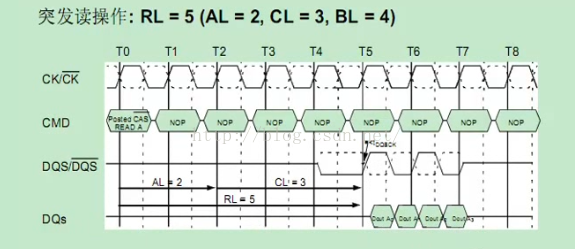

读时序:

RL = AL+CL

寄存器延时配置(BANKCON2)

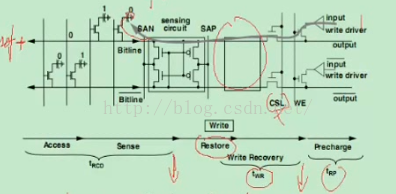

RAS:Active命令到Precharge命令的最小时间。

ARFC:指令刷新时间。

CAS:CAS Latency Control。read/write经过CAS之后有效。

RCD:active命令经过RCD延时之后才能发送read/write命令。

RP:Precharge命令到发送Active命令时间间隔。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?