目录

猝发长度(Burst Length, BL)是指某行打开期间,能够连续读取的列数;而预取(Prefetch)则是指在指定BANK和行列地址之后,可以往该地址内写入(或读取)的数据量(DDR3是8 Bytes)。

学习DDR有一段时间了,对DDR的内部结构、存取原理、工作特性等有了一定的了解,但是对它的Burst和Prefetch概念始终不太理解,总觉得它们是相同的东西不同的叫法而已。

经过多方查阅资料和自己的思考,我对这两个概念逐渐地清晰了,特此总结一下。

为简化描述和理解,以常见的DDR3 x8 为例进行说明。

1.DDR内部组织架构

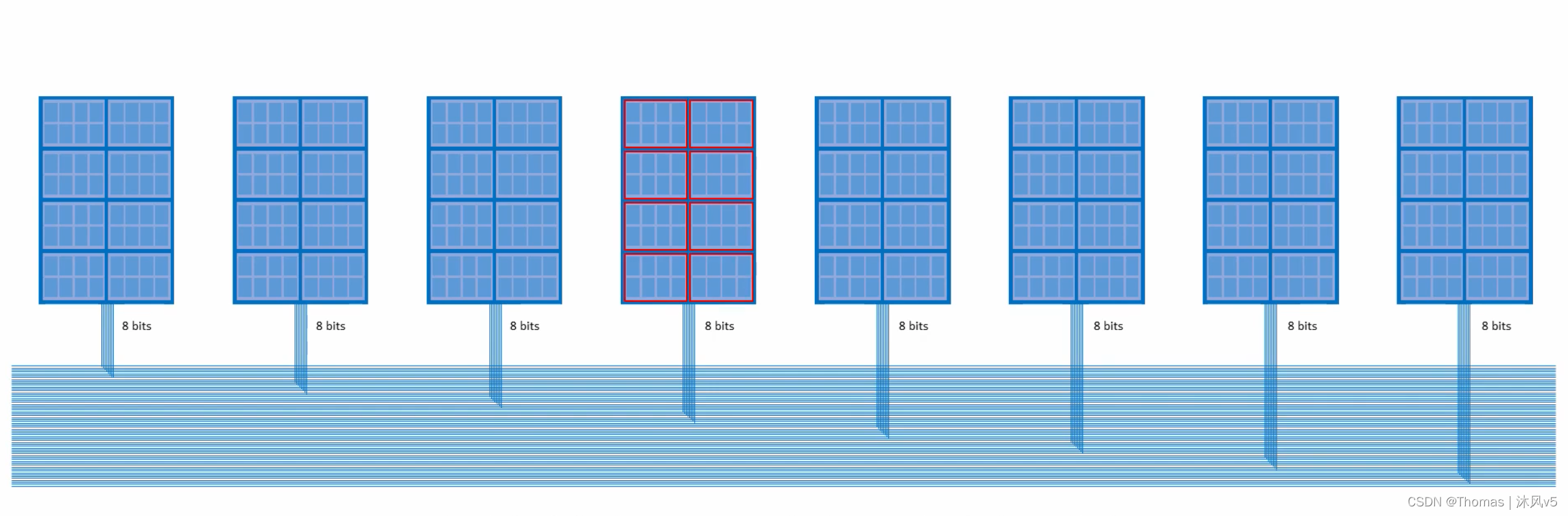

如下图所示,常见的内存通道总线位宽是64 bits,假设使用x8内存颗粒,则需要8颗IC才能组成64 bits。这64 bits是同时存取的,称为一个RANK,即CPU一次访问的位宽。

每颗IC内部一般分为8个BANK(如上图红色框),CPU访问时是以BANK为基本单位的。每个芯片相同位置的BANK,它们的地址线和控制信号是一摸一样的,因此当CPU同时向各芯片写入8 bits数据时,它们写入的是相同位置的BANK。

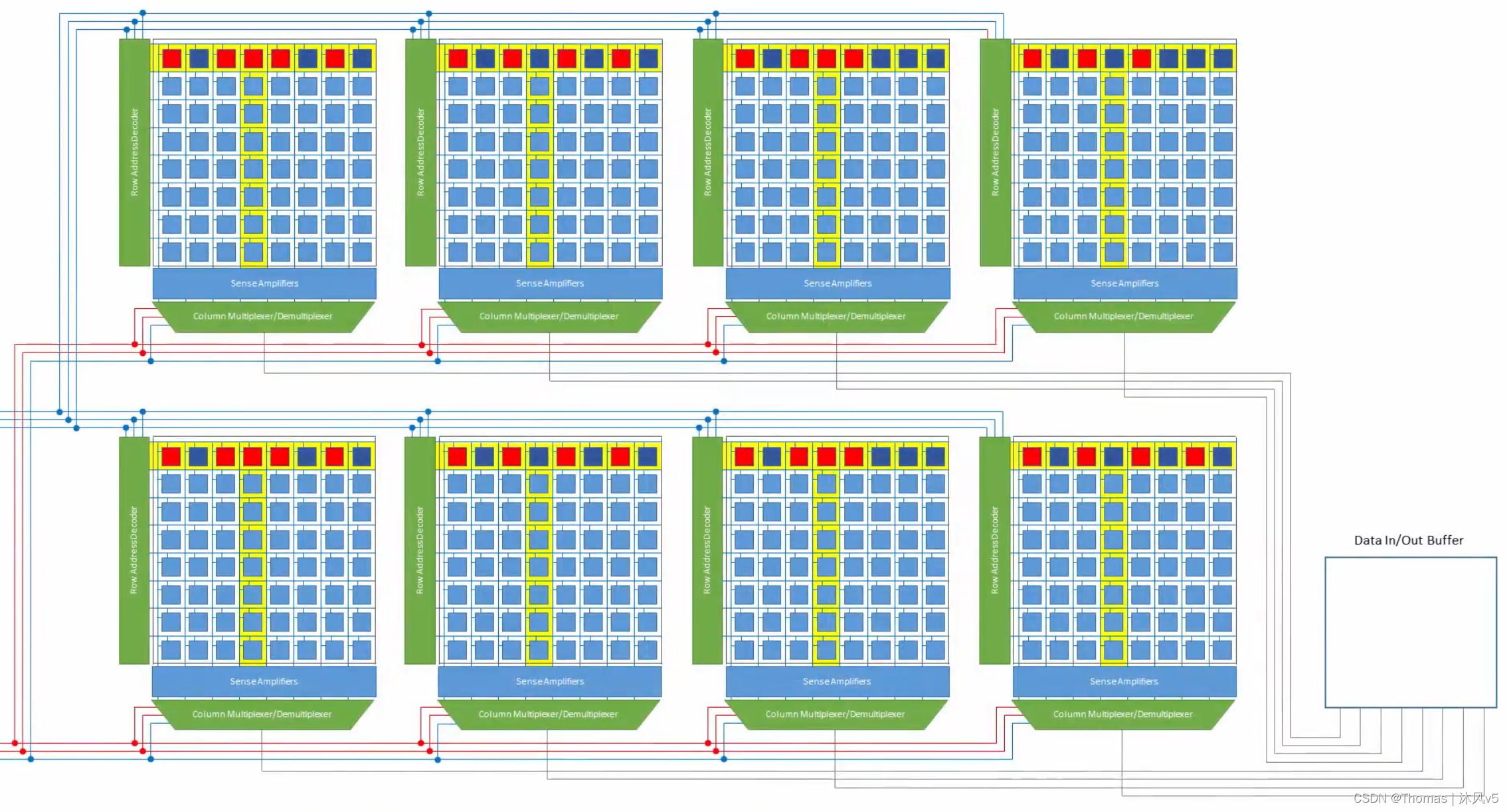

每个BANK内部包含8个存储阵列,每个阵列每次可存取1 bit数据。一个BANK的组成结构如下:

进一步细化如下:

每个存储阵列包含8行8列,共64个存储单元(此处为简化模型,一个实际阵列为长方形,可能包含1024列16384行),每个存储单元可存储1 bit数据。

读取流程:激活行地址,锁存行数据到感测放大器-->激活列地址,数据送到输出缓存-->利用感测放大器值刷新行数据-->关闭位线,关闭行线,位线预充电。

由于8个阵列的行列地址线是共用的,指定行列地址也就指定了8个阵列中相同位置的存储单元,每个阵列可读取1 bit,共8 bits数据。如下图所示:

举例:激活第0行时,8个存储阵列的第0行都被打开,数据被同时锁存到感测放大器中(如上图中红色箭头,此过程非常耗时);当激活列地址时,8个阵列中相同位置的1bit数据被指定,并被同时送往输入/输出缓存中,这就完成了一次8 bits数据的读取(如上图中黄色箭头)。

注意,这里只是单颗IC中1个BANK的操作过程。实际工作时,CPU每次访问一个RANK,包含8颗IC,每颗IC中相同位置的BANK都同时输出8 bits(1 Byte),共64 bits数据。

2.Burst的概念

仔细观察上述读取过程会发现,为了获取1 bit的数据,需要打开BANK中的一整行(包含8个存储单元,甚至1024个或更多)。读取完毕后需要关闭整行,然后给bit线预充电,再去打开另外一行,再去读取1 bit,这个过程实在是浪费,效率非常低。

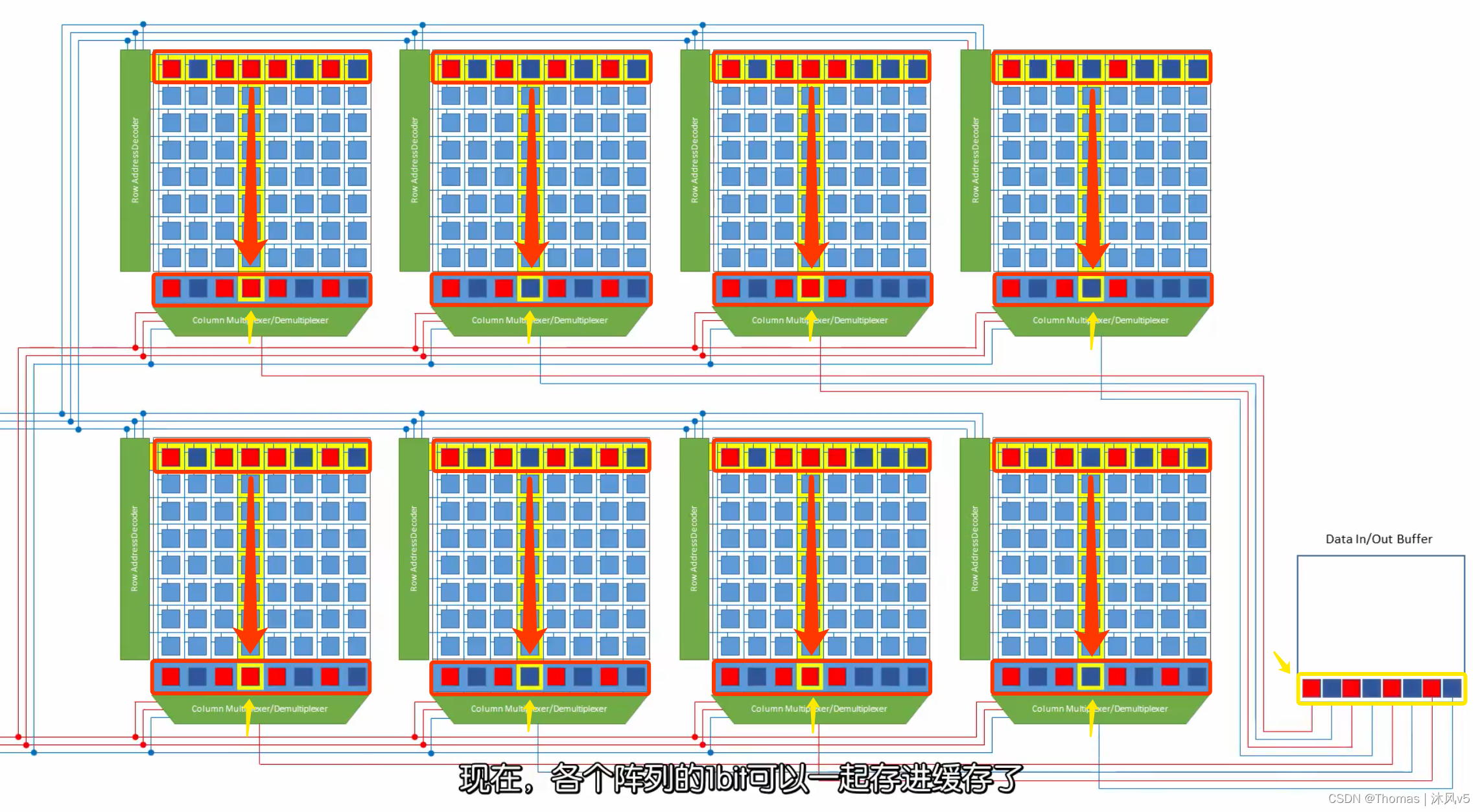

早期的DRAM由于上述原因,存取速率较低。实际上,当打开一行时,相邻位置的另一个Byte数据也可以送入输入输出缓存(如下图中黄色箭头)。

也就是说,仅提供一个行地址和一个列地址,就可以非常快速的完成一次猝发(Burst)。某行打开期间,能够连续读取的列数,称为“猝发长度(BL)”。

不同代DDR的猝发长度不同,通常DDR的BL是2,DDR2的BL是4,DDR3的BL是8,DDR4的BL也是8。

以上例子中,一个BANK每次可以提供连续位置的8 Bytes(64 bits)数据。

3.Prefetch的概念

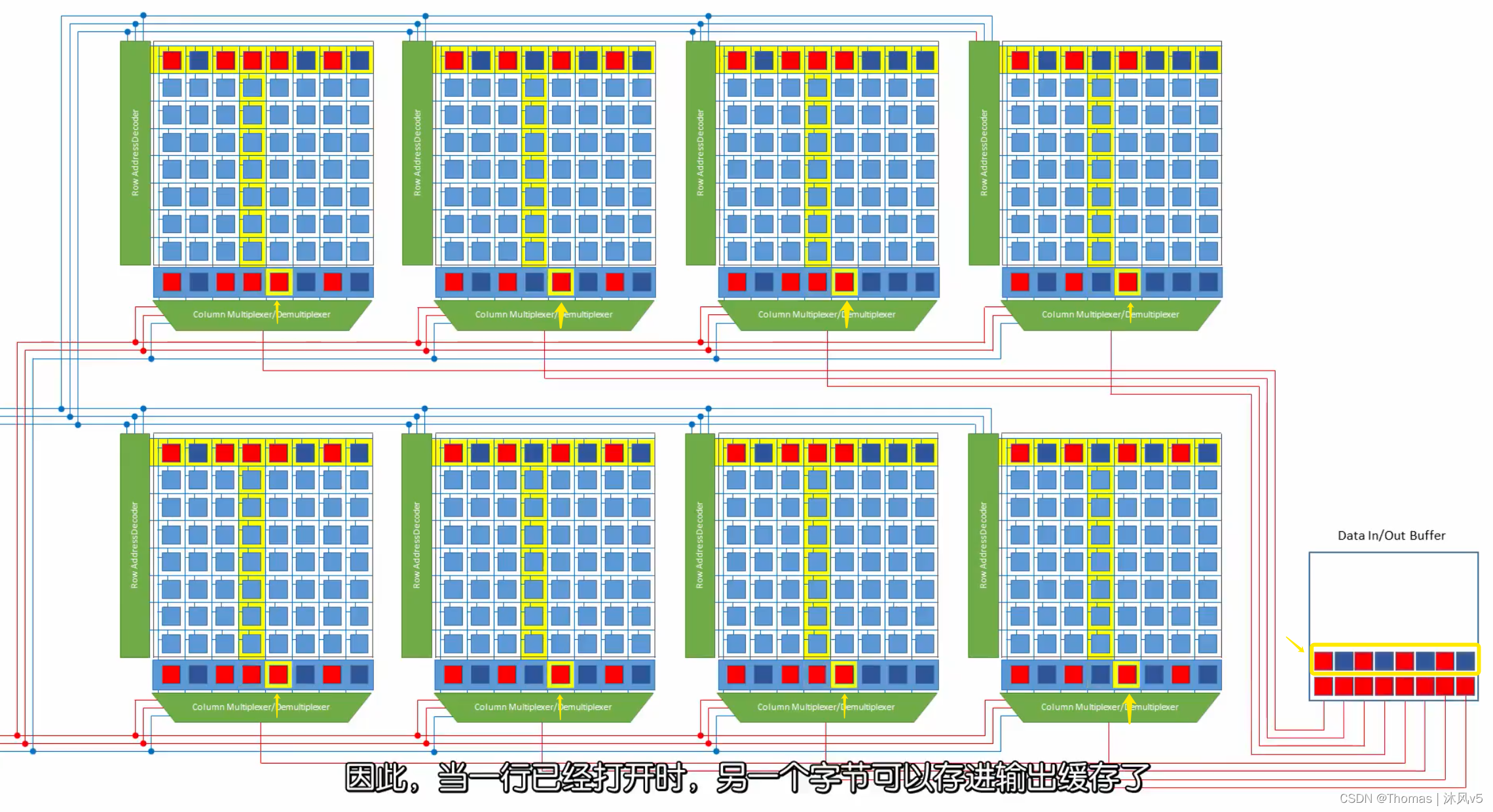

别忘了,以上看到的仅是一个BANK的情况,实际上DDR3的一次RANK访问中,8颗IC各有一个BANK同时在工作,以在一个RANK访问的短时间内处理8个8 Bytes(64 Bytes)数据,这个技术称为“预提取(Prefetch)”。通常DDR的预取是2n,DDR2的预取是4n,DDR3的预取是8n,DDR4的预取也是8n(n为DDR的位宽)。

这里还有一个问题,一个BANK在某个时刻只能打开一行,一次猝发结束后,这一行就得先关闭才能开启别的行。这个过程涉及到刷新该行的所有单元,并且再次给位线预充电,整个过程可能需要18个CPU时钟周期!

进一步,数据在DRAM和CPU之间是一块一块交互的,交互的对象称为“高速缓存行(Cash Line)”,一条高速缓存行一般是64 Bytes,即8个64 bits。现代DIMM的一次猝发就能塞满一条高速缓存行,因此DRAM和CPU的交互速率就是数据的传输速度。

但如果多条高速缓存行想连续获取数据该怎么办?这将涉及到内存交错(BANK Interleaving)操作,我将在另一篇博文中详细阐述(详见:DDR知识二:内存交错技术(BANK interleaving)原理)

4.总结

猝发长度(Burst Length, BL)是指某行打开期间,能够连续读取的列数;而预取(Prefetch)则是指在指定BANK和行列地址之后,可以往该地址内写入(或读取)的数据量(DDR3是8 Bytes)。

===========================全文完毕=====================================

欢迎留言讨论,批评指正。码字不易,求关注点赞收藏,一键三连,给予我继续创作的动力,感谢!

1655

1655

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?