前言

作为一名硬件设计工程师,MOSFET想必经常出现在大家的硬件设计中,今天我们聊一下与MOSFET栅极那点事。

一、MOSFET管GS波形

我们测试MOSFET的GS波形时,总是会看到Fig.1 (2)所示的波形。这种波形现象称之振铃。振铃的大小直接影响着设计的可靠性,当振铃的赋值较小时,还能勉强过关,但是当振铃的赋值较大时,轻则会增加MOSFET的开关损耗,重则使得系统不断重启。

二、振铃产生的根本原因?

1.引入寄生参数的概念

I. 无论是芯片内部的bonding line,还是PCB的走线,都不是理想的导线,多多少少都会存在寄生电感和寄生电阻

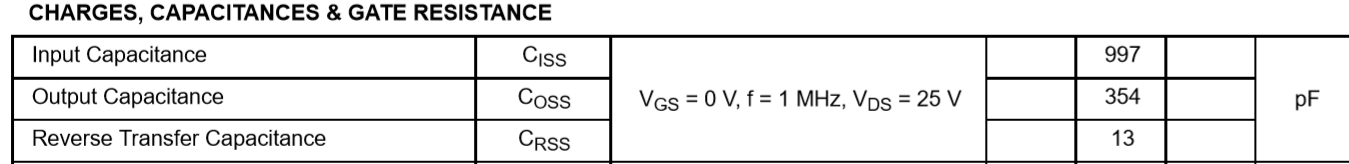

II. 由于制造工艺的原因,MOSFET的GS,GD,DS端都会存在寄生电容,这三个参数一般会在datasheet中表明

2.引入串联谐振的概念

对于一个RLC组成的串联谐振电路,其中L,C为储能器件,不消耗能量,R起到阻止振荡的阻尼作用。R阻值的大小决定C两端是否发生阻尼。

I. R>2(L/C)^0.5时,处于过阻尼情况

II. R=2(L/C)^0.5时,处于临界阻尼情况,此情况下的波形与过阻尼相似

III. R<2(L/C)^0.5时,处于欠阻尼情况 ,在这种情况下,电路肯定会发生振荡

3. 栅极回路分析

将上面的寄生和串联谐振的概念结合起来,分析一下MOSFET的驱动电路。

走线的寄生电感包含芯片内部的bonding line和PCB layout走线两部分;

驱动电阻+走线寄生电感+GS端电容共同组成了RLC串联谐振电阻。

当MOS打开时,IC内部推挽结构的上管打开,下管关闭,IC经过驱动电阻R,走线寄生电感L,给GS电容充电;

当MOS关闭时,IC内部推挽结构的上管关闭,下管打开,C经过走线寄生电感L,驱动电阻R,放电到GND。

4. 消除振铃的几种方法

I. 增大驱动电阻R,使其工作在临界阻尼,或者过阻尼的工作状态

II. 减小PCB走线寄生电感,即MOS栅极的驱动线尽可能的短

III.在GS端增加瓷片电容

说明:方法I,III都需要根据实际情况去做调节,因为增大电阻和电容都是增加MOSFET的开通损耗,导致MOSFET发热严重,到底如何选择R的值,请关注下一篇文章。

总结

提示:这里对文章进行总结:

例如:以上就是今天要讲的内容,本文仅仅简单介绍了MOSFET栅极RLC串联谐振的由来和影响。

1012

1012

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?