DDR4: 2G、32bit数据位、2400M

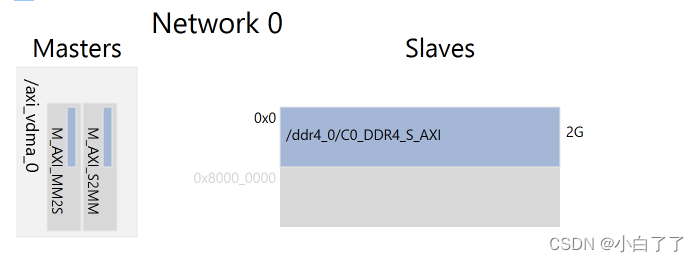

一、由于使用的是PL端ddr,vdma和ddr的通信是一个单独的AXI总线,所以在PL端vivado的DDR总线地址分配时,要注意分配的地址是多少,这个要和VDMA中的帧存储地址要保持一致。

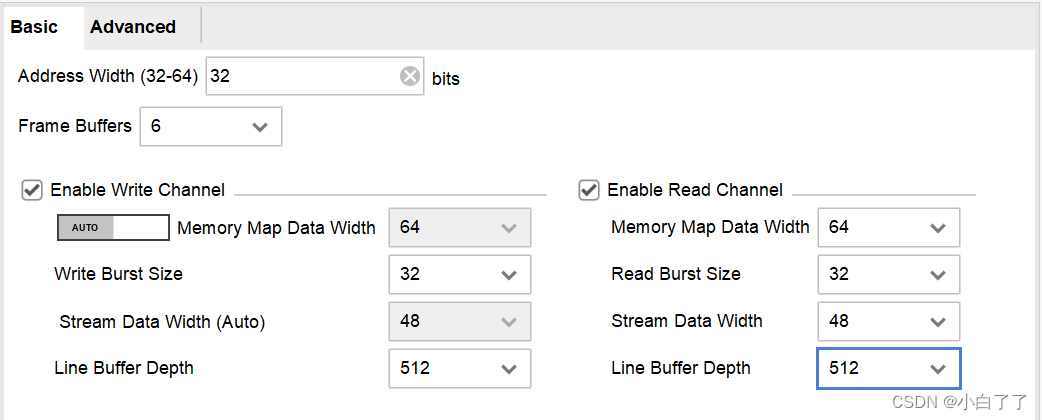

二、VDMA IP核配置

本次使用的DDR4的带宽是够3840*2160@60hz的视频实现同时读写数据的,但VDMA处AXI的通信带宽需要调整,增加突发长度可以增加吞吐量。所以如果发现视频传输吞吐量不够的话,可以适当调整下这个参数。

Specify the maximum number of data beats allowed for WriteChannel(S2MM)AXl Memory Map per burst transfers.

Setting a smaller value reduces throughput but allows morebandwidth allocation to other AXl Memory Map Masters.

Higher values increases throughput, butallows less bandwidth allocation to other AXl Memory MapMasters.

三、VDMA配置过程中,我没有使用到中断,但是读写status的寄存器中读到了中断,展示不影响,只要没有error中断就证明传输没问题,这个问题我在xilinx论坛中也有发现,链接:https://support.xilinx.com/s/question/0D52E00006hpRJCSA2/vdma-frmcntirq-usage?language=zh_CN

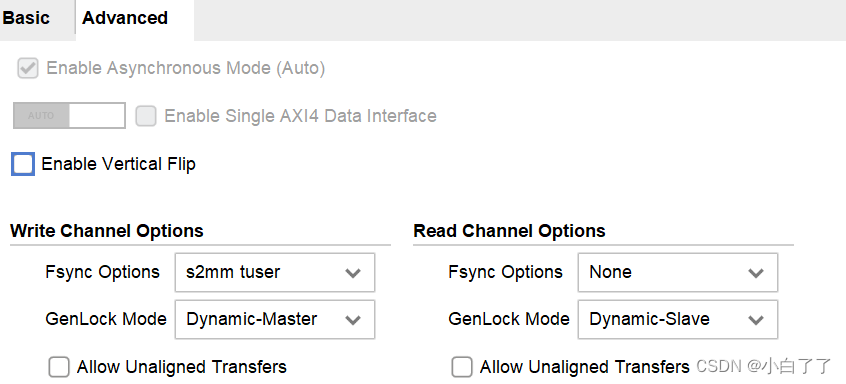

四、VDMA的配置:

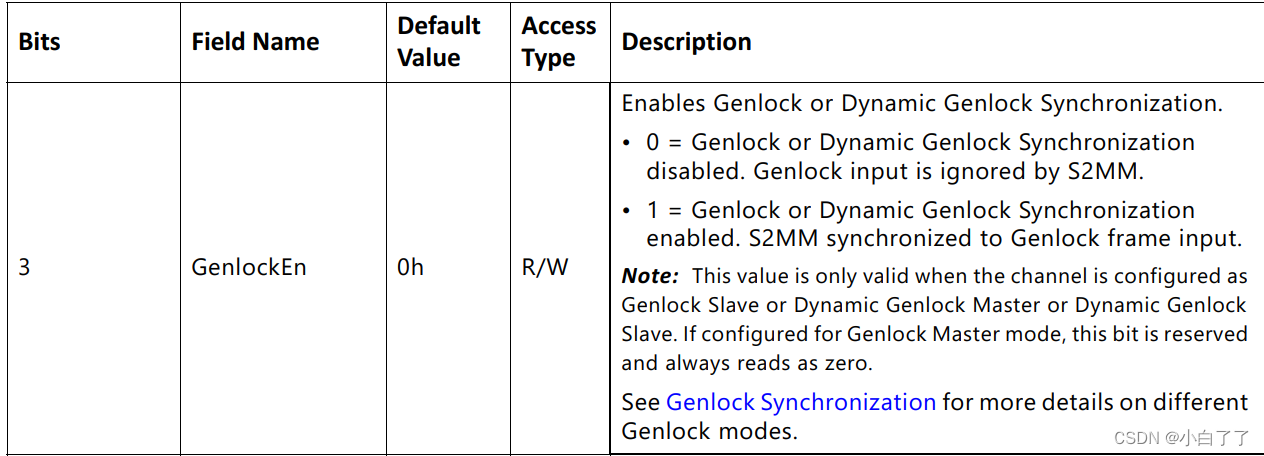

这里只有不选择Genlock Master的情况下,这个GenlockEn才能被使能,这里千万需要注意。这个寄存器是偏移是 读:0x00和 写:0x30。

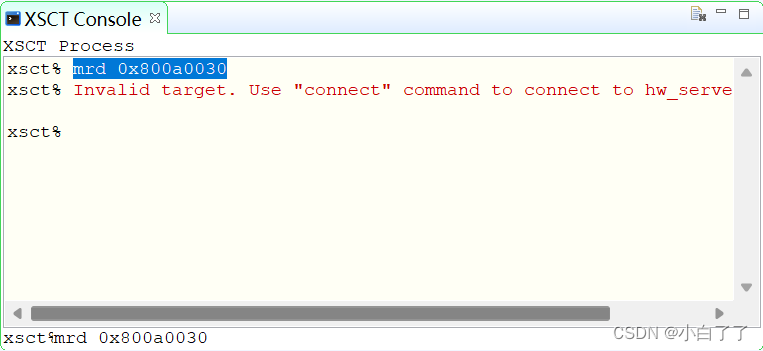

五、PS端Vitis软件中提供的XSCT 窗口很适合寄存器调试过程中的查询和更改。

六、贴出一个比较好的一个配置流程,供大家参考,这个来自于网上搜寻,不是我写的实际代码。

https://github.com/txzing/Lattice_A7/tree/132d45249c9c088d286d366f2e9f068aa9fb52c7/A7/vitis/src/vitis_proj/src/vdma

339

339

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?