参考资料:pg020_axi_vdma.pdf

VDMA可以在内存和数据流之间做切换,从而实现一些类似于帧率切换,数据加载等功能,下面简单描述一下vdma的使用,方便后续调试。

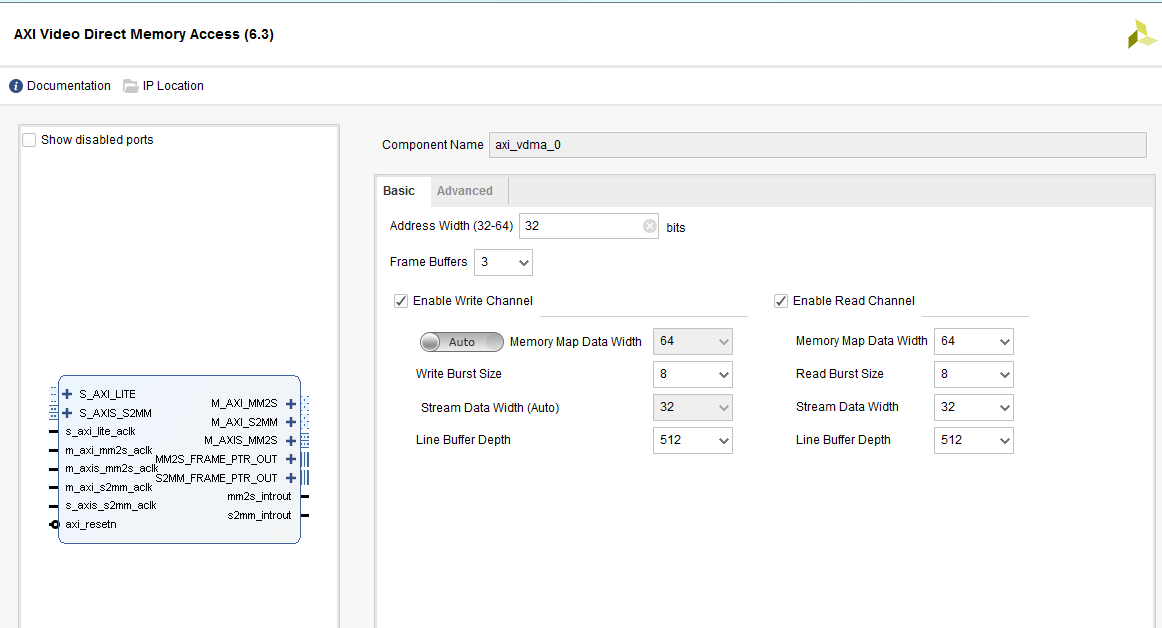

vdma的配置界面1:

其中可以配置地址总线宽度,AXI总线数据总线宽度,读写burst size,Stream数据总线宽度,以及linebuffer深度(手册描述的是AXI从ddr读数据会先放到line buffer,然后再发送;stream会先写到linebuffer,然后再写内存)

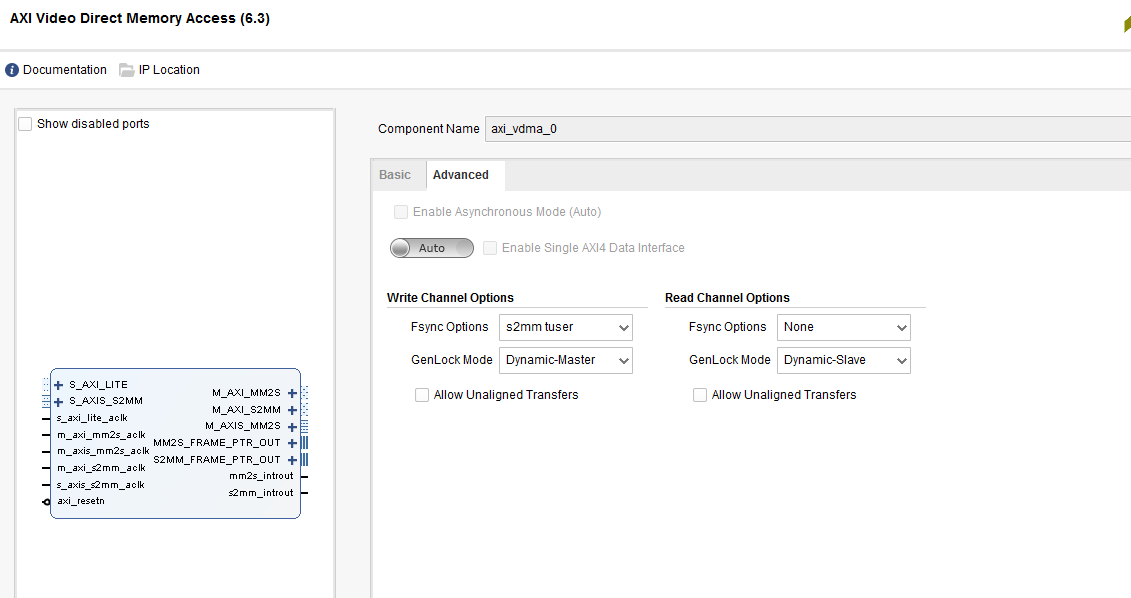

vdma的配置界面2:

这里可以配置产生fsync选项,genlock选项,以及是否允许非对齐传输,fsync相当于一个同步信号,有效后才会触发vdma工作;genlock是一个读写通道之间同步的机制;

下面以一个持续发起MM2S读内存,然后通过AXIS_MM2S stream接口将数据发送出去,

1.版本寄存器0x2c

2.配置MM2S控制寄存器0x00为0x8b

3.配置hsize 寄存器0x54为0x100,代表只要vdma从内存取够256byte,就会开始stream传输;

4.配置mm2s stride寄存器0x58为0x200,代表stream每发送512byte数据后,就产生一个tlast;

5.配置ddr起始地址,因为我们配置时选择3个frame buffer,故这里配置0x5c,0x60,0x64都为0x10000000,代表都从内存0x10000000取数据;

6.配置vsize寄存器0x50为0x5,代表发起5次stream传输后(每次以tlast为标志),下次再从内存取数据的话,从首地址取;

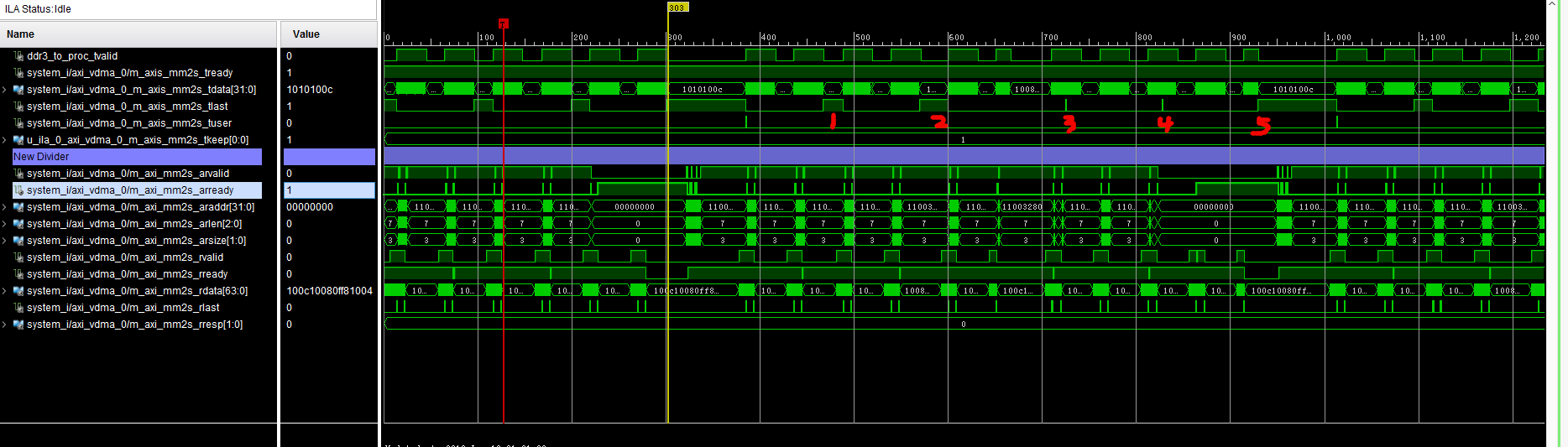

在线调试结果:

缺点:目前发现缺省配置下vdma占用LUT资源都有2k,资源不小。

1599

1599

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?