参考文档:《UG871》

目录

Lab1 创建高层次综合工程

基于HLS的FIR滤波器实现流程

Step1 创建工程

(1)打开Vivado HLS 2015.4,单击Create New Project

(2)输入工程名和工程路径后,单击Next

(3)指定顶层函数名,以及添加所需要的源文件。如果有准备好的文件,可在此步骤进行添加,这一步也可以在工程建立好后再进行。

【注意】在这个实验中,只有一个C设计文件,如果有多个C设计文件需要被综合时,需要在此步骤下全部添加进来。而此路径下的所有头文件会自动添加到工程中。如果头文件分撒在不同的位置,则使用Edit CFLAGS按键添加标准gcc/g++搜索路径信息,例如 -I<path_to_header_file_dir>。

(4)指定测试文件,除了头文件,这里要求测试平台以及其用到的所有文件都要被添加到工程中。如果需要自己后面新建测试文件,这里可以跳过(点击Next)

C仿真和RTL协同仿真都是在solution的子目录下执行。如果没有把测试平台使用的所有文件(例如这里的测试平台读取文件out.gold.dat)包括进来,则会由于无法找到数据文件导致C和RTL仿真失败。

(5) 在下面的Solution Configuration界面中,指定了第一个解决方案(solution1)。工程中可以有多个方案,每个解决方案使用不同的目标技术,包括约束或综合指令。

设置时钟周期为默认的10位(单位ns),Uncertainty若不填,则默认为12.5%。

(6)点击Part Selection右侧按钮进行芯片选择。

这里我们选用xc7a35tcpg236-1,则在search栏输入xc7a35tcpg236-1,然后在Device中选择xc7a35tcpg236-1器件,单击OK。

7)选中后,回到上一个界面,点击Finish

(8)如果之前已经全部添加源文件和测试文件,这里就会如下图所示。

若源文件和测试文件需要自己添加的话,这里开始创建源文件和测试文件。添加设计文件则右击工程界面右侧Explorer栏的Source,选择New File,新建两个文件:fir.h和fir.c。

然后在文件中添加代码,并保存文件。

(9)设置顶层函数名。单击Project->Project settings,然后选择Synthesis,在Synthesis Settings界面中设置Top Function为Fir,点击OK

这里熟悉一下GUI

Setp2: 验证C设计文件

一个HLS工程的第一步时验证C代码是否正确,这个过程叫做C验证或者C仿真。这里在Test Bench 下,双击fir_test.c。在Auxiliary pane中的Outline窗口,选择main()即可跳转到main()。

(10)点击run c simulation按键或者Project->Run C Simulation去编译执行C Design。

或

Step3 高层次综合

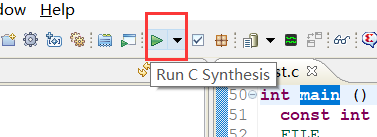

(10) 综合工程。单击工程界面上方的综合按钮。

或

(11)综合结束后,工程界面会自动出打开一个Report文件,可以查看延时、等待时间、资源占用及接口类型等信息。在outline窗口点击Performance Estimates。

在图中可以看到时钟周期设置为10ns,但Vivado HLS的目标时钟周期为目标时间减去时钟不确定度(本例中为10.00-1.25 = 8.75ns)。

时钟不确定性(Uncertainty)确保了(在此阶段)由于布局和布线而导致的未知净延迟存在一些时序余量。图中,HLS估计的时钟周期(最坏情况延迟)为8.43 ns,满足8.75 ns的时序要求。

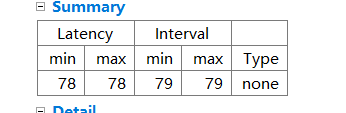

在Summary部分,可以看到:

- 该设计具有78个时钟周期的延迟:输出结果需要78个时钟。

- 间隔为79个时钟周期:在79个时钟之后读取下一组输入。 这是写入最终输出后的一个循环。 这表明设计没有流水线。 此函数(或下一个事务)的下一次执行只能在当前事务完成时启动。

Detail section:

- 此设计中没有子块。 展开“Instance”部分不会显示层次结构中的子模块。

- 所有Latency延迟都是由名为Shift_Accum_Loop的循环综合成的的RTL逻辑引起的。 该逻辑执行11次(trip count)。 每次执行需要7个时钟周期(迭代延迟),总共77个时钟周期,以执行从该循环合成的逻辑的所有迭代(延迟)。

- 总的延迟比环路延迟大一个时钟周期。 它需要一个时钟周期才能进入和退出循环(在这种情况下,设计在循环结束时结束,因此没有退出循环)。

在Outline中点击Utilization Estimate:

在Detail部分,可以看到该设计使用单个存储器实现为LUTRAM(因为它包含少于1024个元素),4个DSP48,以及大约200个触发器和LUT。 在此阶段,设备资源编号是估计值。

- 资源利用率数据是估计值,因为RTL综合可能能够执行其他优化,并且这些数字可能会在RTL综合后发生变化。

- 对于FIR滤波器,DSP48的数量似乎比预期的要大。 这是因为数据是C整数类型,即32位。 它需要多个DSP48才能实现32bit相乘

- 32位数据值。

- “实例”视图中显示的乘数实例显示了所有DSP48。

- 乘数是流水线乘数。 它出现在Instance部分,表明它是一个子块。 标准组合乘数没有层次结构,并列在表达式部分中(表示此层次结构中的组件)。

在Lab3 使用方案优化设计中,可以对这个设计进行优化。

在Outline中点击Interface:

Interface部分表明了端口综合后的IO协议

- Source Object提供了与设计相关的其他端口。 Synthesis已自动添加了一些块级控制端口:ap_start,ap_done,ap_idle和ap_ready。

- Interface Synthesis教程提供了有关这些端口的更多信息。

- 功能输出y现在是一个32位数据端口,带有相关的输出有效信号指示符y_ap_vld。

- 函数输入参数c(数组)已实现为具有4位输出地址端口,输出CE端口和32位输入数据端口的Block RAM接口。

- 最后,输入参数x实现为没有I / O协议(ap_none)的数据端口。

在Lab3中:使用设计优化解决方案解释了如何优化端口x的I / O协议。

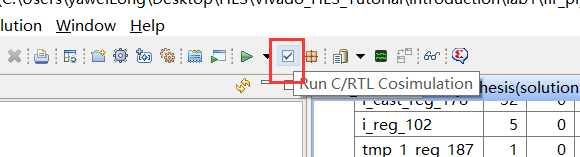

Step 4: RTL 验证

高级综合可以重复使用C测试平台来验证RTL。通过Solution > Run C/RTL Cosimulation或者点击快捷按键执行RTL仿真。

或

RTL协同仿真(cosimulation)的默认选项是调用Vivado仿真器和Verilog RTL执行仿真。 要使用其他模拟器,如VHDL或SystemC RTL执行验证,请使用C / RTL协同仿真对话框中的选项。

当RTL协同仿真完成时,报告将自动在“Information Pane”中打开,控制台将显示如图所示的消息。 这是在C仿真结束时产生的相同消息。

- C测试平台为RTL设计生成输入向量。

- 仿真RTL设计。

- 来自RTL的输出向量被反馈到C测试平台,并且测试平台中的结果检查验证结果是否正确。

- 如果测试平台返回值0,Vivado HLS表示仿真通过。它是测试平台中返回变量的值,仅此一项,表明仿真是否成功。 重要的是,只有在结果正确的情况下,测试平台才会返回值0。

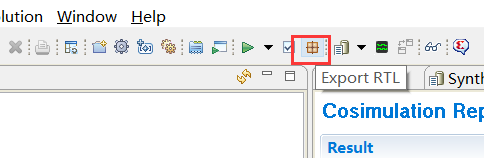

Step 5: IP Creation

高级综合流程的最后一步是将设计打包为IP块,以便与Vivado Design Suite中的其他工具一起使用。通过快捷按钮或者Solution > Export RTL

或

选择IP Catalog,IP打包程序为Vivado IP目录创建包。 (下拉菜单中提供的其他选项允许您为System Generator for DSP创建IP包,为Vivado创建合成检查点格式,或者为Xilinx Platform Studio创建Pcore。)

在Explorer中展开Solution1,展开“导出RTL”命令创建的impl文件夹。展开ip文件夹,找到打包为zip文件的IP,准备好添加到Vivado IP Catalog。

【注意】:在上图中,如果展开impl文件夹中的Verilog或VHDL文件夹,则可以在Vivado Design Suite中打开Vivado项目。

此Vivado项目仅作为分析Vivado IDE内部设计的便捷方式提供。 此项目不应用于实现您的设计:此项目中没有顶级IO缓冲区。 在自己的设计中使用Vivado HLS输出的推荐方法是将IP包或其他输出格式之一合并到您自己的Vivado项目中。 本指南中的其他教程演示了如何在项目中将Vivado HLS输出用作IP。

8156

8156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?