xilinx zynq(一)

简介

本文介绍Xilinx Zynq开发,参考《Xilinx Zynq Soc与嵌入式Linux设计实战指南》,为学习笔记。内容介绍Zynq PS(Arm Cortex-A9)设计和开发。

一、Zynq 组成 PL & PS

1.1. PL的开发流程

本文主要介绍Xilinx Zynq-7000和Zynq-7010处理器,Zynq芯片内部分为两部分,PS(Process System)和PL(Programmable Logic),

创建工程、设计输入、设计、下载执行。

1.2. PS的开发流程:

建立Zynq硬件系统、PS端设计hello world、下载执行。

二、Zynq 硬件平台和集成开发环境

2.1. Zynq XC7Z020芯片资源

- PS部分资源

双核Cortex-A9多核处理器(ARM-v7);

32KB 命令Cache;

32KB 数据Cache;

512KB 共享L2 Cache;

PL到PS的加速器一致性端口(ACP);

64位高级可扩展端口(AXI);

256KB 片上存储(OCM);

DMA和中断控制器(GIC);

看门狗定时器和三重计数器/定时器;

DDR3、DDR2或者LPDDR-2、支持4线SPI控制器

支持8/16/32 i/o 宽度NAND flash.支持8位数据宽度,最大25个地址信号SRAM/NOR存储器;

54个GPIO信号引脚(MIO连接);

2个三模式以太网控制器;

USB控制器;

SD/SDIO控制器;

SPI控制器;

CAN控制器;

UART控制器;

I2C控制器;

- PL资源

可编程逻辑块(CLB);

32KB RAM;

时钟管理;

DSP48E1;

可配置I/O;

模数转换(ADC);

集成PCIe模块;

本文以PS为核心进行嵌入式系统设计,将PL作为PS的外设。

2.2. Zynq软件—XPS

XPS作为嵌入式硬件开发工具,是Xilinx推荐使用用来构建程序。

嵌入式PS硬件部分设计完成生成system.bit文件,可下载到Zynq的PL中。

2.3. Zynq软件—XPS

2.3. 嵌入式开发工具—SDK

三、Zynq 启动流程、启动镜像制作方法

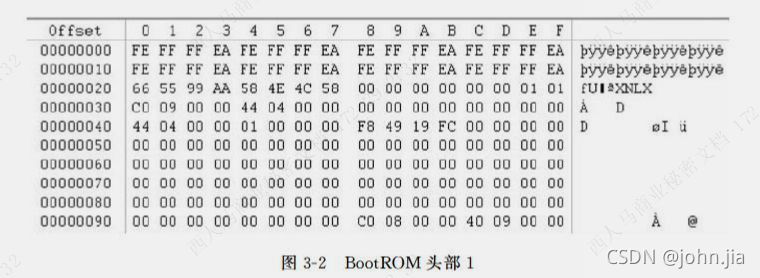

3.1. BooTROM

Zynq启动首先是BootROM。Zynq是可扩展处理平台,简言之是A9双核处理器带有一个FPGA外设。zynq的启动也和主流ARM处理器启动类似,支持JTAG、NAND、parallel NOR、Serial NOR(QSPI)、SD卡。

zynq启动配置步骤包含三个阶段:

阶段0:器件上电后自动执行片内BootROM中代码,上电复位或者热复位后,处理器执行的不可修改的代码,PS采样专用boot strapping signals引脚电平决定是从什么存储介质引导Zynq,加载相应NAND、NOR、QSPI驱动,启动PS配置;

阶段1:BootROM初始化CPU和部分外设后,读取下一个启动程序FSBL,用户可定义的代码;

阶段2:有操作系统的启动引导程序(SSBL),这个阶段代码完全是用户控制实现,对嵌入式Linux而言,这个阶段就是u-boot。

Zynq在非安全启动模式下,PS作为主设备。PS的启动配置步骤:

设备上电复位;

BootROM执行;

读启动模式;

确定引导程序存储所在存储器;

读启动头部,确定加密状态和镜像;

BootROM使用DevC的DMA,将第一阶段的启动引导程序FSBL加载到OCM;

关闭BootROM,释放CPU用于控制FSBL;

FSBL通过PCAP加载PL bit流;

PS作为主设备安全启动步骤:

设备上电复位;

BootROM执行,读自举程序,确定外部存储器接口;

BootROM加载一级引导启动程序FSBL;

PL使用PCAP将界面的FSBL返回给PS,然后加载到OCM;

关闭BootROM,释放CPU用于控制FSBL;

FSBL通过PCAP,加载PL bit流。

PS JTAG级联非安全启动

3.2. BootGen

BootGen是Zynq AP SOC processor 创建引导镜像的工具,BootGen可直接添加镜像文件里头部、分区表头文件,也可对镜像加密。BootGen输出一个.bin二进制文件,可以进行直接少些启动引导存储器里引导Zynq。

BootGen集成到SDK软件里,可通过图形化界面生成启动镜像。

感谢阅读,祝君成功!

-by aiziyou

3416

3416

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?