Vivado IP核使用之RAM实验

RAM简介

RAM的英文全称是Random Access Memory,即随机存取存储器,它可以随时把数据写入任一指定地址的存储单元,也可以随时从任一指定地址中读出数据,其读写速度是由时钟频率决定的。RAM主要用来存放程序及程序执行过程中产生的中间数据、运算结果等。我们将对Vivado软件生成的RAM IP核进行读写测试,并向大家介绍Xilinx RAM IP核的使用方法。

Vivado软件自带了BMG IP核(Block Memory Generator,块RAM生成器),可以配置成RAM或者ROM。这两者的区别是RAM是一种随机存取存储器,不仅仅可以存储数据,同时支持对存储的数据进行修改;而ROM是一种只读存储器,也就是说,在正常工作时只能读出数据,而不能写入数据。

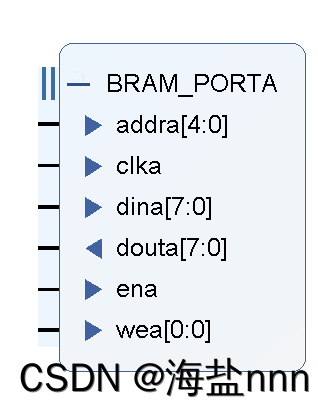

各引脚的意义分别为:

douta ram读数据

ena ram使能

wea 读写选择

addra 读写地址

dina ram写数据

实验过程

本次实验平台基于正点原子领航者ZYNQ开发板

代码等教程均参考正点原子ZYNQ系列教程

实验任务

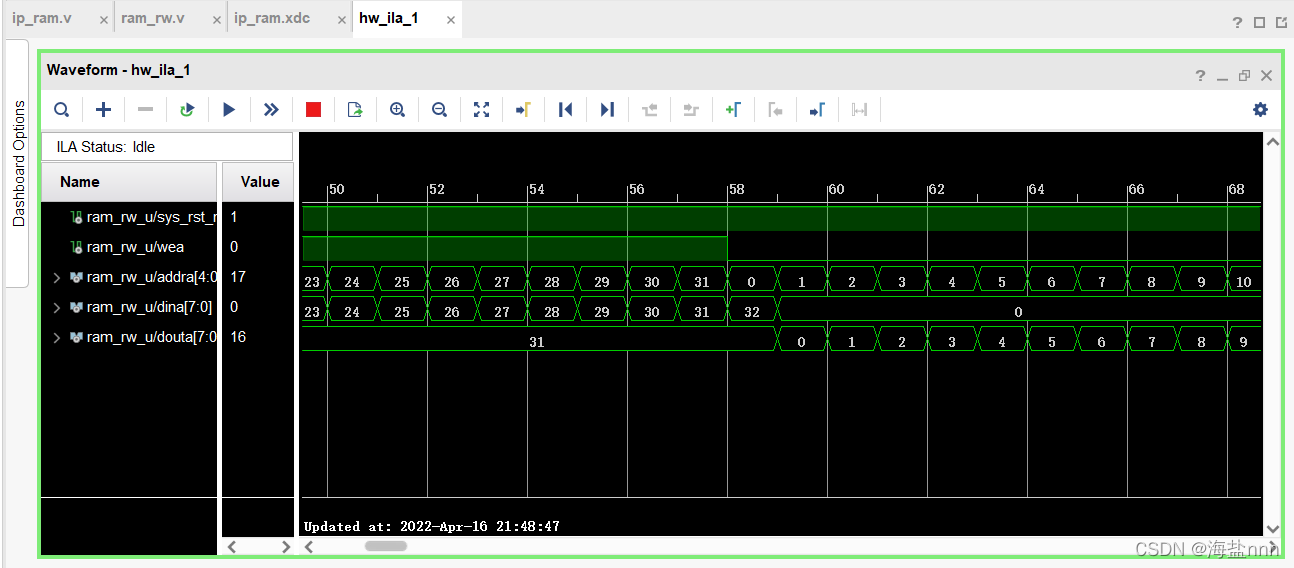

本节实验任务是使用Xilinx BMG IP核,配置成一个单端口的RAM,然后对RAM进行读写操作,通过在Vivado自带的仿真器中观察波形是否正确,最后将设计下载到领航者Zynq开发板中,并使用ILA对其进行在线调试观察。

实验程序

顶层代码

分别例化了RAM IP核以及子程序ram_rw

module ip_ram(

input sys_clk,

input sys_rst_n

);

ram_rw ram_rw_u(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.douta (douta),

.ena (ena),

.wea (wea),

.addra (addra),

.dina (dina)

);

wire ena ;

wire wea ;

wire [4 : 0] addra ;

wire [7 : 0] dina ;

wire [7 : 0] douta ;

blk_mem_gen_0 blk_mem_gen_0u (

.clka(sys_clk), // input wire clka

.ena(ena), // input wire ena

.wea(wea), // input wire [0 : 0] wea

.addra(addra), // input wire [4 : 0] addra

.dina(dina), // input wire [7 : 0] dina

.douta(douta) // output wire [7 : 0] douta

);

endmodule

ram_rw

module ram_rw(

input sys_clk ,

input sys_rst_n ,

input [7:0] douta , //ram读数据

output ena , //ram使能

output wea , //读写选择

output reg [4:0] addra , //读写地址

output reg [7:0] dina //ram写数据

);

assign ena = sys_rst_n;

assign wea = (cnt<=6'd31&&ena==1'b1)?1'b1:1'b0;

reg [5:0] cnt;

//0-63计数器

always@(posedge sys_clk,negedge sys_rst_n) begin

if(!sys_rst_n)

cnt<=0;

else if(cnt<6'd63)

cnt<=cnt+1;

else

cnt<=0;

end

//生成ram要写的数据 cnt前半个周期写数据

always@(posedge sys_clk,negedge sys_rst_n) begin

if(!sys_rst_n)

dina<=8'b0;

else if(cnt<=6'd31)

dina<=dina+1'b1;

else

dina<=8'b0;

end

//ram读数据地址 cnt后半个周期

always@(posedge sys_clk,negedge sys_rst_n) begin

if(!sys_rst_n)

addra<=5'b0;

else if(cnt==5'd31)

addra<=0;

else

addra<=addra+1'b1;

end

//ila逻辑分析

ila_0 ila_0_u (

.clk(sys_clk), // input wire clk

.probe0(ena), // input wire [0:0] probe0

.probe1(wea), // input wire [0:0] probe1

.probe2(addra), // input wire [4:0] probe2

.probe3(dina), // input wire [7:0] probe3

.probe4(douta) // input wire [7:0] probe4

);

endmodule

仿真结果

ILA真好用!

285

285

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?