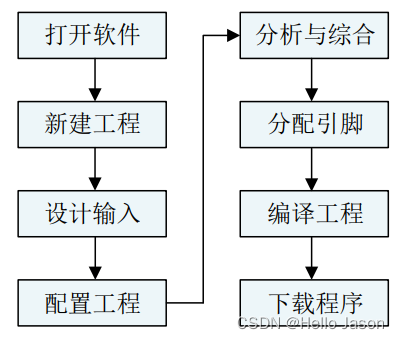

使用流程图总结图:

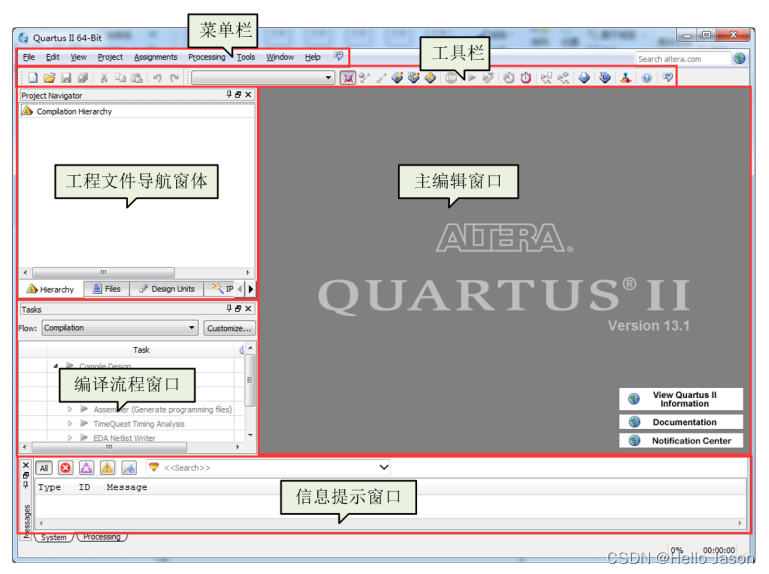

一、打开软件

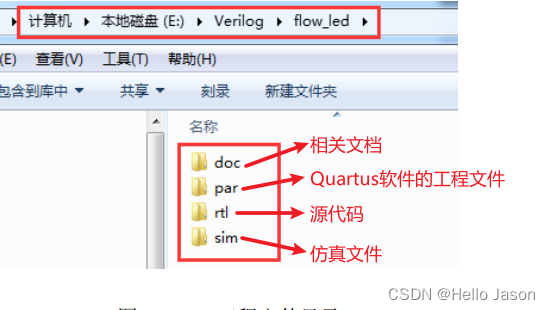

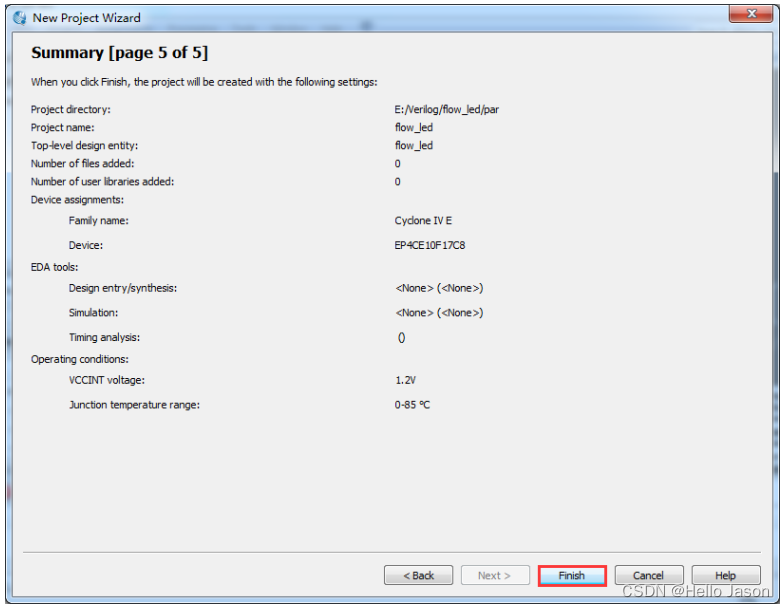

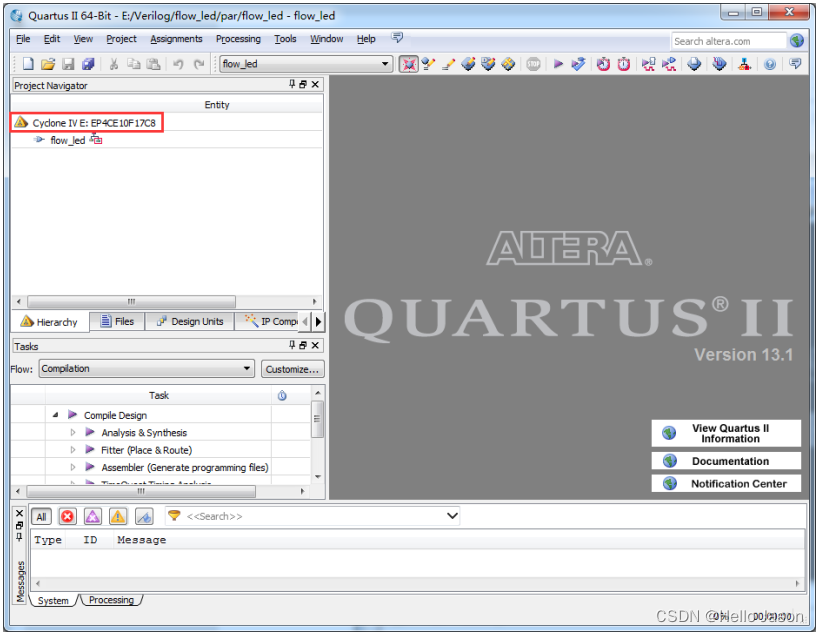

二、新建工程

1、创建目录

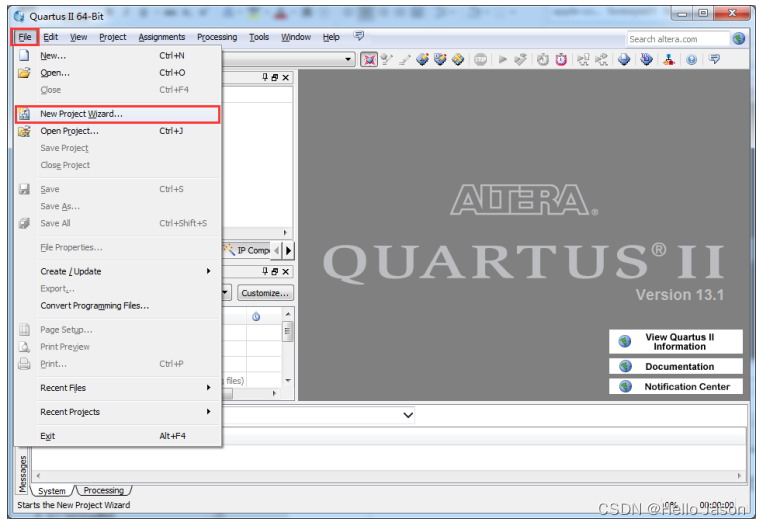

2、创建工程

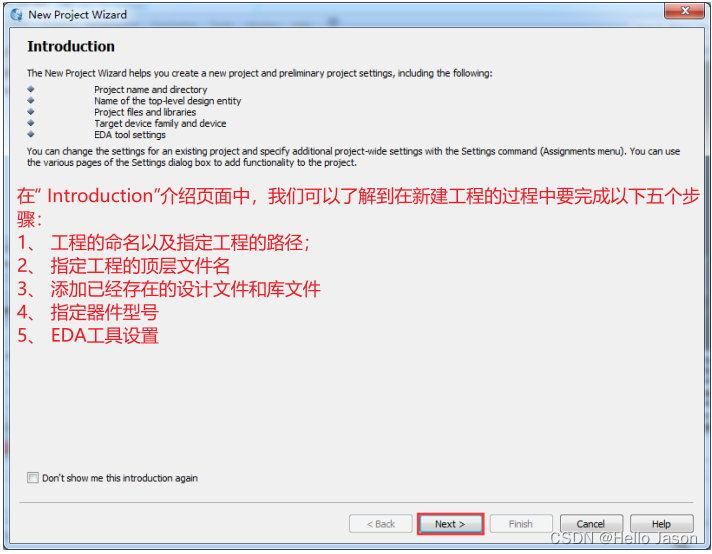

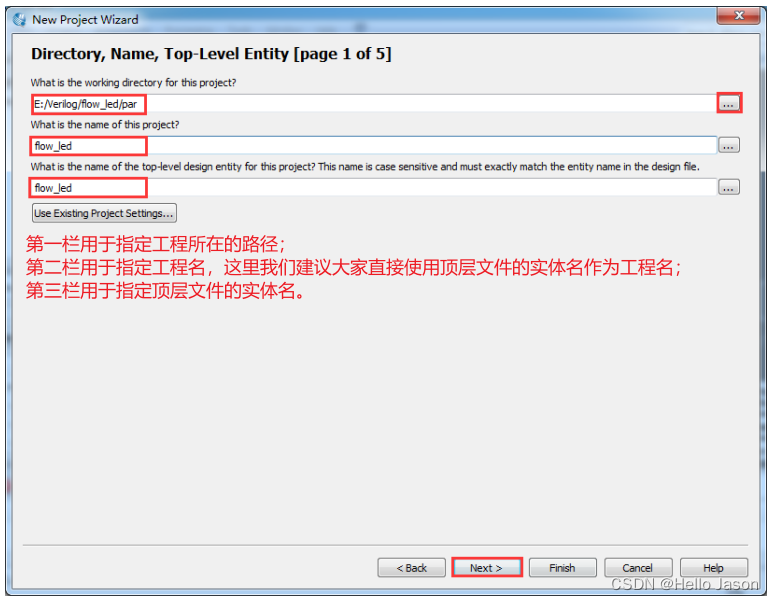

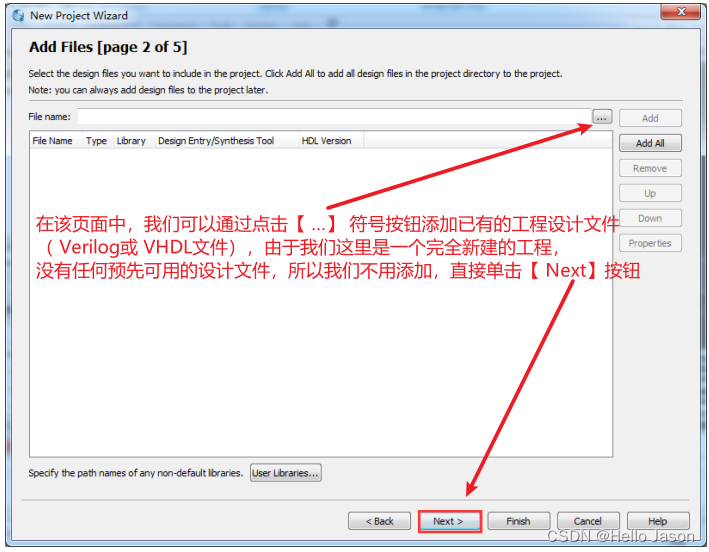

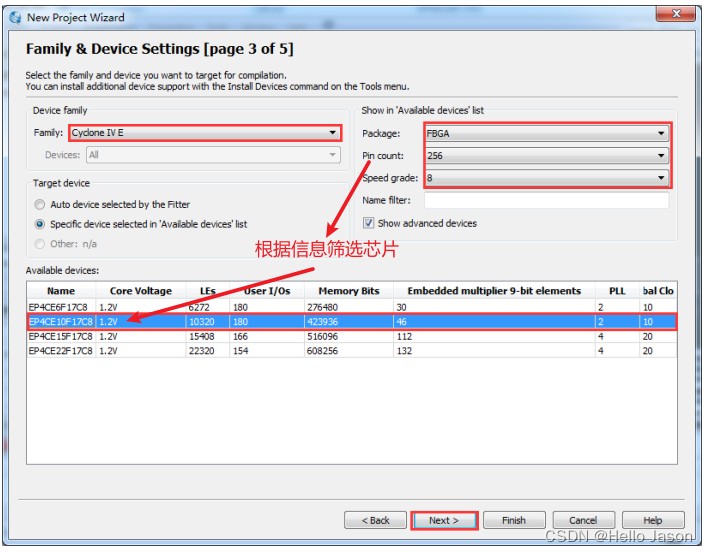

选择【 File】→【 New Project Wizard…】来新建一个工程

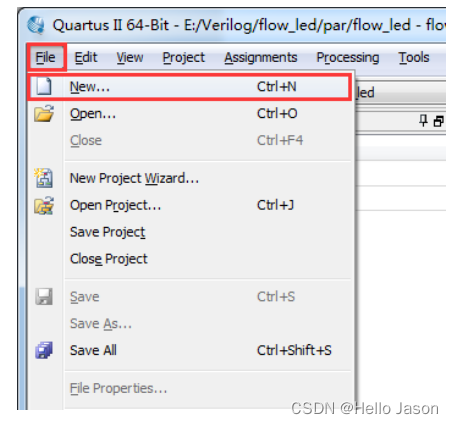

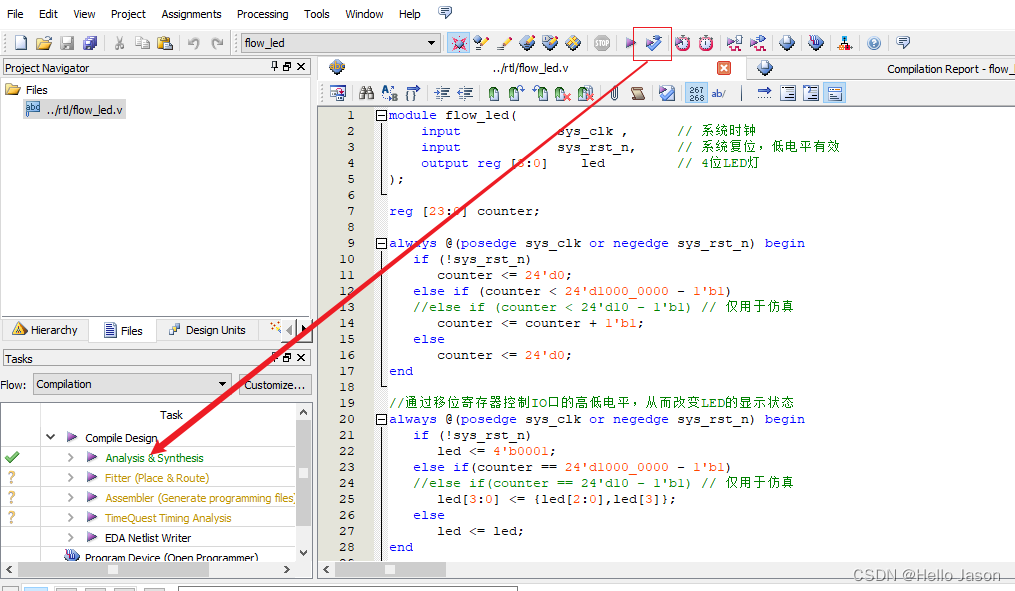

三、设计输入

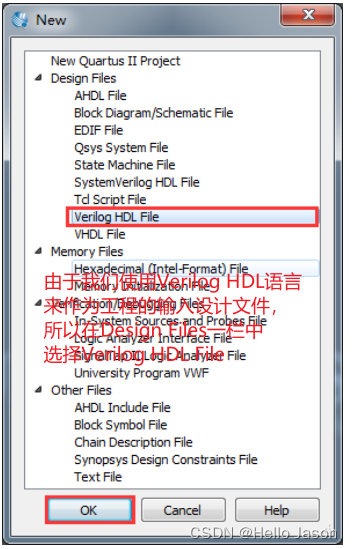

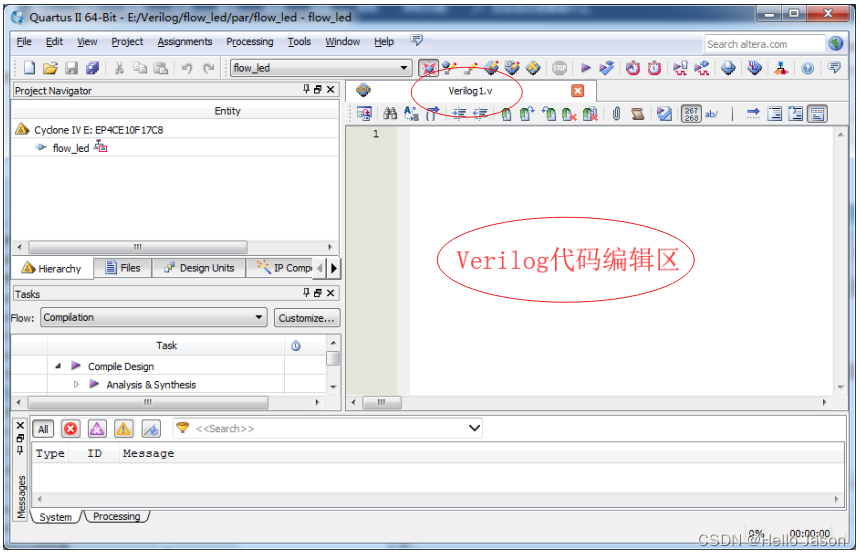

【 File】→【 New】

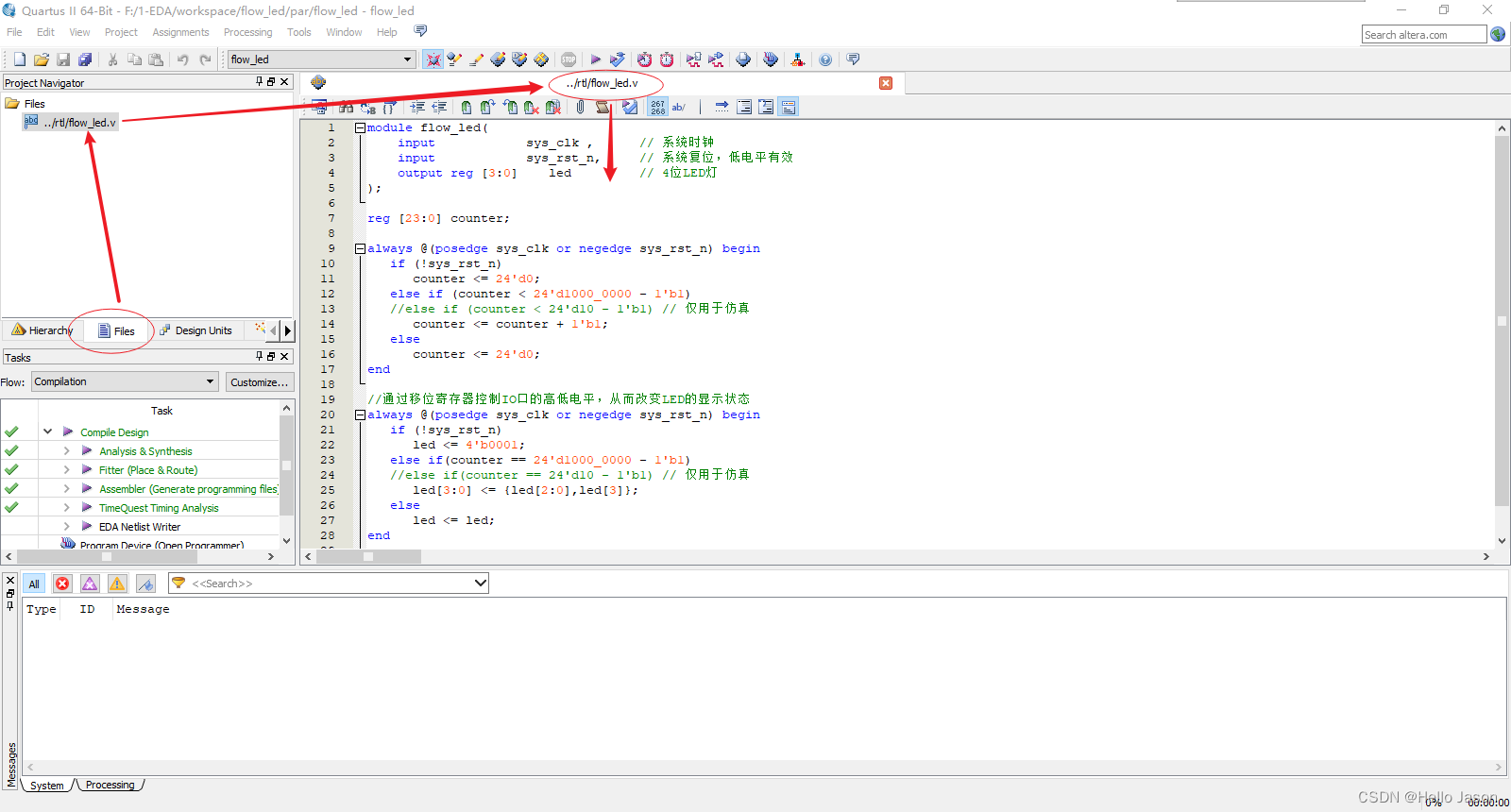

输入代码:

module flow_led(

input sys_clk , // 系统时钟

input sys_rst_n, // 系统复位,低电平有效

output reg [3:0] led // 4位LED灯

);

reg [23:0] counter;

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 24'd0;

else if (counter < 24'd1000_0000 - 1'b1)

//else if (counter < 24'd10 - 1'b1) // 仅用于仿真

counter <= counter + 1'b1;

else

counter <= 24'd0;

end

//通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4'b0001;

else if(counter == 24'd1000_0000 - 1'b1)

//else if(counter == 24'd10 - 1'b1) // 仅用于仿真

led[3:0] <= {led[2:0],led[3]};

else

led <= led;

end

endmodule

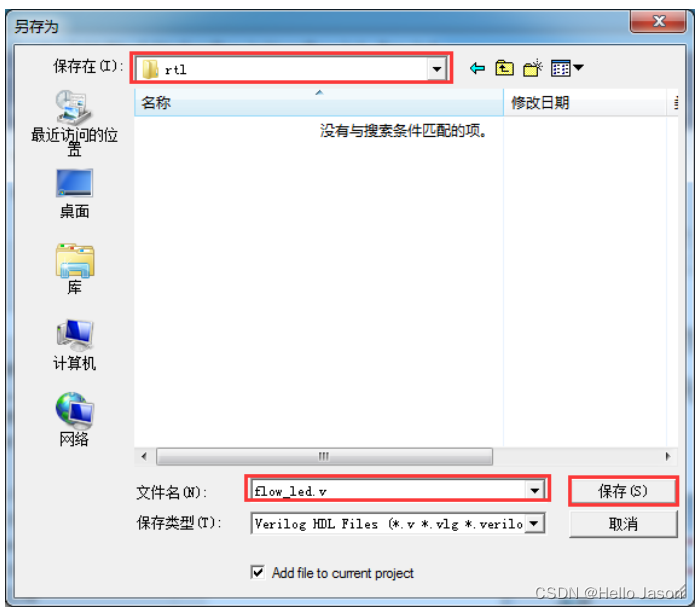

代码保存到rtl目录

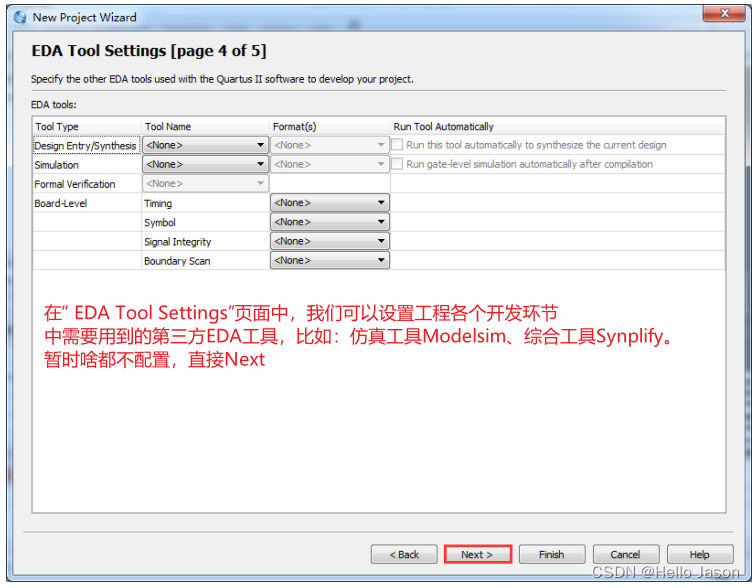

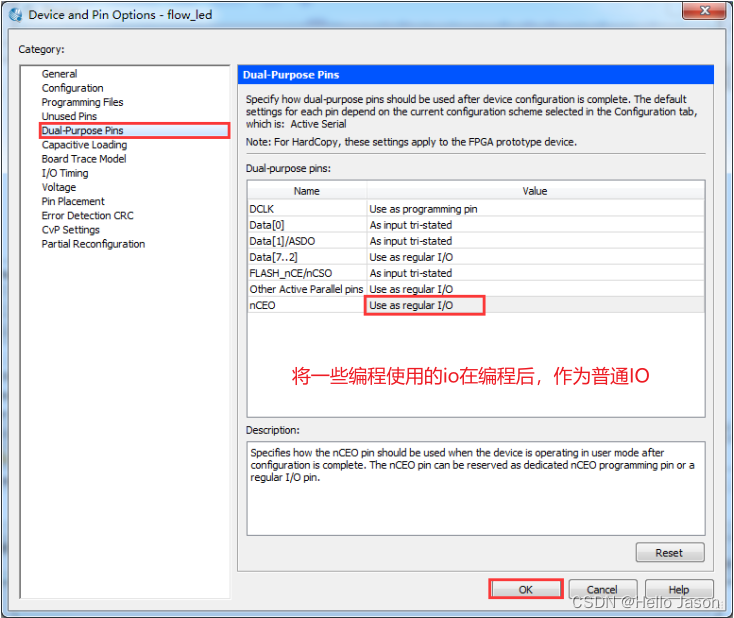

四、配置工程

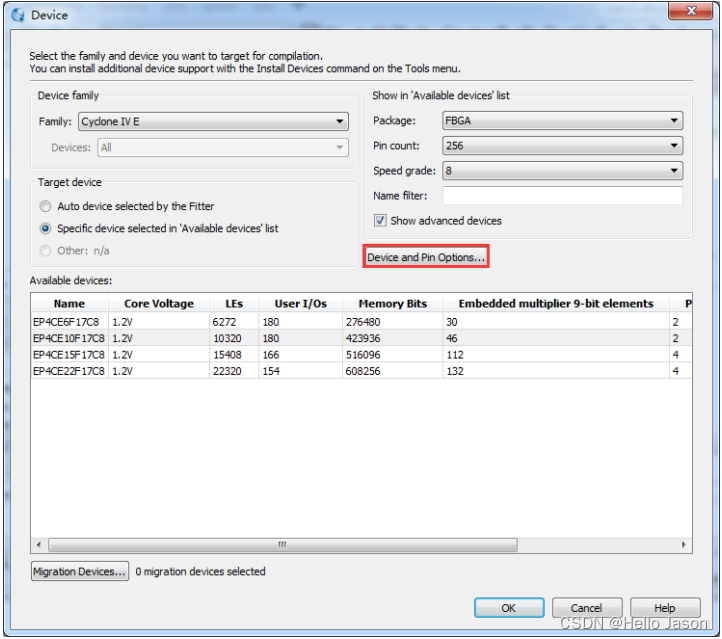

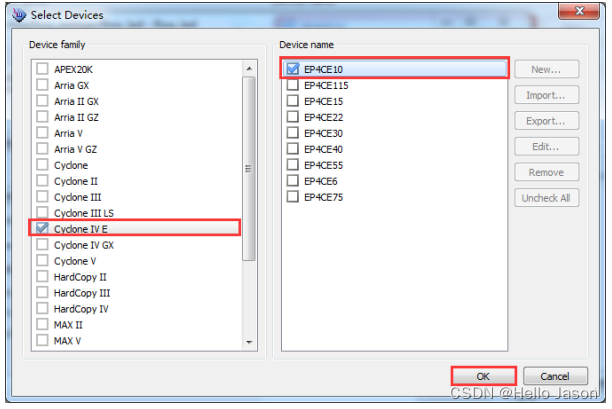

【 Assignments】→【 Device...】

五、分析与综合( 编译)

【 Analysis & Synthesis】进行语法检查编译

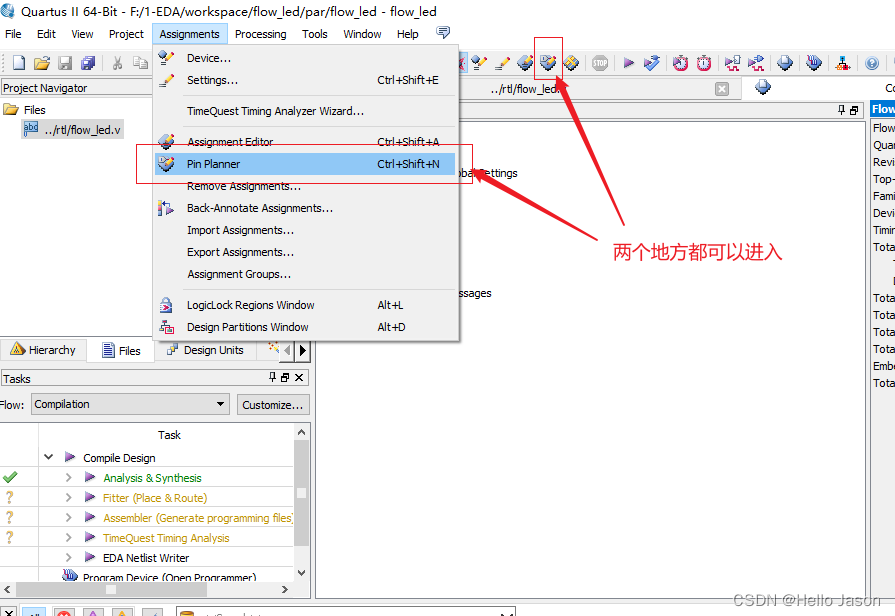

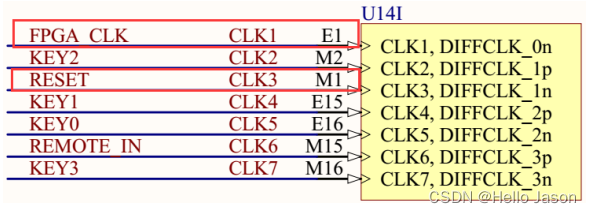

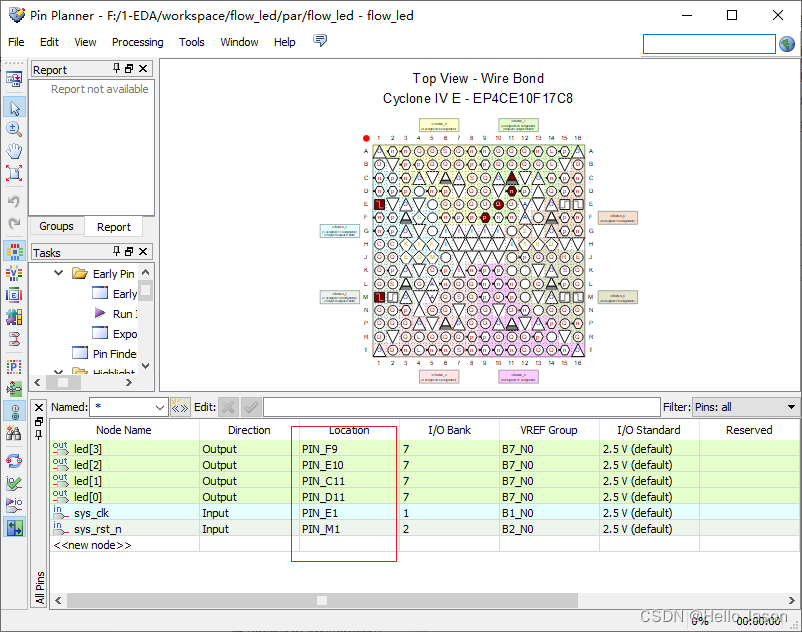

6、分配引脚

根据原理图配好下面管脚

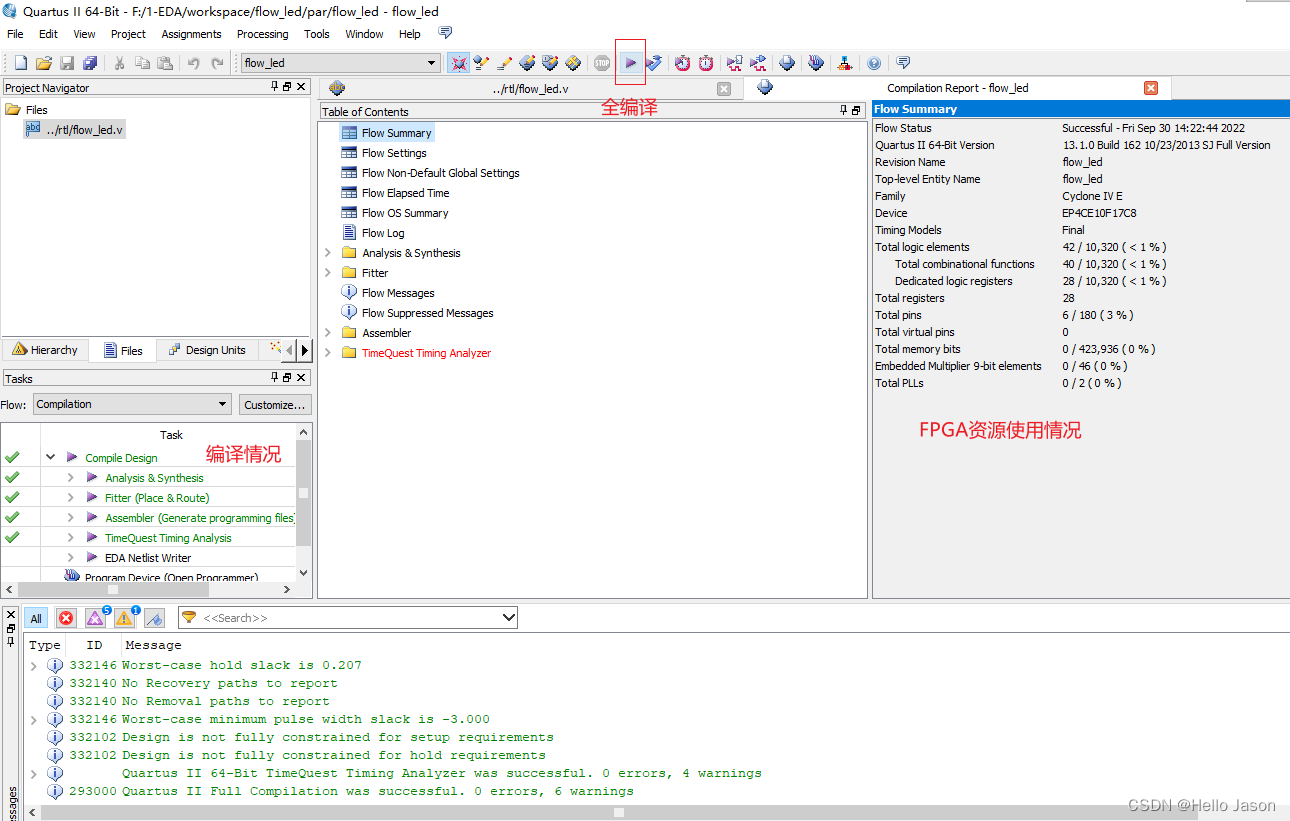

七、 编译工程

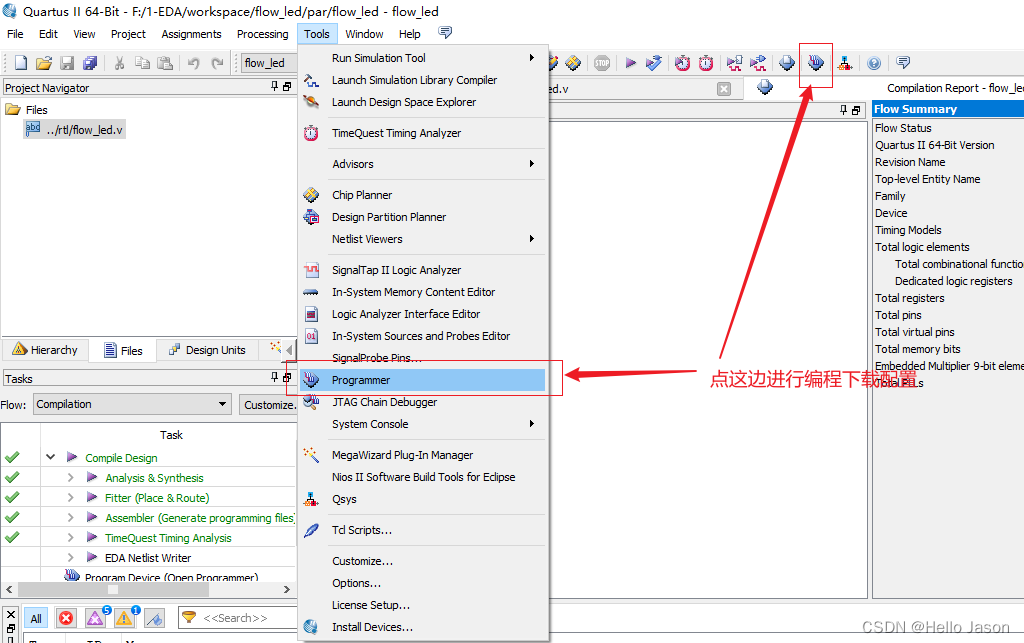

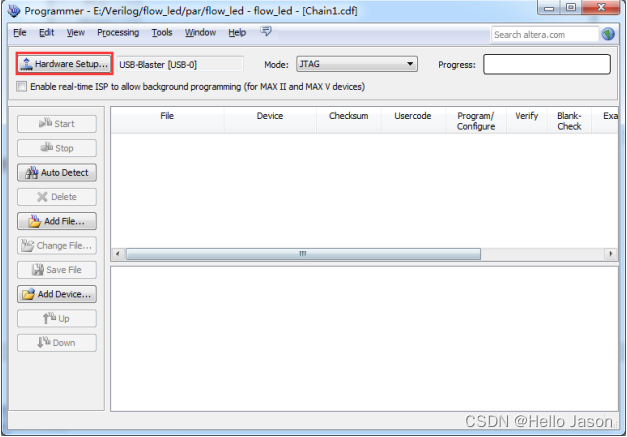

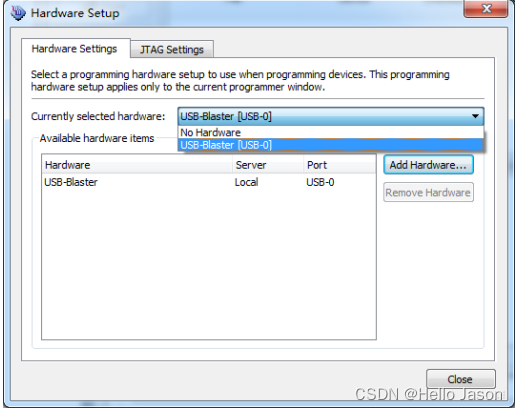

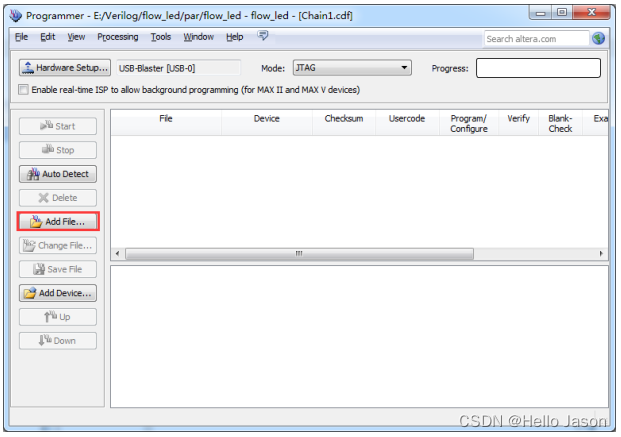

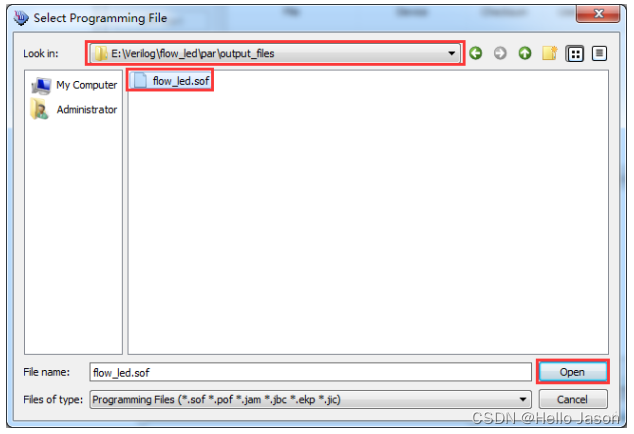

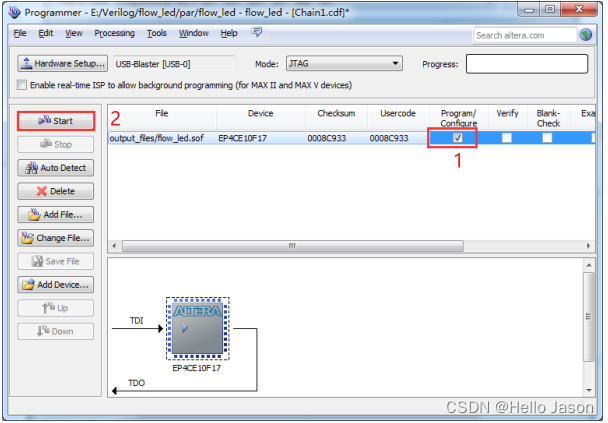

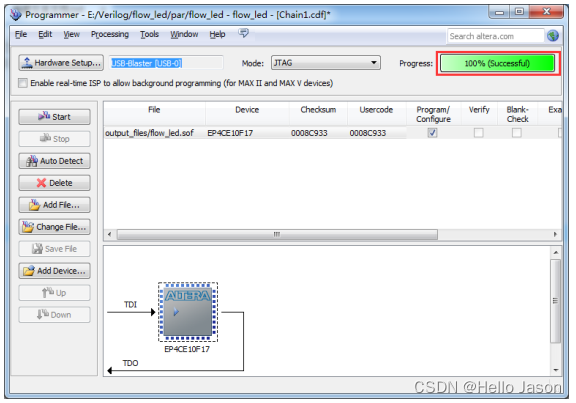

八、下载程序

这里下载的程序是.sof文件格式,开发板断电后程序将会丢失。

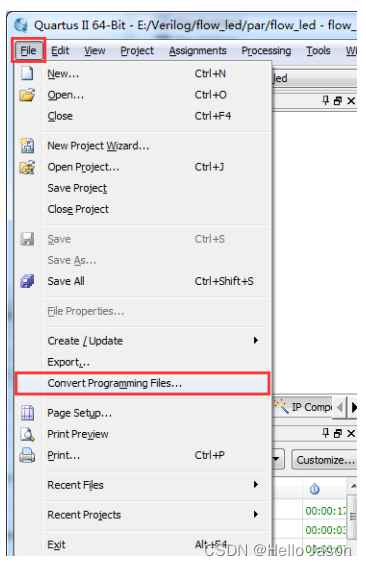

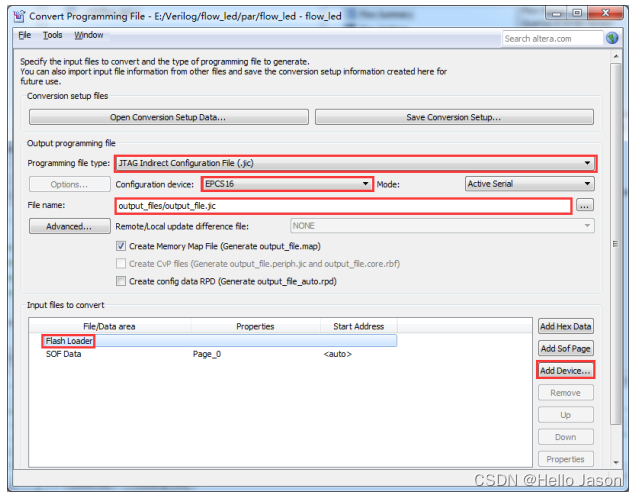

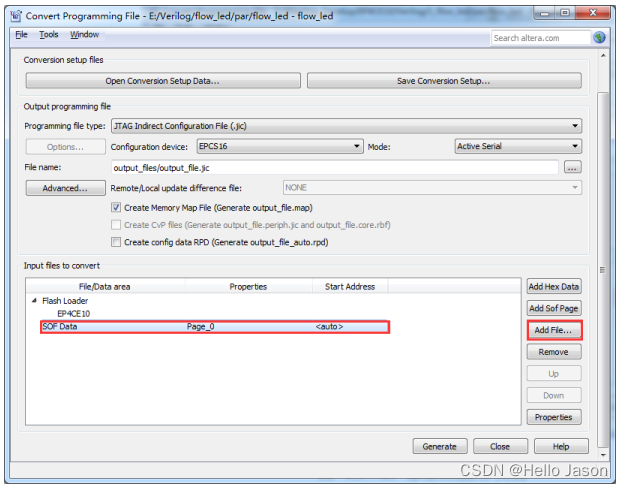

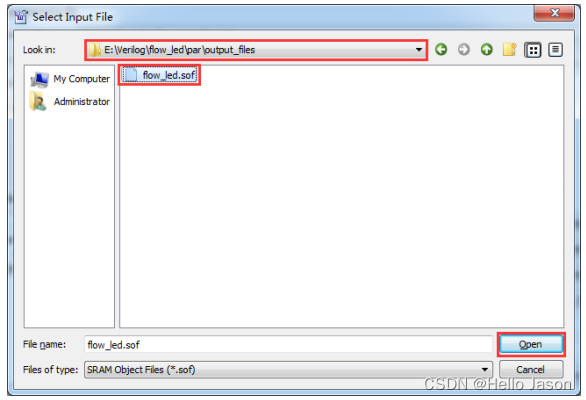

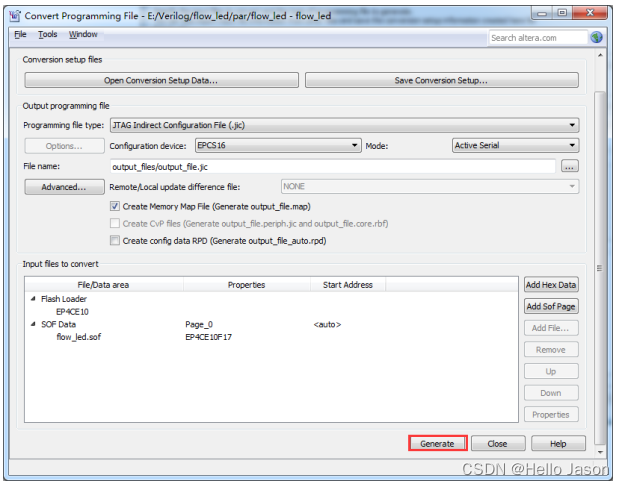

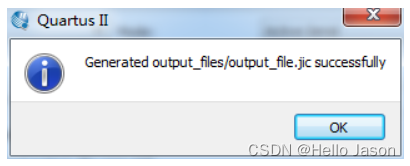

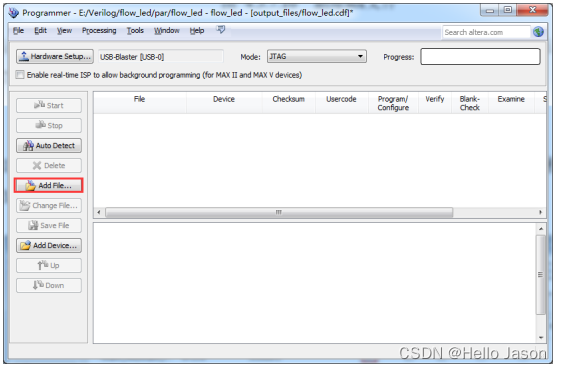

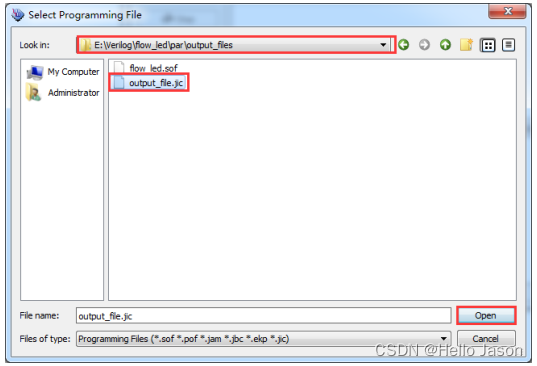

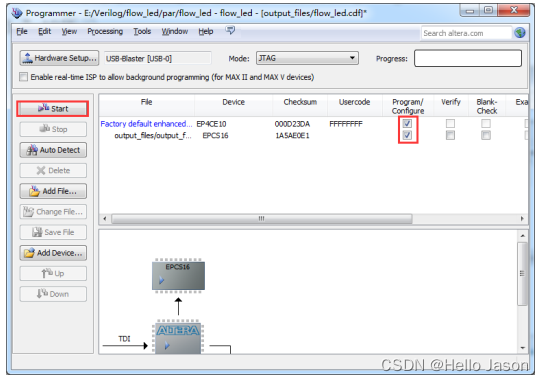

九、固化程序

如果我们想要程序断电不丢失的话, 就必须将程序保存在开发板的片外Flash中, Flash的引脚是和FPGA固定的引脚相连接, FPGA会在上电后自动读取Flash中存储的程序,这个过程不需要我们编写驱动代码和人为干预,只需要通过JTAG下载jic文件即可。需要注意的是, jic文件不是软件自动生成的, 而是需要我们手动的将sof文件转换成jic文件。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?