首发于数据转换器学习与设计

本文想着重阐述下TDC (Time to Digtial Converter)。

TDC的基本结构是什么样的?虽然笔者在前面的文章提及过些概念,但是如果没有一个基本概念和实际系统/电容架构的话,大家理解起来也就没有那么直观(换个写文的逻辑,或许会有不一样的效果)。

参考文献:

- Quantization noise improvement of time to digital converter (TDC) for ADPLL;

- Overview on Phase Noise and Jitter. Technical Overview. Keysight EEs of EDA;

- (Springer Series in Advanced Microelectronics 29) Stephan Henzler (auth.) - Time-to-Digital Converters-Springer Netherlands (2010);

笔者一开始对TDC认知只是停留下Isacco Arnaldi那本书Voltage to Phase Quantizer的几个仿真案例而已。可对知识的好奇心使然,逐步想对这个TDC概念想有个更加清晰地认知。幸运地是,有一本《Time to Digital Converter》用来专门讲述TDC,这下就来了兴致。该书百来页,花上点时间,细细品读一会儿,还是很有意思的。有兴趣地读者,可以搞来看看,尤其是做数字电路设计的,或许哪天需要跟模拟的兄弟姐妹们混合搭档,干把高速高精度的大票。

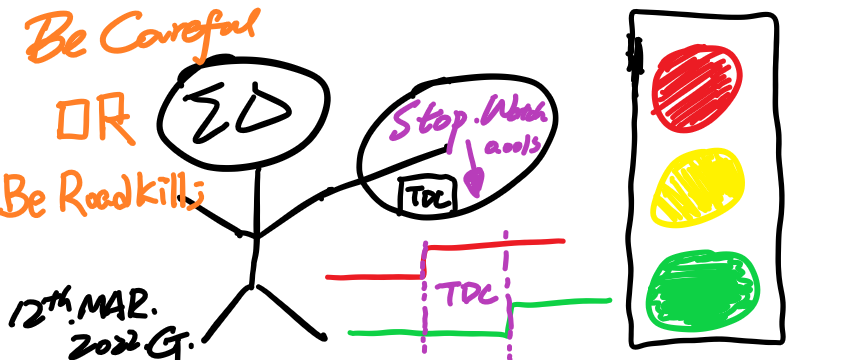

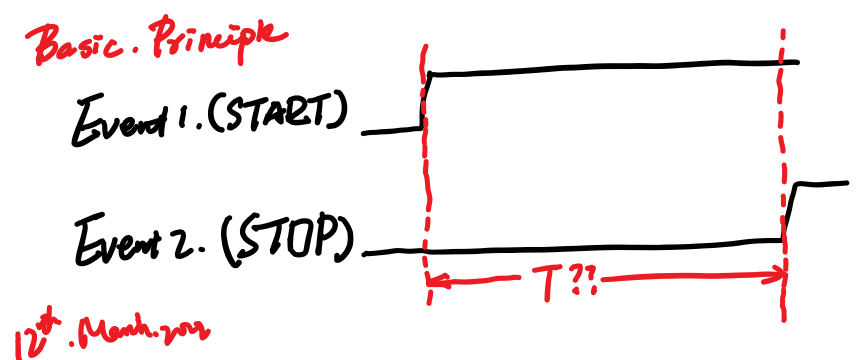

首先我们可以追溯下TDC的基本原理。试想有两个你想测试的信号,一个START,一个STOP,那么TDC的作用就是将这个START与STOP的时间差用数字信号方式表征出来。原理的源头逻辑就是需求,TDC的功能满足这个需求而已。那么,看到下面图示中的两个事件,该如何测量呢?毫无疑问,对于两者的长度量上来说,如果有一把尺子的话,我们量一下两者之间的差异长度即可。因此,时间维度上,同理上需要一把时间刻度的尺子而已。类比于尺子的刻度,时间刻度的尺子,同样具备一样的性质,比如测试时间范围(Dynamic Range)、时间最小刻度(TLSB)等。

Figure 1. 两个事件(或是多个事件)之间的时间如何测量

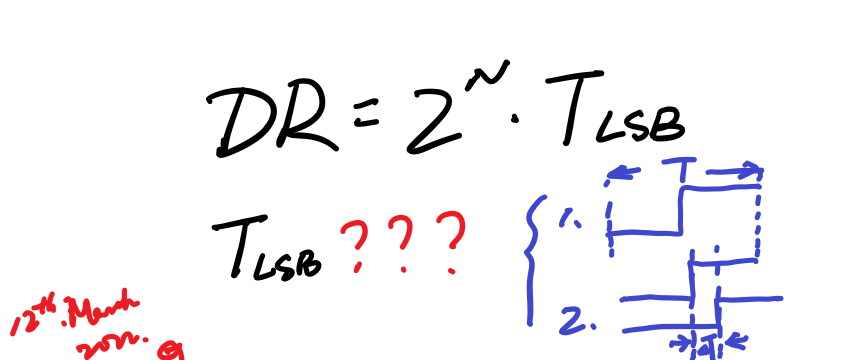

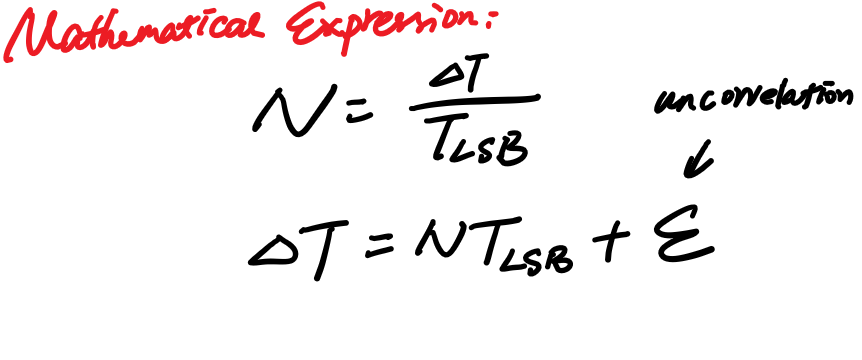

那么,该如何去定义这把标准的“时间尺子”呢?朋友们,注意啦!时光易逝永不回,它是具备单调性的。因此,你不可能像常规ADC那样,去定一个标准的参考值,比如参考电压值,作为自己的测试范围,再根据所需位进行最小LSB的定义。时间上,则是逆过程,你定义了一个最小时间刻度,在这个基础上的演绎即是测试范围(见下图的数学表达式)。那么问题就到了,如何给出一个最小时间刻度呢?示意图中给出了两个方式的定义。我们先讲解第一个,那就是一个标准的周期T。

Figure 2. 最小时间刻度与测试范围示意

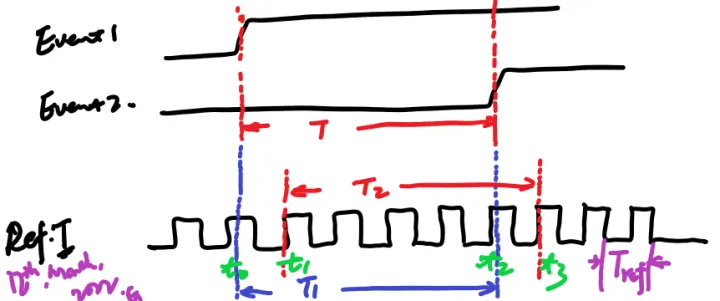

至此,有了想要干的事情(测试两个时间事件的时间)和一把刻度为T的“时间尺子”。那么,此时一个粗糙的“TDC”(脉冲计数)就应该隆重登场,完成它的使命了!

Figure 3. 脉冲计数基本原理

如图所示,如果拥有一个完美的“尺子”,那么T1(t2-t1)即为所测时间。可现实是骨感的,你不能在别人持续在一个电平上时,还能分辨它的位置。就好比是一个mm刻度的尺子,你能够读出了个0.1mm位,那么这个位是个估算位。实际情况是,通过上升沿来决定开始位与结束位。那么读出来的数就是T2。

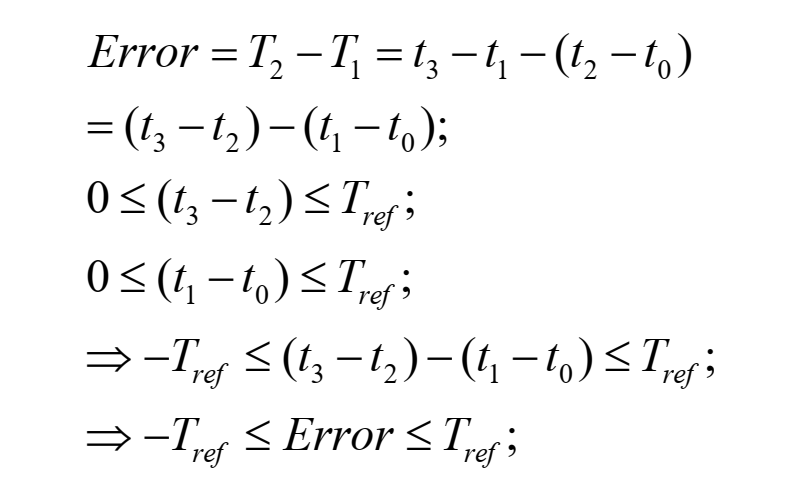

那么,这个T2的准确度如何评估呢?总不能说测个大概就满足了,而是要知道差距在哪里。

这个数学表达式的最直接解释就是,如果碰巧需要测试的时间中第一个上升沿的延迟等于结束上升沿的延迟,那么这个测试就是理想的,正好等于整数倍的参考周期。但是,如果不是的话,那么这个误差就是正负下的参考周期。这个时候,大家可以大致计算下,如果需要一个1ns的精度话,那么就需要2GHz的高速电路。想要更好地精度(思考下,为何需要精度更高呢?哪些领域需要高精度到ps级别的呢?)的话,那该怎么办?不过,在思考更好精度的架构前,在已有的这个架构下,如果你的两个事件差别很大,这时的TDC还有意义?就好比用一个秒表去测试一个月的工作时间,值得吗?那么,是否需要做一个低碳(缓慢熵增)的过程。

不知道细心地读者有没有发现,这个时候,笔者总要写到一个粗计算(coarse)和一个精计算(fine)的概念(比如在讲解如何学习Sigma-Delta那篇文中点到的ADC进程以及微积分解析Sigma-Delta ADC)。这个概念应用的基本思想是专业的事交给专业的人来做,粗加工与精加工才能做到真正的折中(Trade-off)。好比就是一个人的身高,你非要用一把1cm的尺子在那测量,咱又不是小蚁人,没必要。不知道有没有用过机床(车床、铣床)的读者,你会发现他们一开始的加工都是大刀阔斧的,直到快要接近你的需求精度时,它才开始精加工。或是商场门口那种自动测身高的仪器,当它理你很远的时候,它的下降速度是很快的,等到探测到你的存在时,它才开始逐步下降,直到触碰到你的发根。这些都是Time of Fight(ToF)基本应用。

Figure 4. 粗测量与精测量示意

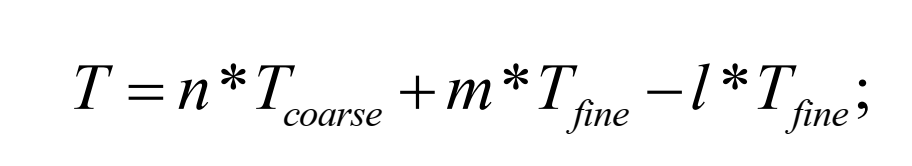

根据上述图示,测试时间的精度是由Tfine来决定。但是这个架构的存在,只是解决了硬件上的浪费问题,并非实现精度上的提升。数学公式如下:

虽然说精度仍然取决于精周期,最坏的精度就是2Tfine。但是大家有没有想过在实际设计的过程,如何设计这个粗周期跟精周期的关系,会降低最坏情况的出现呢?另一方面,虽然这个结构上精度没有提升,但是它的优点在于使得人们把关注点转移点如何去测试两个小的时间偏移量。

那么,在时间上小的偏移量可以理解为相位的差异。因此,PLL的功能是不是就出来了!哇,这下不就把问题全解决掉了嘛!大结局,Happy ending。但是,如果是这样的话,那么为什么直接先用PLL呢?貌似又回到了原点,如果输入很大的话,PLL是否有点过犹不及呢?是的,其实在游标卡尺结构TDC(等价于无需鉴频的PLL)之前。人们还从一个放大时间的角度去设计TDC。主要的原理还是将时间转换为幅值的方式,这一点通过基本元开关与电容即可实现,尤其是通过设定电容的大小,来放大充放电时间。有兴趣的读者,可以理解下面这个图(Ref. 3)。具体公式也可以参考文献3,不赘述。

Figure 5. Block diagram of analog TDC based on dual-slope analog-to-time-interpolation. Ref[3]

那么,是否可以从纯数字角度去考虑TDC的结构呢?回答当然是可以的。因为之前的阐述就表明了,如果纯粹在模拟角度来思考的话,除了精妙的架构以外,精度上基本被限制和局限了。换个角度来说,也正是由于数字的高速发展,才使得TDC应用和更新迭代来得更宽泛、更快。

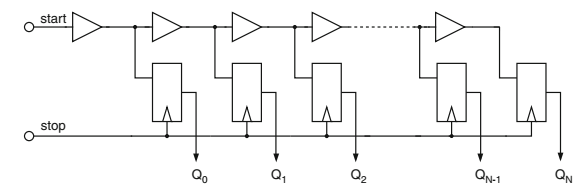

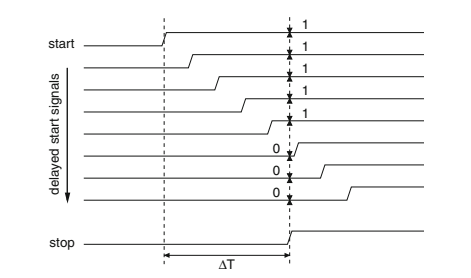

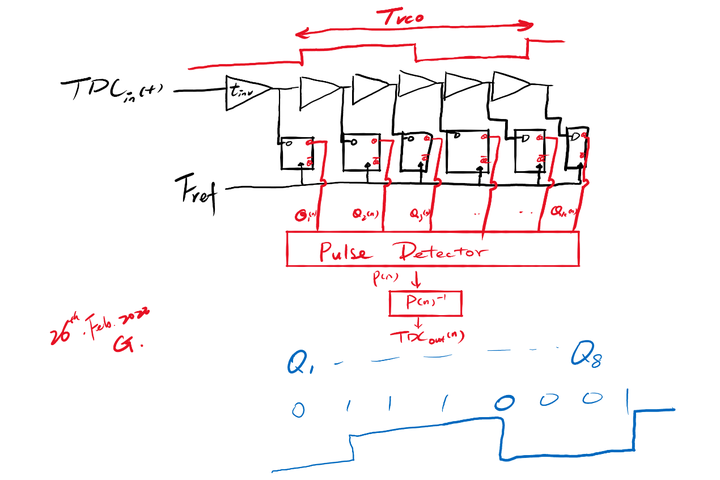

下图的TDC结构是建立在R.Nutt1968年提出的延迟线结构基础之上,利用信号通过逻辑门电路的绝对传输时间提出的一种时间测量方法。Delay Line由多个BUffer单元组成,buffer加Stop的信号用来进行Flip-Flop的触发。当脉冲结束后,Flip-Flop记录的Buffer单元数即为测试时间。基本操作如下图6所示。其实到这里,大家可以看到,基本的原理跟前面阐述的保持了一致性。

Figure 6. Implementation of a basic delay-line based time-to-digital converter (DL-TDC). Ref[3]

Figure 7. 基本DL-TDC工作原理(温度码)

Figure 8. DL-TDC数学属性

========美丽的分割线!========

写完基本测试需求下的设计逻辑后,本想止文在此。因为后面的TDC结构演化都是一个逐步的完善和递进过程,希望读者能够花点自己的时间在这个上面,用来细细琢磨!另外,我们在之前的两篇文章中提及的TDC,其实是为了Sigma-Delta ADC来服务的。TDC在本专栏中的涉及内容应该包括它作为一种VCO-TDC量化器的存在,它的线性模型如何?能不能用数学的方式分析下它的噪声特性,等等。

Figure 9. DL-TDC基本结构

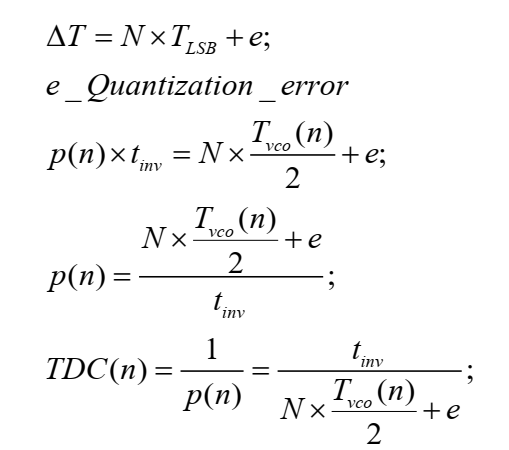

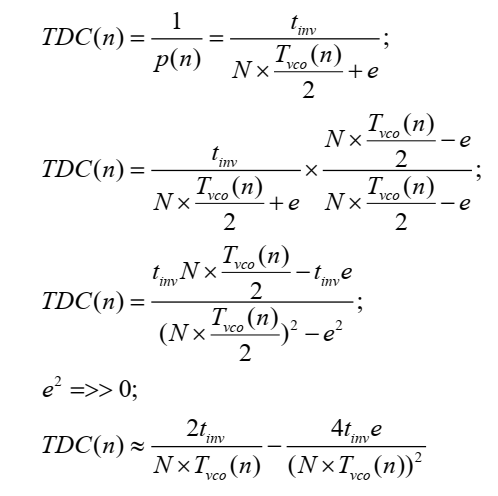

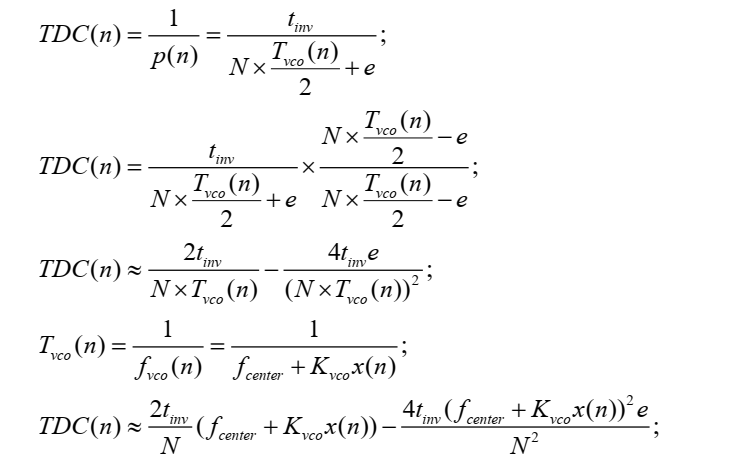

结合上面的图与上面DL-TDC数学属性。接下来,就在一个线性系统下,去完成TDCout(n)的推导。

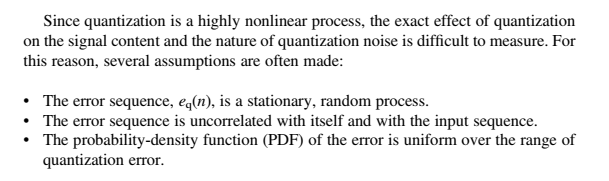

推导到上面最后一个式子的时候,这个时候我们应当学会别人在设计ADC时,将量化噪声作为白噪声假设的那些个条件。主要有三点,1)随机性;2)非相关性;3)均匀性;下面的演绎利用它的非相关性,即与TVCO(n)无关。

Figure 10. 量化噪声的三个假设

除了非相关特性外,其实还有个特点,就是它的定义,这噪声相对于信号而言是个非常小的量。那么利用这两个特性,进一步对上面的公式进行简化。如下,

不知道大家是否还记得Tvco(n)是什么吗?细心地读者可以翻翻赤脚大佬啃猪蹄:剖析VCO量化器FDC(Frequency to Digital Converter)的数学公式化中的Figure 3。代入到上述推导中。

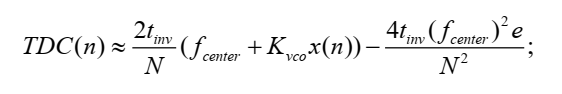

读者可能发现了,在量化噪声的那一项当中,这个NTF怎么还有输入x有关呢?不是违背了上面的三个假设嘛!遇到这种情况,一般而言,遵从地是大佬的假设,因为他们说的都对。那怎么办?直接弃之即可。

至此,我们就推导出TDC的信号传递函数STF与噪声传递函数。

======

结束语:由于近一个月来将空闲时间用来读莫言先生的《生死疲劳》和另一本专业书《自动控制原理》,因此,能够坐在电脑面前写文的时间就少了。现在抓紧时间,用了一整天的闲暇时间(除了中午健身一小时与楼下五分钟的核酸时间),简单记录下关于Time-to-Digital Converter TDC的所思所想,也算是对好奇心的一个释然吧!或许等以后做到相关项目时,希望自己更加深入地进行电路设计。

感谢大家的阅读!共勉。

Sigma-Delta ADC/DAC 学习与设计

4218

4218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?