本博客的工程源码文件下载:百度网盘 (点击蓝色“百度网盘”文字即可下载)提取码:mww7

1.工程组成

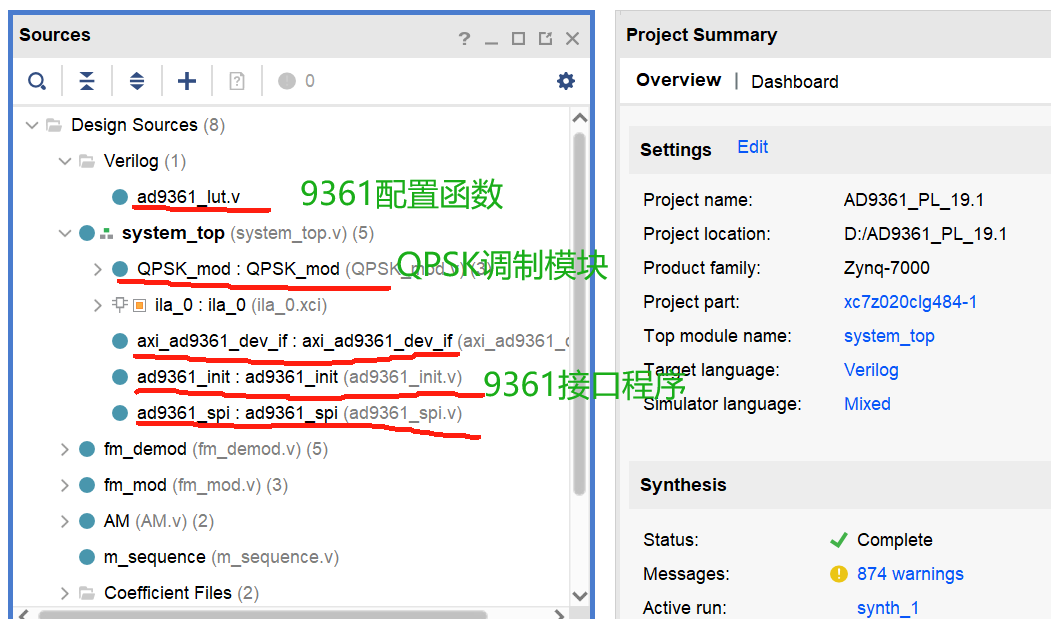

在前面博客中利用AD9361实现模拟调制FM的调制和解调,并进行了测试。本次博客利用AD9361实现QPSK正交调制,整个工程包括AD9361接口程序、配置程序和QPSK调制程序,工程结构如下图所示:

2.AD9361实现QPSK正交调制

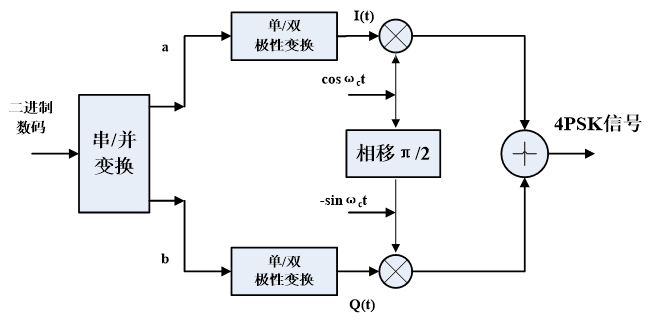

QPSK、8PSK、QAM、MSK等数字调制均采用正交调制方法实现,首先正确设置9361的寄存器,包括采样率,带宽,差分模式、射频频率等参数,利用我的转换软件将设置文件转换成ad9361_lut.v函数,实现9361的PL端纯逻辑配置。然后根据下图的调制图,分别编写串并转换模块、QPSK码元映射模块,上采样模块、升余弦模块,最后将升余弦模块IQ两路信号赋值AD9361接口函数的发送通道接口。

3.QPSK工程测试

利用ila查看升余弦函数的输出,如下图

根据ila结果可以看出9361发送通道的接口数据符合QPSK升余弦信号特征。

通过示波器、频谱仪、逻辑信号分析仪查看时域波形、频谱特征以及星座图。

频谱仪的QPSk频谱

QPSk频域

示波器的QPSK时域波形

QPSK时域

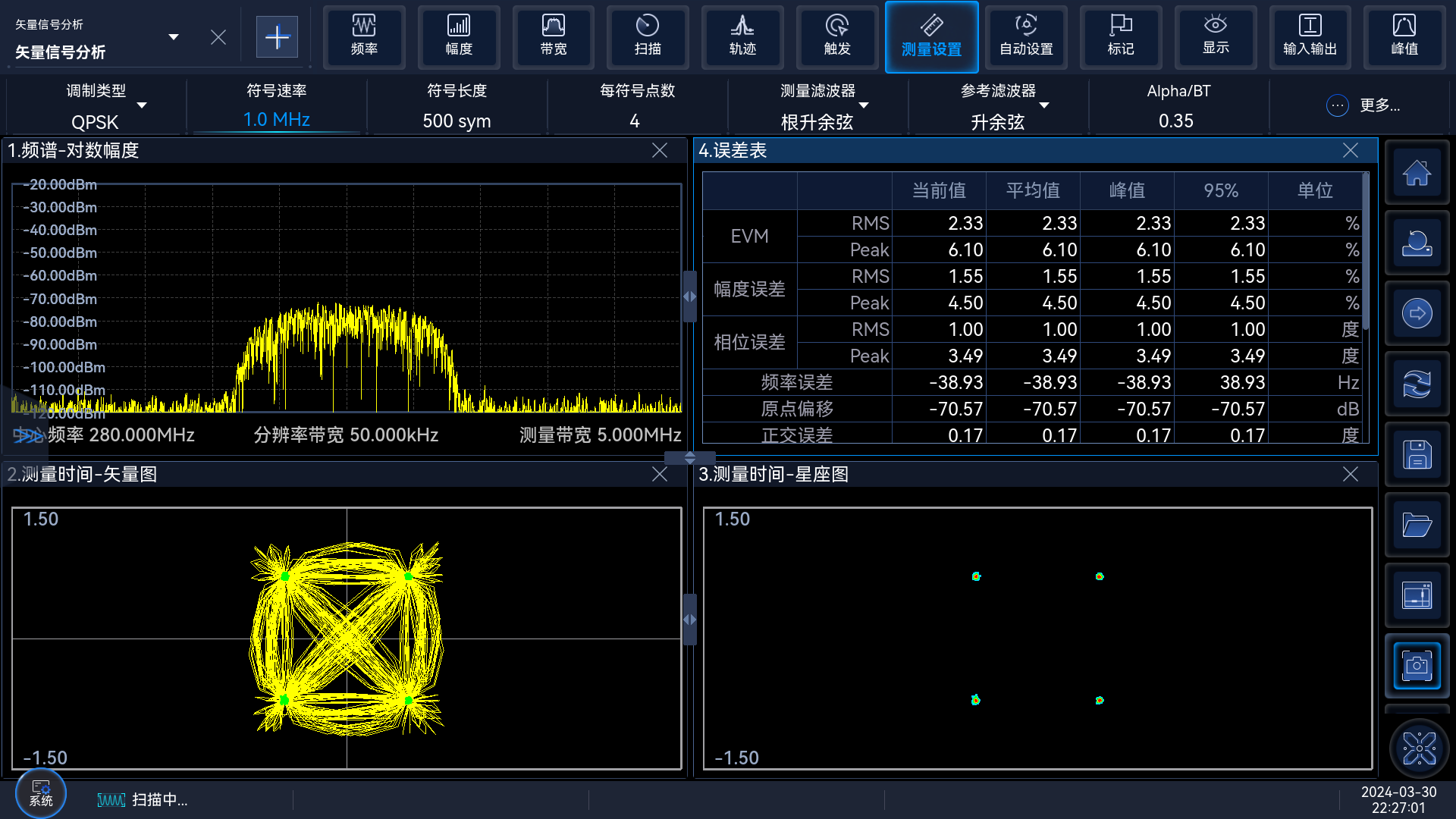

通过频谱仪和示波器可以看出符合QPSK信号特征,最后利用逻辑信号分析仪对QPSK信号查看星座图。本博客码元速率设置1MHZ。

通过分析仪可以看出,星座图符合QPSK信号特征,相位稳定,说明信号调整正确,整个工程的9361接口和配置函数工作正常。

4.总结

本博客在前面博客(如下)基础上,进一步验证了我的转换软件和AD9361接口程序正确性,同时讲解了怎么应用AD9361进行QPSK调制解调,下一步验证讲解如何利用AD9361实现数字调制信号QPSK的解调,敬请期待!!

5.参考博客文章

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(一)_初始化寄存器脚本文件生成_fpga控制ad9361-CSDN博客

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(二)_将寄存器脚本文件转换成Verilog函数_ad9361 .cfg转.v-CSDN博客

1788

1788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?