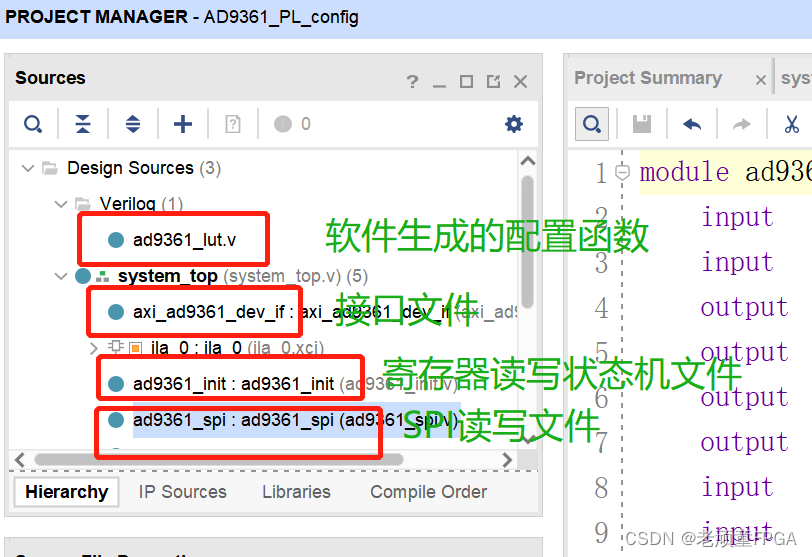

建立工程,主要文件有4个,配置函数,接口文件、寄存器读写状态机文件,SPI文件。

工程文件下载:百度网盘 提取码:mww7

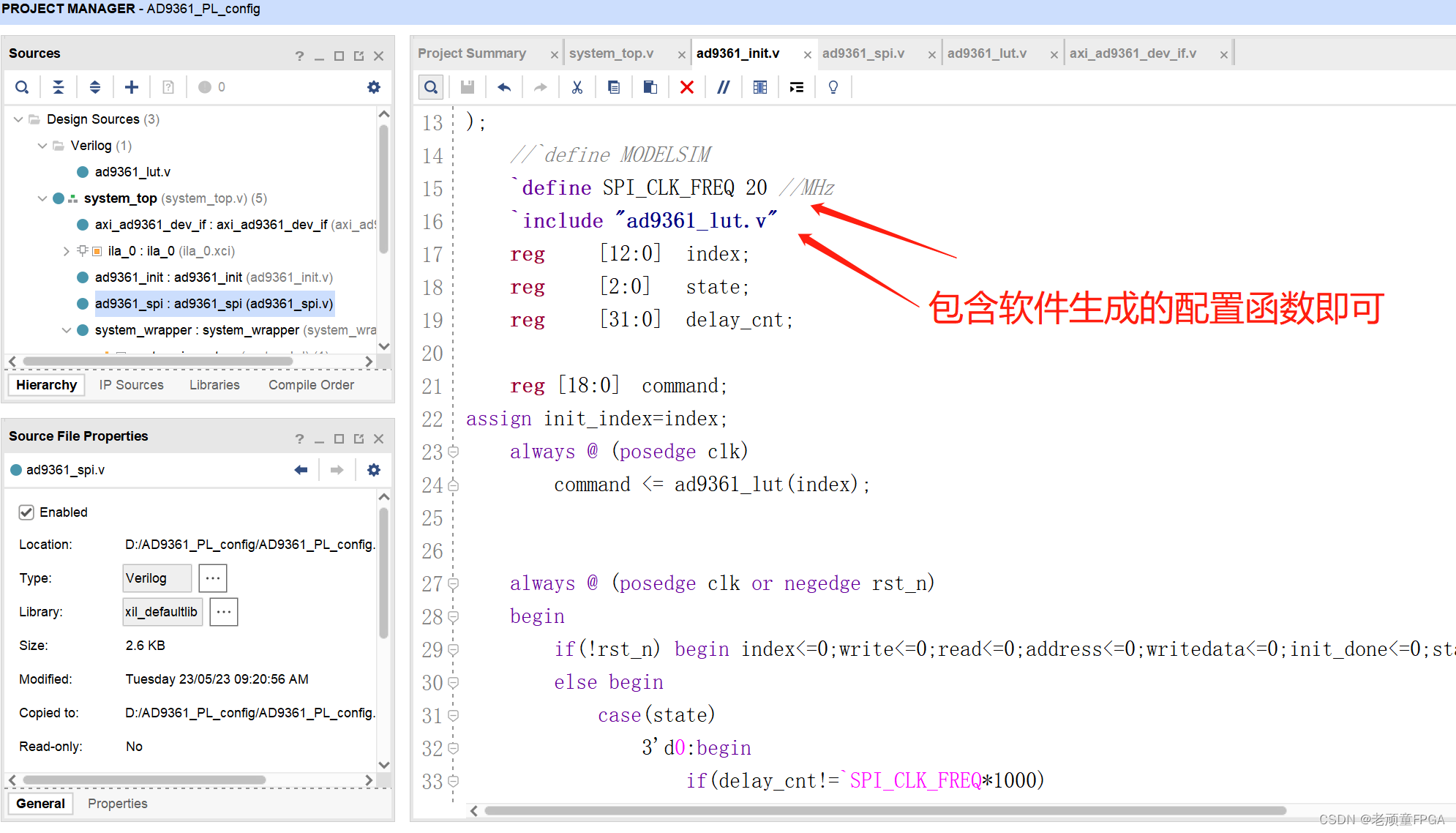

一、编写状态机文件

根据前面生成的ad9361_lut.v文件,分成写状态、读状态、延时状态,反复循环,直到最后配置完所有寄存器之后使状态机处在一个固定状态,并给出配置结束的标志信号。时钟建议20MHz和SPI读写时钟一致。

二、编写SPI读写文件

根据状态机状态,选择对相应寄存器的读写操作。根据状态机状态给出读写指示,并给出相应的寄存器地址和所需写入或读取的值。

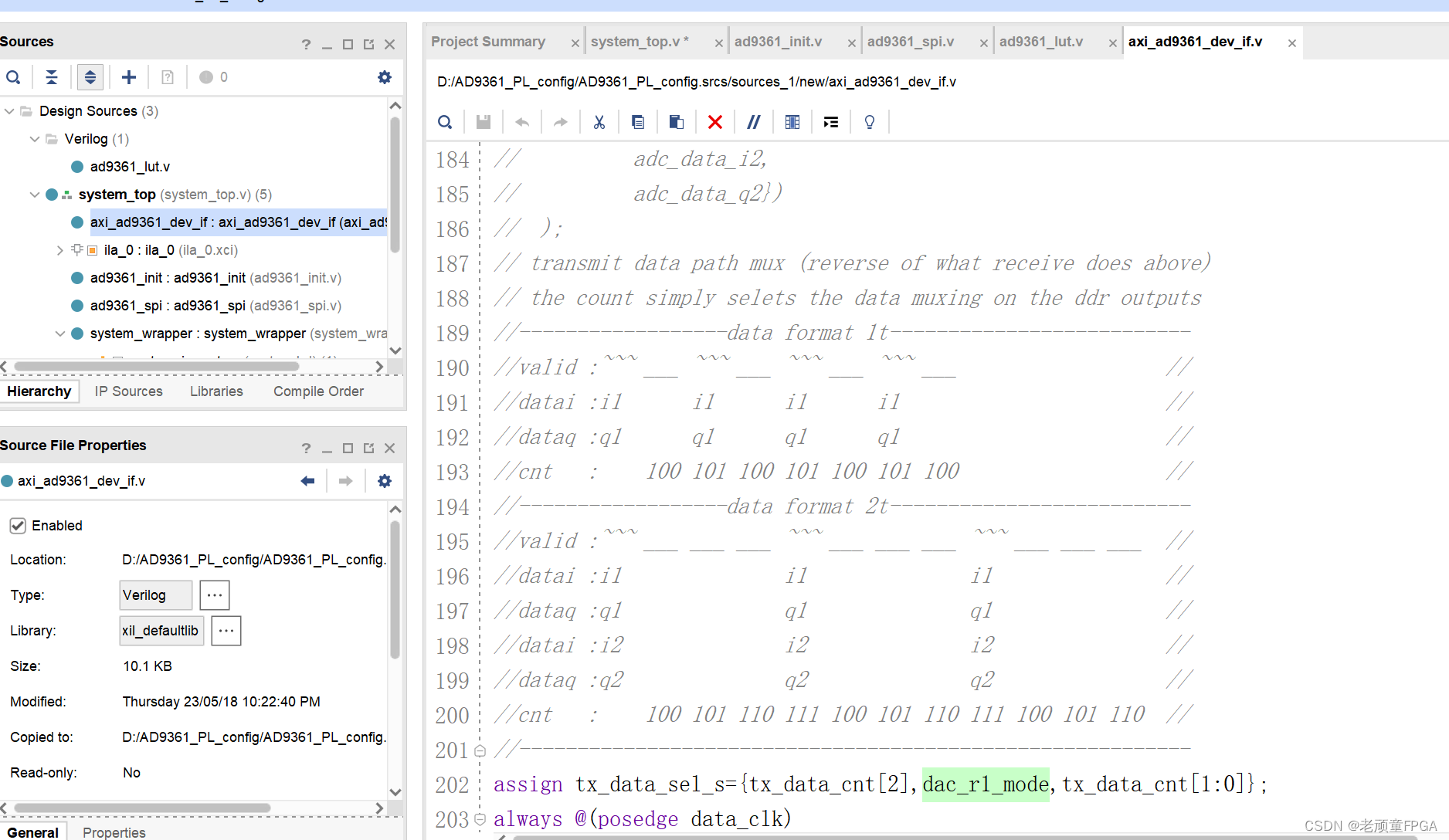

三、接口文件

基本参考ADI官方的接口文件,稍作修改,可以直接设置adc_r1_mode和dac_r1_mode配置单通道或者双通道读写。

四、测试结果

上述文件都编写结束,根据寄存器配置参数,AD9361应处在FDD工作状态,tx1和rx1单通道收发,收的频率2.4GHz,发的频率1.2GHz,工程编译完之后,加载到电路板,利用示波器测试clk_out引脚查看时钟是否配置正确,利用频谱仪测试输出信号是否为1.2GHz频率。

为了方便测试,使tx1通道输出单载波信号,直接向接口赋值1即可,如下:

示波器和频谱仪的测试结果,从测试结果看,时钟配置正确,输出信号频率1.2GHz。到这AD9361已经正常工作了。

并且通过ila查看了每个读寄存器的值,均符合要求。

748

748

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?