本博客的工程源码文件下载:百度网盘 (点击蓝色“百度网盘”文字即可下载)提取码:mww7

1.工程组成

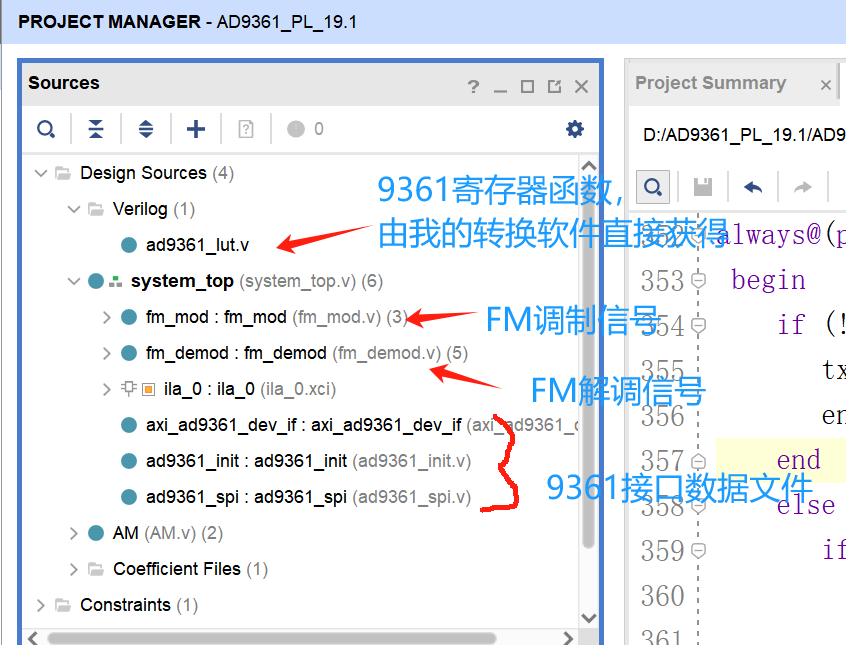

在前面博客中通过我的转换软件和AD9361接口程序,可以保证接收和发射通道是能正常工作的,这篇博客在此基础上增加FM信号的调制解调模块,进一步验证前面博客程序的正确性,同时讲解怎么具体使用AD9361进行信号的调制发射和接收解调,工程结构如下图所示:

2.FPAG+AD9361实现FM数字调制、解调

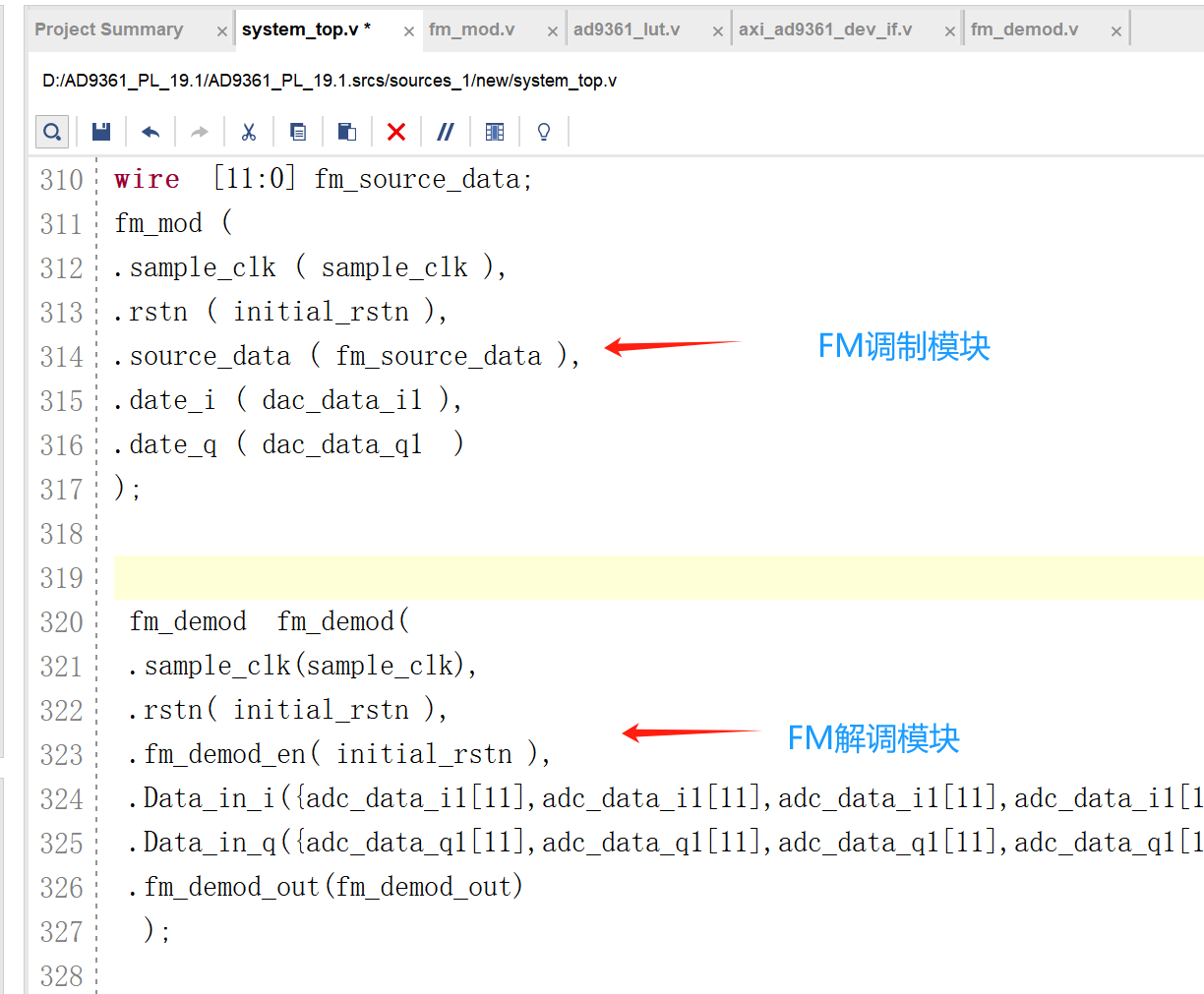

FM的数字调制和解调均采用正交调制解调方法,将9361的DATA_CLK作为采样时钟,对于FM调制,重点是设计好最大频偏,然后采用DDS方法,实现cos和sin的两路正交输出,直接赋值AD9361接口文件的dac_data_i和dac_data_q。

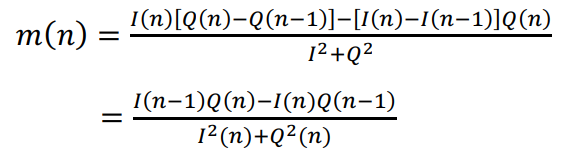

对于FM数字解调,将AD9361接收的adc_data_i和adc_data_q两路信号按照下面的数字解调公式计算,即可解调出信源信号,最后设计合适的滤波器,对解调的信源信号做一定的滤波处理。

在计算过程中注意数据位的截断取舍!

本工程中FM的调制、解调程序模块如下图:

3.FM数字调制、解调工程测试

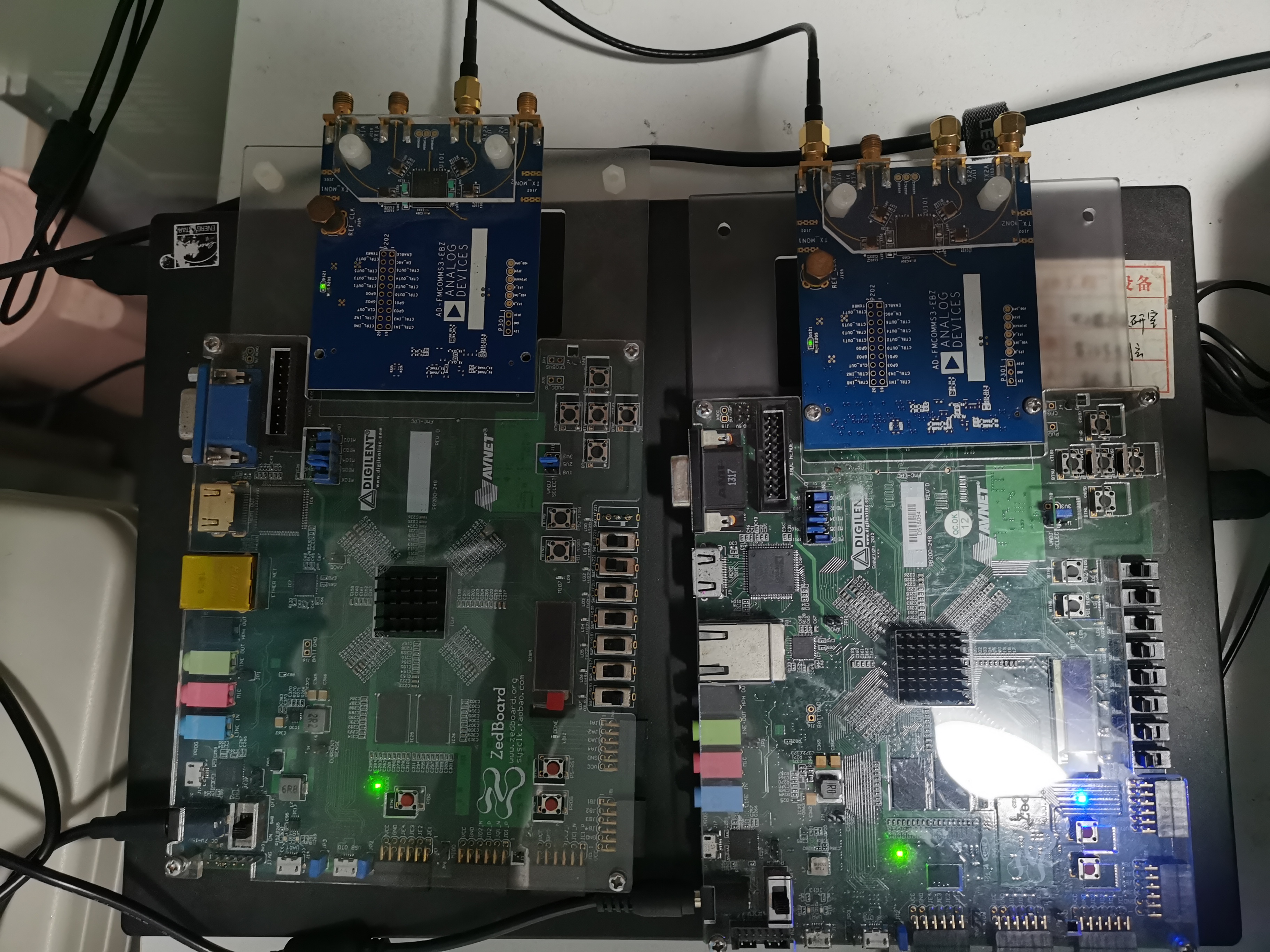

采用两个ZedBoard+AD9361_FPGA开发板,一个作为接收,一个作为发送,连接方式如下图所示:

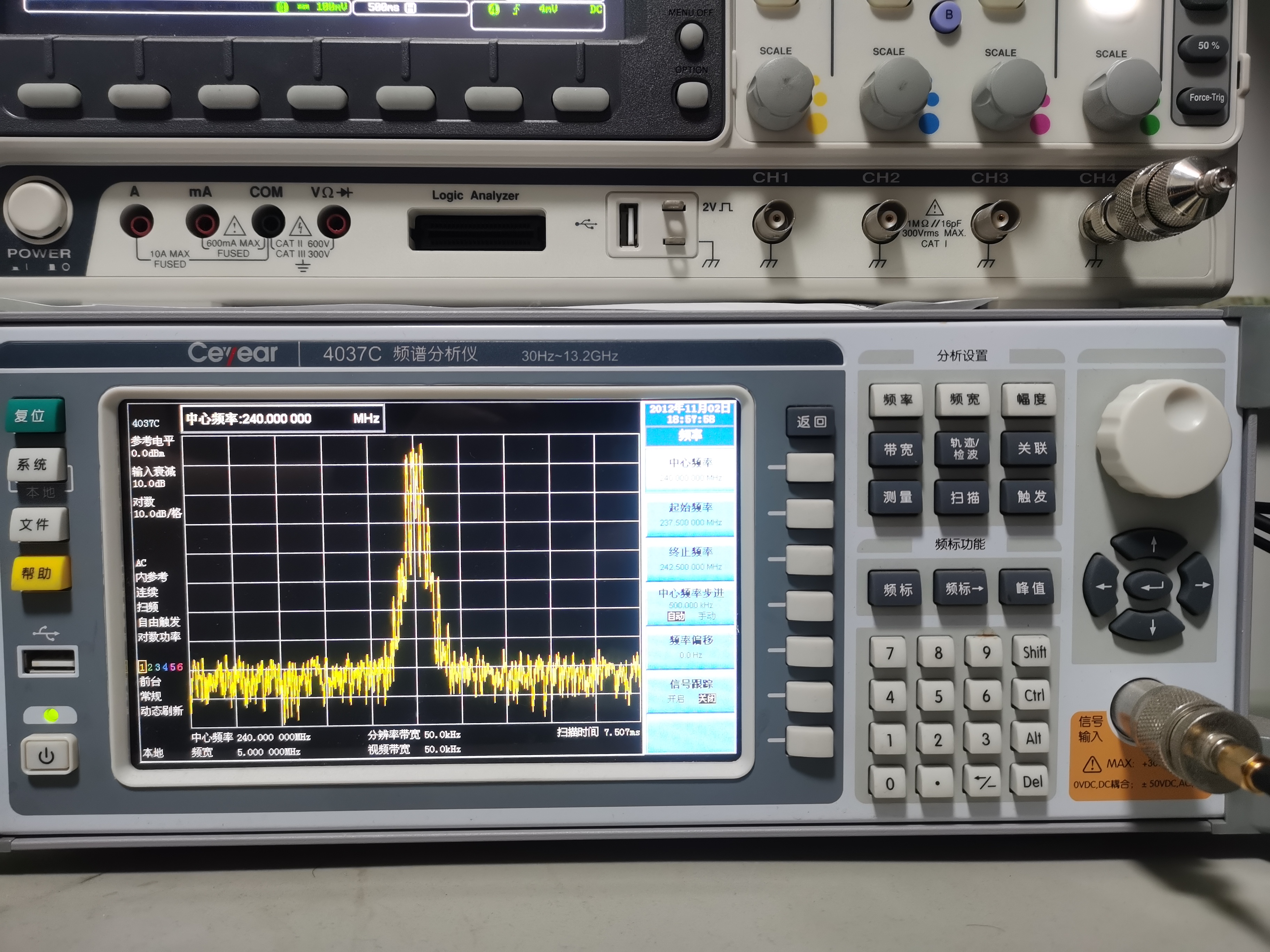

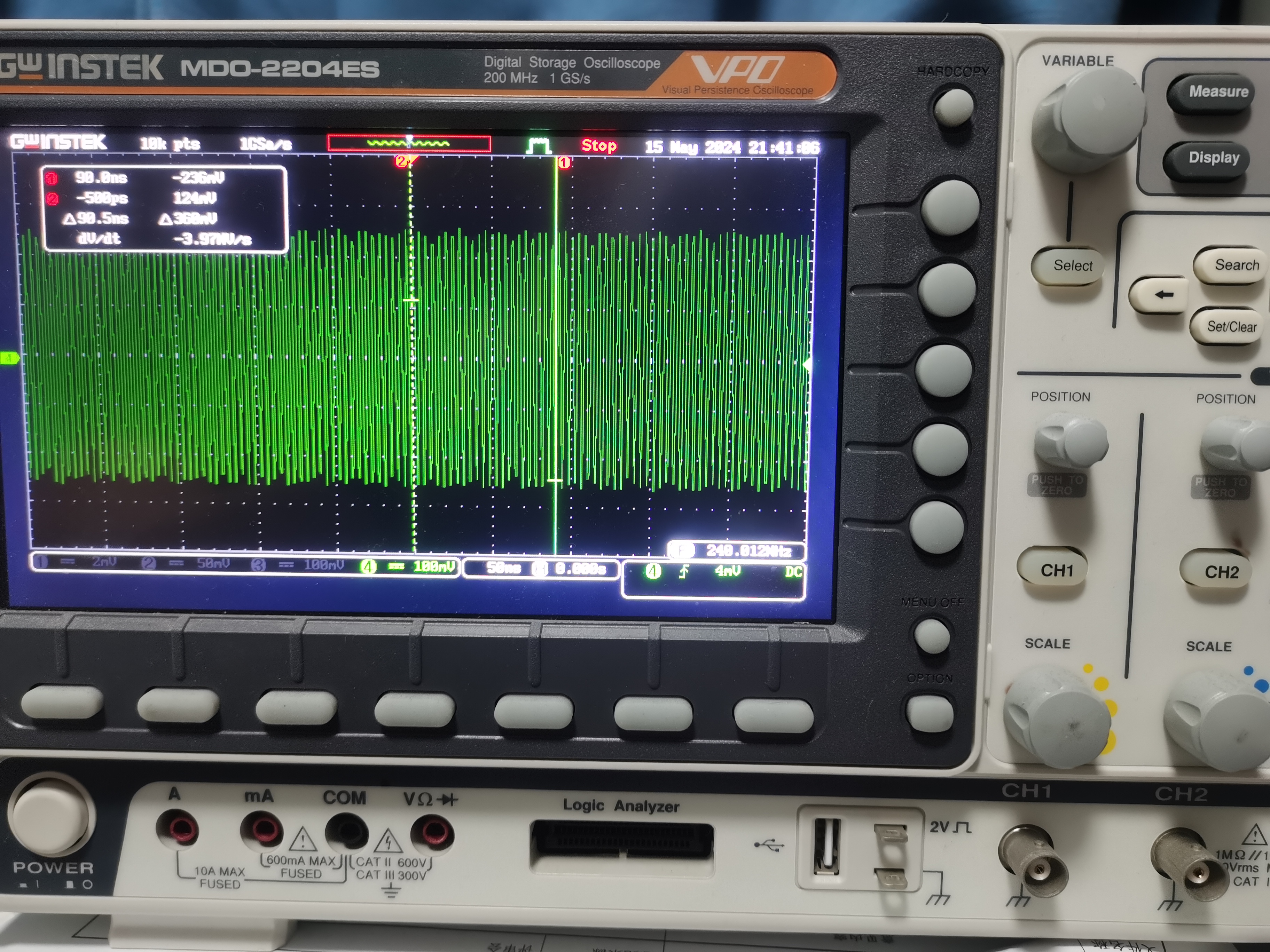

利用示波器和频谱仪查看FM辐射信号的质量好坏,如下图:

频谱仪-FM频谱

示波器-FM时域波形

从频谱仪和示波器的波形可以看出FM信号质量很好。可以证明配置的发射通道和调制模块均是正确的。

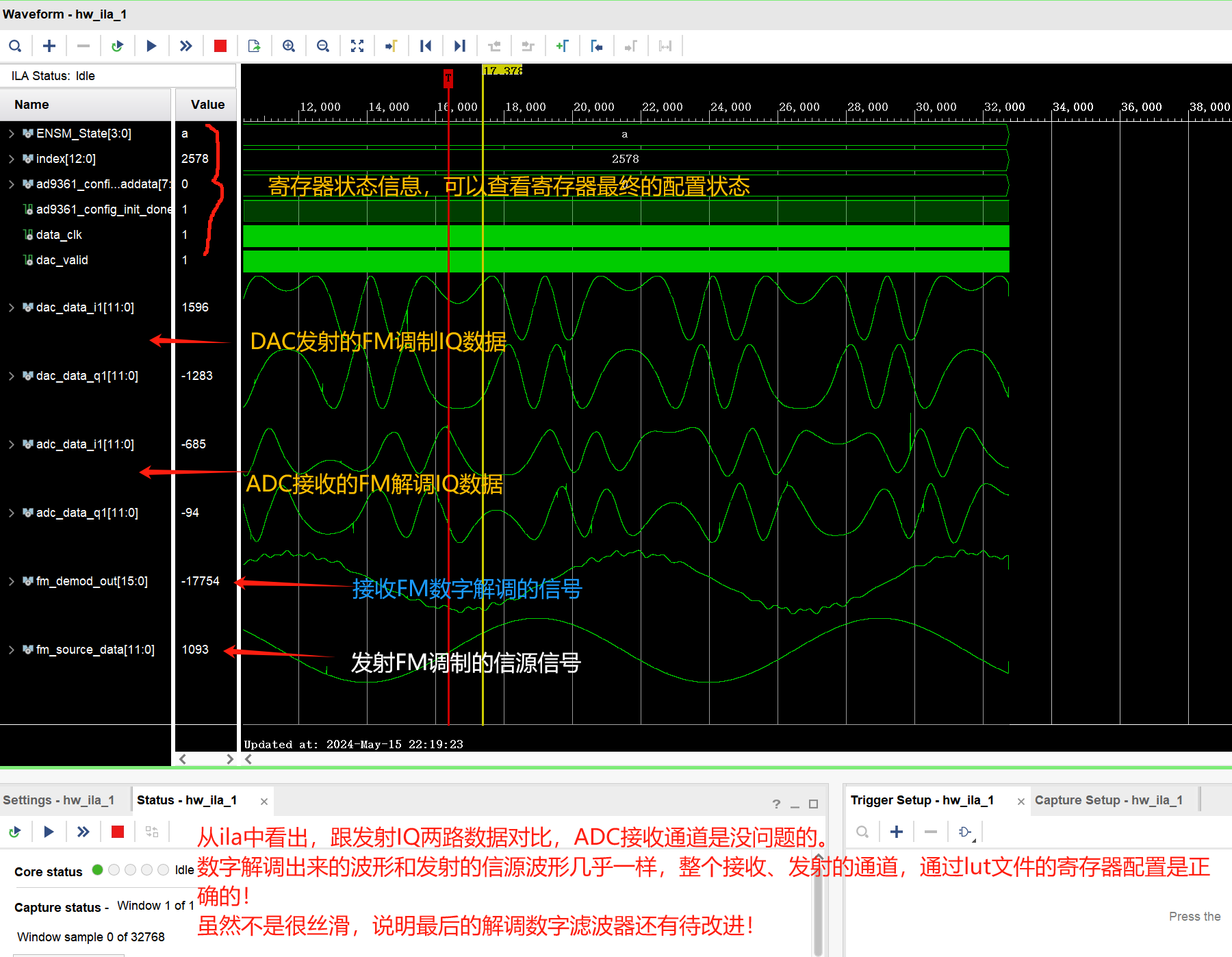

通过ila查看AD9361接收通道的adc_data_i和adc_data_q两路信号质量以及最终的解调信号,如下图:

通过ila可以对比AD9361发射通道的dac_data_i和dac_data_q两路正交调制信号和接收通道的两路信号adc_data_i和adc_data_q几乎完全一样,说明我的转换软件和接口程序是完全正确的,能够使AD9361正常工作。

从最终解调出来的波形和发射的信源波形对比,几乎一样,但不是很丝滑,说明我设计的滤波器还有待进一步改进,这种解调程度对于接收FM广播是没有问题的,音质很好。

4.总结

本博客在前面博客(如下)基础上,进一步验证了我的转换软件和AD9361接口程序正确性,同时讲解了怎么应用AD9361进行信号的调制解调,下一步验证讲解如何利用AD9361实现数字调制信号QPSK的调制解调,敬请期待!!

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(一)_初始化寄存器脚本文件生成_fpga控制ad9361-CSDN博客

ZedBoard+AD9361_FPGA的PL端纯逻辑(verilog)配置控制9361(二)_将寄存器脚本文件转换成Verilog函数_ad9361 .cfg转.v-CSDN博客

7608

7608

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?