简介

串行外设接口(SPI),它是一种高速同步串行输入和输出(I/O)端口,允许程序长度(1到16位)的串行位流以程序的比特传输速率进出设备。SPI通常用于MCU控制器与外部外设或其他控制器之间的通信。典型的应用包括通过移位寄存器、显示驱动程序和模数转换器(adc)等设备进行的外部I/O或外设扩展。

SPI的主或从操作支持多设备通信。该端口支持16级FIFO收发,以减少CPU服务开销。

特性

SPI模块的特性包括:

- SPISOMI: SPI从输出/主输入引脚

- SPISIMO: SPI从输入/主输出引脚

- SPISTE: SPI从发射使能引脚

- SPICLK: SPI串行时钟引脚

- 两种操作模式:主和从

- 波特率:125个不同的可编程速率。可采用的最大波特率受SPI引脚上使用的I/O缓冲区的最大速度限制

- 四种时钟方案(由时钟极性和时钟相位位控制)包括:

-

- 无相位延迟的下降边缘:SPICLK active-high。SPI在SPICLK信号的下降沿上传输数据,在SPICLK信号的上升沿上接收数据。

-

- 带相位延迟的下降边缘:SPICLK active-high。SPI在SPICLK信号的下降沿前半个周期发送数据,并在SPICLK信号的下降沿上接收数据。

-

- 无相位延迟的上升边缘:SPICLKinactive-low。SPI在SPICLK信号的上升沿上传输数据,在SPICLK信号的下降沿上接收数据。

-

- 带相位延迟的上升边缘:SPICLKinactive-low。SPI在SPICLK信号的上升沿前半个周期发送数据,并在SPICLK信号的上升沿上接收数据。

- 收发同时操作(可在软件中关闭发送功能)

如果不使用SPI模块,所有四个引脚都可以用作GPIO。

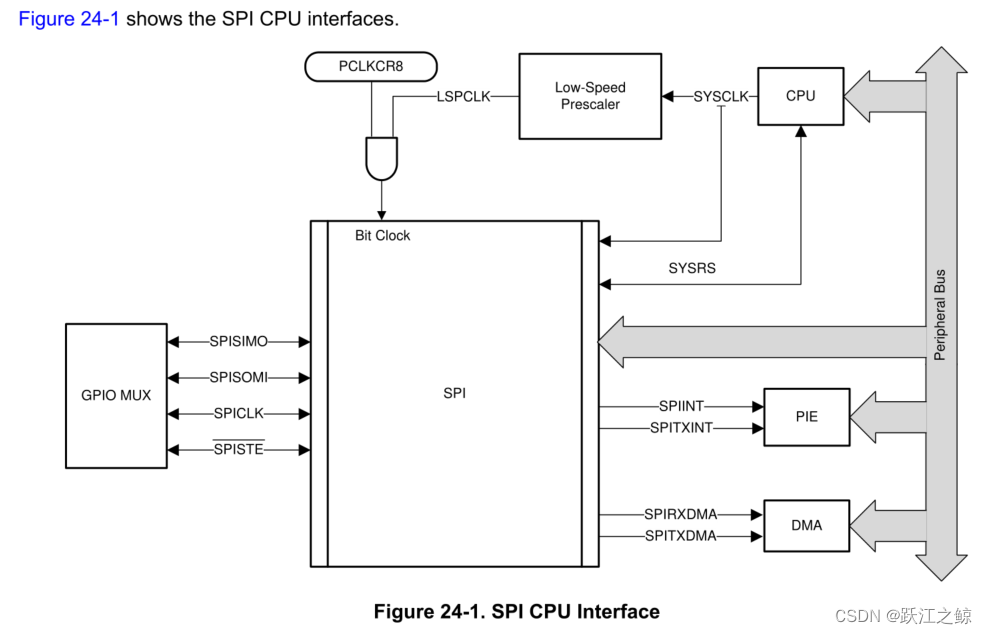

框图

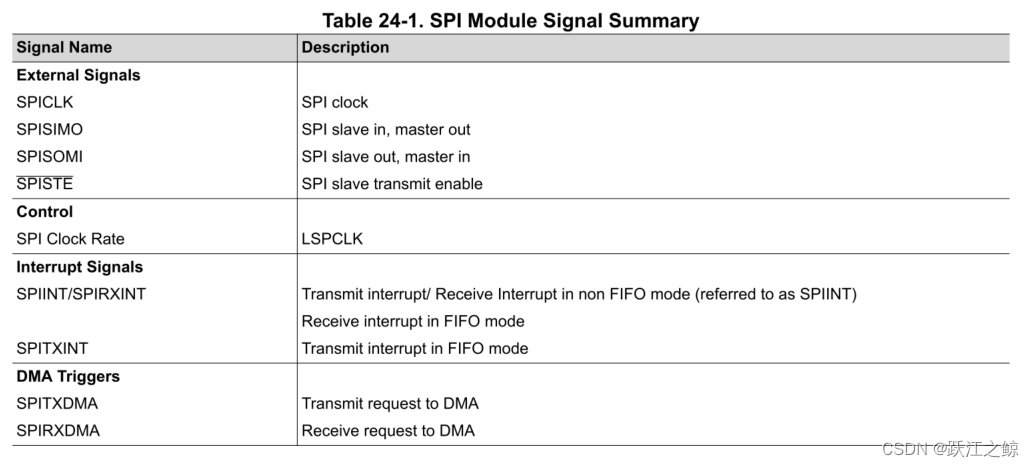

表24-1对SPI模块信号进行分类并提供摘要

当SPI处于从模式时,SPISTE信号提供了gate任何虚假时钟和数据脉冲的能力。SPISTE上的HIGH逻辑信号将不允许从机接收数据。这可以防止SPI从站失去与主站的同步。不建议将SPISTE始终绑定到活动状态。

如果SPI从端确实失去了与主端同步,那么切换SPISWRESET将重置内部位计数器以及模块中的各种状态标志。通过重置位计数器,SPI将下一个时钟转换解释为新传输的第一个位。

SPI Operation

对操作模式、中断、数据格式、时钟源和初始化的解释。给出了数据传输的典型时序图。

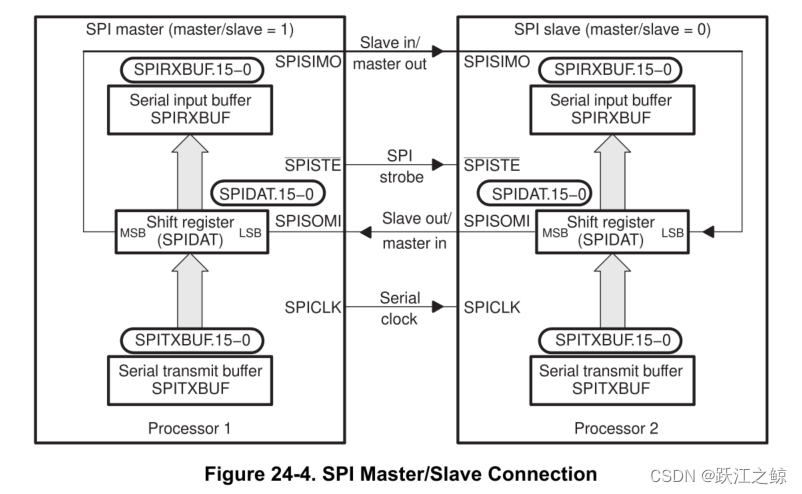

图24-4显示了用于两个控制器之间通信的SPI的典型连接:一个主控制器和一个从控制器。

主机通过发送spickk信号来传输数据。对于从端和主端,数据从SPICLK一端的移位寄存器移出,锁存到另一端SPICLK时钟边缘的移位寄存器中。如果CLK_PHASE位高,则在spickk转换前半个周期传输和接收数据。

结果,两个控制器同时发送和接收数据。应用软件判断数据是有意义数据还是虚拟数据。有三种可能的数据传输方法:

-

主发送数据;Slave发送虚拟数据。

-

Master发送数据;Slave发送数据。

-

Master发送虚拟数据;Slave发送数据。

master可以在任何时候启动数据传输,因为它控制着SPICLK信号。然而,软件决定了主机如何检测从机何时准备好数据。

SPI可以在主模式或从模式下工作。MASTER_SLAVE位选择工作模式和spiclk信号的来源。

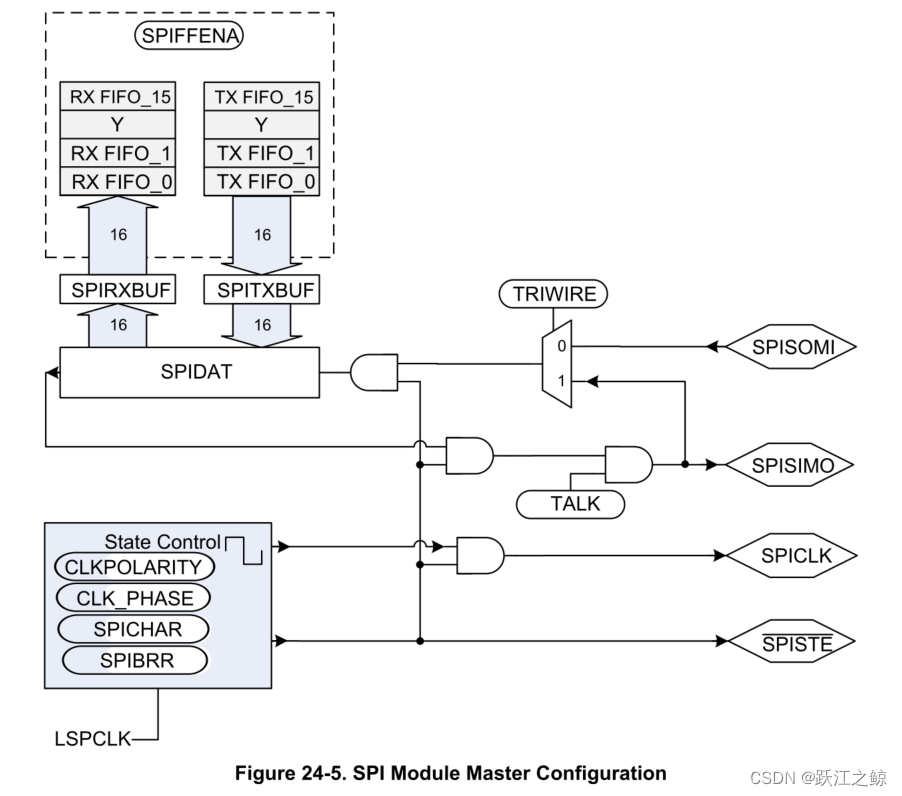

主模式

在主模式(MASTER_SLAVE = 1)下,SPI为整个串行通信网络提供在SPICLK引脚上的串行时钟。数据在SPISIMO引脚上输出,并从SPISIMO引脚锁存。

SPIBRR寄存器决定了网络的发送和接收比特传输速率。SPIBRR可以选择125种不同的数据传输速率。

写入SPIDAT或SPITXBUF的数据首先在SPISIMO引脚上启动数据传输,MSB(最高有效位)。同时,接收到的数据通过SPISOMI引脚转移到LSB(最低有效位)。

图24-5是SPI在主模式下的框图。它显示了SPI主模式中可用的基本控制块。

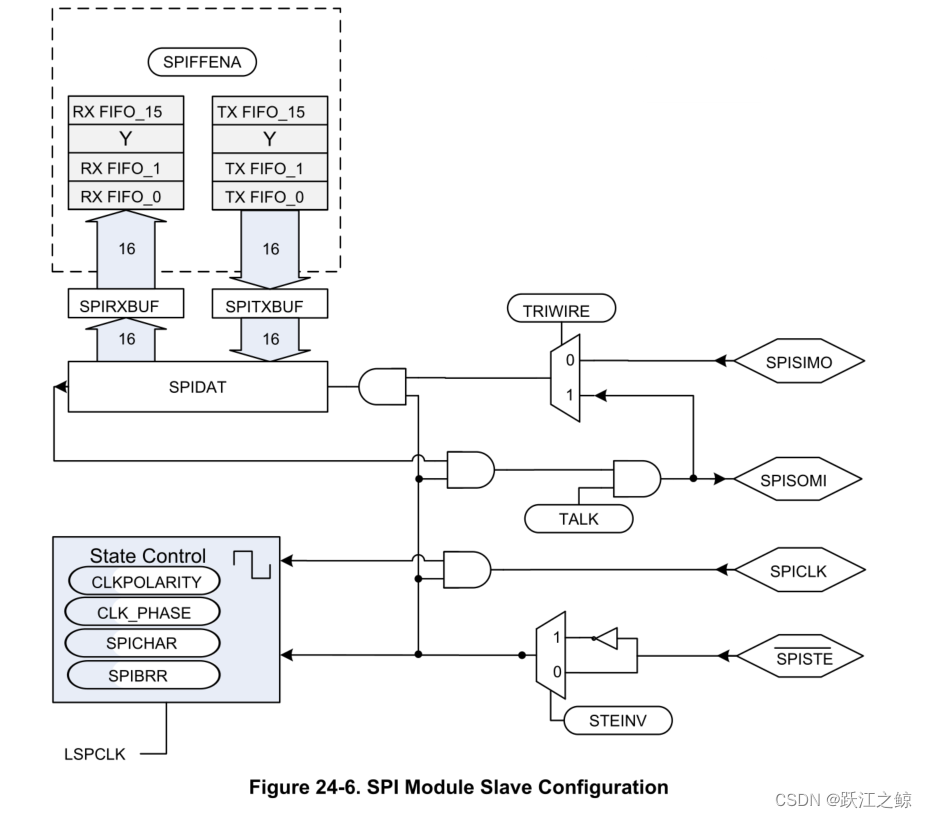

从模式

在从模式(MASTER_SLAVE = 0)下,数据在SPISOMI引脚上移出,在SPISIMO引脚上移入。SPICLK引脚被用作串行移位时钟的输入,该时钟由外部网络主机提供。

传输速率由这个时钟定义。SPICLK输入频率不能大于LSPCLK频率除以4。

图24-6是SPI从模式的框图。它显示了SPI从模式中可用的基本控制块。

1802

1802

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?