Verilog HDL中如何控制模块的调用与否(实用)

语言 :Verilg HDL

EDA工具:ISE、Vivado、Quartus II

- 关键词: 调用,Verilog HDL,ifdef 和 endif ,generate语句

一、引言

在FPGA开发调试中,经常需要添加debug核,ila或者vio,在调试结束或者功能测试完成之后,需要将之前添加的debug核去掉,以使得工程轻量化,那么这时我们最常用的方法是直接将ila模块注释掉,这种方法简单快速,但是影响代码美观,在debug模块比较多的时候,也比较繁琐。本文,在结合平时做项目中的经验,对Verilog HDL中控制模块调用与否的方式 作了一个总结,望能对各位实操应用中有所帮助。

二、模块调用与否的几种方法

1. 注释

常用方法是直接注释,如下,用 “//”

// ila_smooth ila_smooth (

// .clk(clk), // input wire clk

// .probe0(freq_in), // input wire [16:0] probe0

// .probe1(freqmax1), // input wire [15:0] probe1

// .probe2(freqmax2), // input wire [15:0] probe2

// .probe3(freqmax3), // input wire [15:0] probe3

// .probe4(freqmax4))// input wire [15:0] probe4

或者 “/* */”

/*

ila_smooth ila_smooth (

.clk(clk), // input wire clk

.probe0(freq_in), // input wire [16:0] probe0

.probe1(freqmax1), // input wire [15:0] probe1

.probe2(freqmax2), // input wire [15:0] probe2

.probe3(freqmax3), // input wire [15:0] probe3

.probe4(freqmax4))// input wire [15:0] probe4

*/

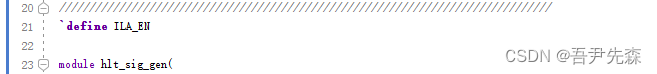

2. 使用预处理指令`ifdef

在Verilog中,ifdef 和 endif 是条件编译指令,它们允许在编译时根据条件包含或排除代码块。这些指令通常用于创建可配置的设计,使得同一段代码可以适应不同的硬件平台或配置要求。

ifdef 和 endif 的基本用法:

ifdef:如果定义了指定的宏(macro),则包含 ifdef 和 endif 之间的代码块。

endif:标记 ifdef 条件编译块的结束

因此,我们只需要将 模块置于 ifdef 和 endif 之间即可,然后通过是否宏定义 ifdef 来决定是否调用该模块,如下所示,

`define ILA_EN

//`define ILA_EN

`ifdef ILA_EN

ila_smooth ila_smooth (

.clk(clk), // input wire clk

.probe0(freq_in), // input wire [16:0] probe0

.probe1(freqmax1), // input wire [15:0] probe1

.probe2(freqmax2), // input wire [15:0] probe2

.probe3(freqmax3), // input wire [15:0] probe3

.probe4(freqmax4))// input wire [15:0] probe4

`endif

注意`define ILA_HSG_EN 语句可以置于.v文件的任何位置,一般放到文件的最开始处,不调用 ifdef 和 endif 之间的模块时,将宏定义注释掉就行,宏定义中可以 有多个模块

3. 使用generate语句

在Verilog中,generate 和 endgenerate 是用于生成参数化结构的关键字,它们允许你根据一个参数重复生成一段代码,或者根据条件生成代码块。这种结构在设计中非常有用,尤其是当你需要创建多个相同结构的实例时,可以大大减少代码的冗余。

使用方法如下,当参数USER_TX_ILA 输入为1时候,模块起效,否则无效,

generate

if( USER_ILA == 1 )

ila_smooth ila_smooth (

.clk(clk), // input wire clk

.probe0(freq_in), // input wire [16:0] probe0

.probe1(freqmax1), // input wire [15:0] probe1

.probe2(freqmax2), // input wire [15:0] probe2

.probe3(freqmax3), // input wire [15:0] probe3

.probe4(freqmax4))// input wire [15:0] probe4

endgenerate

USER_TX_ILA可以用作参数输入,如下所示。

module top #(

parameter USER_ILA = 0

)(

三、结尾

本文主要介绍了在Verilog HDL编程中,如何根据不同情况控制模块是否被调用的方法。文章的核心内容可以概括为以下几点:

注释方法: 通过在代码中使用注释符号//或/* */来临时禁用模块,这种方法简单快捷,但会使得代码看起来杂乱,尤其是在需要注释掉多个模块时。

条件编译指令: 使用ifdef和endif预处理指令来根据是否定义了特定的宏来决定是否编译某段代码。通过定义或注释掉宏,可以灵活地控制模块的调用,使得代码更加整洁。

generate语句: 利用generate和endgenerate关键字,根据参数或条件来生成代码块。这种方法适用于需要根据不同参数多次生成相同结构模块的情况,可以减少代码重复,提高代码的可维护性。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?