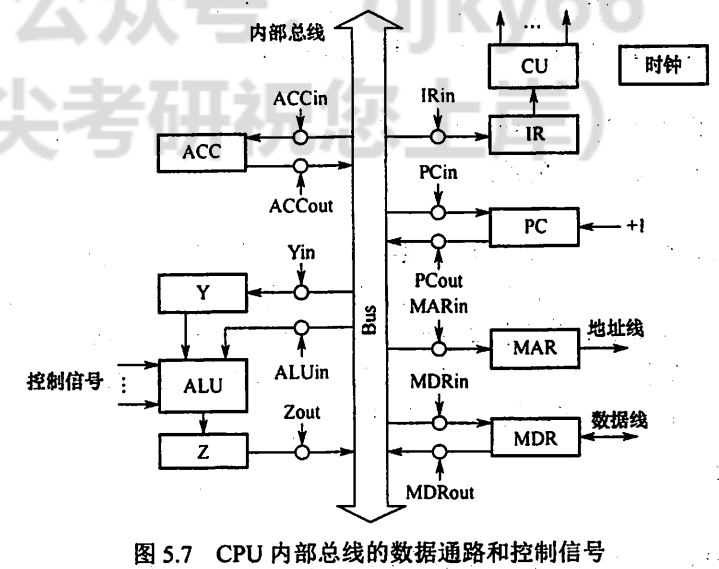

- 数据在功能部件之间传送的路径称为数据通路,包括数据通路上流经的部件:ALU、通用寄存器、状态寄存器、异常和中断处理逻辑等。

- 数据通路受控制部件控制,控制部件根据每条指令的功能来生成对应的数据通路的控制信号。

- 数据通路由控制部件控制,控制部件依据指令的功能生成对数据通路的控制信号,因此,数据通路不包括控制部件。

1.功能

实现CPU内部的运算器与寄存器以及寄存器之间的数据交换。

2.基本结构

2.1 分类

2.1 CPU内部单总线方式

2.1.1 说明

将所有寄存器的输入端与输出端都连接到同一条公共通路上。

2.1.2 优缺点

优点

结构简单。

缺点

数据传输存在较多的冲突现象,性能较低。

总线中的一个时钟周期内只允许传输一个数据,指令执行效率较低。

2.2 CPU内部多总线方式

2.2.1 说明

将所有寄存器的输入端与输出端都连接到多条公共通路上。

2.2.2 优缺点

优点

能够同时再多个总线上传输不同的数据,提高了效率。

2.3 专用数据通路方式

2.3.1 说明

根据指令执行过程中的数据和地址的流动方向安排连接线路,避免使用共享的总线。

2.3.2 优缺点

优点

性能较高。

缺点

硬件量大。

内部总线是指同一部件,如:CPU内部连接各寄存器及运算部件之间的总线。

系统总线是指同一台计算机系统的各部件,如:CPU、内存和各类I/O接口间相互连接的总线。

采用CPU内部总线的数据通路的特点:结构简单,实现容易,性能较低,存在较多的数据冲突现象;不采用CPU内部总线的数据通路的特点:结构复杂,数据量大,不易实现,性能较高,基本不存在数据冲突的现象。

3.栗子🌰

3.1 寄存器之间的数据传送

3.1.1 说明

寄存器之间的数据传送可通过CPU内部总线完成。

3.1.2 栗子🌰

3.2 主存与CPU之间的数据传送

3.2.1 说明

主存与CPU之间的数据传送同样也要借助CPU内部总线完成。

3.2.2 栗子🌰

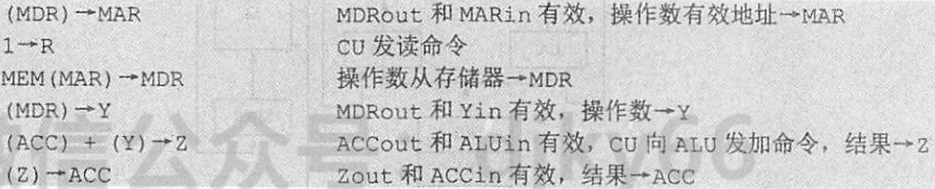

3.3 执行算数或逻辑运算

3.1.1 说明

- 执行算数或逻辑运算操作时,由于ALU本身无内部存储功能的组合电路,因此,要执行加法运算,两个操作数必须同时送入输入端。而暂存器便是起这样的作用。

- 进行运算操作时,先将一个操作数通过CPU内部总线送入(输入的)暂存器保存,然后再将另一个操作数直接送入ALU的右输入端。这样,两个操作数全部送入了ALU,然后ALU随后进行运算并将结果存入(输出的)暂存器中。

3.1.2 栗子🌰

3269

3269

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?