专业术语概念

SDK

概念:软件开发工具包(SDK,全称:Software Development Kit)

SDK是Software Development Kit的缩写,中文意思是“软件开发工具包”。这是一个覆盖面相当广泛的名词,可以这么说:辅助开发某一类软件的相关文档、范例和工具的集合都可以叫做“SDK”。SDK是一系列文件的组合,它为软件的开发提供一个平台(它为软件开发使用各种API提供便利)

API

概念:API(Application Programming Interface,应用程序编程接口)

一般是指一些预先定义的函数,目的是提供应用程序与开发人员基于某软件或硬件得以访问一组例程的能力,而又无需访问源码,或理解内部工作机制的细节。

参考链接:https://blog.csdn.net/ITBigGod/article/details/86703336

GLIBC

glibc是GNU发布的libc库,即c运行库。glibc是linux系统中最底层的api,几乎其它任何运行库都会依赖于glibc。glibc是一种按照LGPL许可协议发布的,自由的,公开源代码的,方便从网络下载的C的编译程序。

GCC

(GNU Compiler Collection,GNU编译器套件)是由GNU开发的编程语言译器。GNU编译器套件包括C、C++、 Objective-C、 Fortran、Java、Ada和Go语言前端,也包括了这些语言的库(如libstdc++,libgcj等。)虽然我们称GCC是C语言的编译器,但使用gcc由C语言源代码文件生成可执行文件的过程不仅仅是编译的过程,而是要经历四个相互关联的步骤∶预处理(也称预编译,Preprocessing)[生成.i]、编译(Compilation)[生成汇编代码.s]、汇编(Assembly)[生成目标文件.o]和链接(Linking)。

命令gcc首先调用cpp进行预处理,在预处理过程中,对源代码文件中的文件包含(include)、预编译语句(如宏定义define等)进行分析。接着调用cc1进行编译,这个阶段根据输入文件生成以.i为后缀的目标文件。汇编过程是针对汇编语言的步骤,调用as进行工作,一般来讲,.S为后缀的汇编语言源代码文件和汇编、.s为后缀的汇编语言文件经过预编译和汇编之后都生成以.o为后缀的目标文件。当所有的目标文件都生成之后,gcc就调用ld来完成最后的关键性工作,这个阶段就是连接。在连接阶段,所有的目标文件被安排在可执行程序中的恰当的位置,同时,该程序所调用到的库函数也从各自所在的档案库中连到合适的地方.

可用如下命令检查gcc版本。

rpm -q gcc

gcc参数详解:https://www.runoob.com/w3cnote/gcc-parameter-detail.html

gdb

gdb是GNU开源组织发布的一个强大的Linux下的程序调试工具。

https://blog.csdn.net/weixin_37921201/article/details/120117096

core文件

core文件是死机之后为了还原现场进行分析而生成的,使用gdb工具可以翻译对于异常时的函数行号。

CPIO

cpio是用来建立、还原备份档的工具程序,它可以加入、解开cpio或tar备份档内的文件。

https://blog.csdn.net/wh_19910525/article/details/8112538?spm=1001.2101.3001.6650.2&utm_medium=distribute.pc_relevant.none-task-blog-2~default~CTRLIST~Rate-2-8112538-blog-116961555.pc_relevant_antiscanv2&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2~default~CTRLIST~Rate-2-8112538-blog-116961555.pc_relevant_antiscanv2&utm_relevant_index=5

http://www.360doc.com/content/21/1118/09/3046928_1004674088.shtml

GPIO

(General-purpose input/output)通用型输入输出的简称。

通俗地说,就是芯片上的一些引脚(当然并不是芯片上所有的引脚都叫GPIO),可以通过编程控制它们输出高低电平或者通过它们读入引脚的状态-是高电平或是低电平。

GPIO口一是个比较重要的概念,用户可以通过GPIO口和硬件进行数据交互(如UART),控制硬件工作(如LED、蜂鸣器等),读取硬件的工作状态信号(如中断信号)等。GPIO口的使用非常广泛。

https://blog.csdn.net/doitsjz/article/details/70193790

LPC总线

(Low pin count Bus),是在IBM PC兼容机中用于把低带宽设备和“老旧”连接到CPU上。那些常见低速设备有:BIOS,串口,并口,PS/2的键盘和鼠标,软盘控制器,比较新的设备有可信平台模块。LPC总线通常和主板上的南桥物理相连,南桥在IBM PC AT平台上通常连接了一系列的“老旧”设备,例如两个可编程中断控制器, 可编程计时器和两个 ISA DMA 控制器。

https://wenku.baidu.com/view/76556299dfccda38376baf1ffc4ffe473268fd3e.html

I2C总线

I2C(Inter-Integrated Circuit)总线是由Philips公司在上世纪80年代开发的一种简单、双向二线制同步串行总线。它只需要两根线即可在连接于总线上的器件之间传送信息。

I2C既是一种总线,也是一种通信协议。总线和通信协议之间的关系类似于硬件和基于此硬件的软件,同一种总线上可以跑多种协议,如在RS485总线上可以跑莫迪康的MODBUS,松下的MEWTOCOL,西门子的profibus/DP等协议;同样地,同一种协议也可以跑在不同的总线上,如上述协议还可以跑在以太网上。一言以蔽之,总线涉及的是物理层的硬件,而协议可以认为是在物理层上传递信息的约定或规则。

或者也可以这么说。在嵌入式开发中,通信协议可分为两层:物理层和协议层。物理层是数据在物理媒介传输的保障;协议层主要规定通信逻辑,如同一收发双方的数据打包、解包标准。 打个比方,物理层相当于现实中的公路,而协议层则是交通规则,汽车可以在路上行驶,但是需要交通规则对行驶规则进行约束,不然将出现危险,也就是数据传输紊乱、丢包。

原文链接:https://blog.csdn.net/ctyqy2015301200079/article/details/83830326

SPI总线

(Serial Peripheral interface)串行外围设备接口,是一种高速的,全双工,同步的通信总线。

SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

UART

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter,通常称作UART) 是一种串行异步收发协议,应用十分广泛。UART工作原理是将数据的二进制位一位一位的进行传输。在UART通讯协议中信号线上的状态位高电平代表’1’低电平代表’0’。当然两个设备使用UART串口通讯时,必须先约定好传输速率和一些数据位。

AMBA总线

AMBA是由ARM公司研发推出的一种高级微控制器总线架构(Advanced Microcontroller Bus Architecture)。其中AMBA包含了四种不同的总线标准,分别是:

AHB

ASB

APB

AXI

https://blog.csdn.net/little_ox/article/details/118399117

https://zhuanlan.zhihu.com/p/155629044

JTAG

Joint Test Action Group;联合测试工作组

JTAG是一种IEEE标准用来解决板级问题,开发于上个世纪80年代。用于芯片内部测试,今天JTAG被用来烧录、debug、探查端口。当然,最原始的使用是边界测试。

https://www.cnblogs.com/kingstacker/p/7454814.html

RTC

实时时钟的缩写是RTC(Real_Time Clock)。RTC 是集成电路,通常称为时钟芯片。

实时时钟芯片是日常生活中应用最为广泛的消费类电子产品之一。它为人们提供精确的实时时间,或者为电子系统提供精确的时间基准,目前实时时钟芯片大多采用精度较高的晶体振荡器作为时钟源。

https://wenku.baidu.com/view/6a00d5487b3e0912a21614791711cc7931b77804.html

https://blog.csdn.net/God__Rain/article/details/113664728

https://www.jianshu.com/p/724a80adb7a5

DS1337时钟芯片手册:

https://www.icspec.com/specification/specification_detail/21c5508c-0239-11eb-8577-00163e14a913

内存SPD

SPD是内存模组上面的一个可擦写的eeprom,里面记录了该内存的许多重要信息,诸如内存的芯片及模组厂商、工作频率、工作电压、速度、容量、电压与行、列地址带宽等参数。SPD信息一般都是在出厂前,由内存模组制造商根据内存芯片的实际性能写入到eeprom芯片中。

GIC

Generic Interrupt Controller。是ARM公司提供的一个通用的中断控制器。

https://blog.csdn.net/yhb1047818384/article/details/86708769

TLB

Translation Lookaside Buffer页表缓存

TLB是一个内存管理单元用于改进虚拟地址到物理地址转换速度的缓存.

TLB是位于内存中的页表的cache,如果没有TLB,则每次取数据都需要两次访问内存,即查页表获得物理地址和取数据.

https://blog.csdn.net/jeiwt/article/details/5911358?utm_medium=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-1.control&depth_1-utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-1.control

页表一般都很大,并且存放在内存中,所以处理器引入MMU后,读取指令、数据需要访问两次内存:首先通过查询页表得到物理地址,然后访问该物理地址读取指令、数据。为了减少因为MMU导致的处理器性能下降,引入了TLB,TLB是Translation Lookaside Buffer的简称,可翻译为“地址转换后援缓冲器”,也可简称为“快表”。简单地说,TLB就是页表的Cache,其中存储了当前最可能被访问到的页表项,其内容是部分页表项的一个副本。只有在TLB无法完成地址翻译任务时,才会到内存中查询页表,这样就减少了页表查询导致的处理器性能下降。

来自 https://www.cnblogs.com/alantu2018/p/9000777.html

快表,直译为旁路快表缓冲,也可以理解为页表缓冲,地址变换高速缓存。

由于页表存放在主存中,因此程序每次访存至少需要两次:一次访存获取物理地址,第二次访存才获得数据。提高访存性能的关键在于依靠页表的访问局部性。当一个转换的虚拟页号被使用时,它可能在不久的将来再次被使用到,。

TLB是一种高速缓存,内存管理硬件使用它来改善虚拟地址到物理地址的转换速度。当前所有的个人桌面,笔记本和服务器处理器都使用TLB来进行虚拟地址到物理地址的映射。使用TLB内核可以快速的找到虚拟地址指向物理地址,而不需要请求RAM内存获取虚拟地址到物理地址的映射关系。这与data cache和instruction caches有很大的相似之处。

来自 https://www.cnblogs.com/alantu2018/p/9000777.html

TLB原理

当cpu要访问一个虚拟地址/线性地址时,CPU会首先根据虚拟地址的高20位(20是x86特定的,不同架构有不同的值)在TLB中查找。如果是表中没有相应的表项,称为TLB miss,需要通过访问慢速RAM中的页表计算出相应的物理地址。同时,物理地址被存放在一个TLB表项中,以后对同一线性地址的访问,直接从TLB表项中获取物理地址即可,称为TLB hit。

来自 https://www.cnblogs.com/alantu2018/p/9000777.html

参考

http://www.wowotech.net/memory_management/tlb-flush.html

ROM&RAM

rom是固态储存,ram是动态储存。

ROM属于内存,也称作只读存储器,只能读出事先所存数据的固态半导版体存储器;ROM的特点是一次写入,反复读取;RAM的特点是随机存取的。

广义上内存指Cache、ROM和RAM三部分,其中Cache现在是做在CPU里面的,ROM在主板上,用来存放BIOS,装机内存指的是RAM。

两个最大的区别从字面上就能看出其rom是相当于一个永久硬盘。存东西在上面可反复使用,不易丢失!ram相当于网吧电脑上的c盘。重启等原因就会丢失数据,在手机上起到缓存的作用!

http://www.elecfans.com/d/1386845.html

SRAM和DRAM

https://zhuanlan.zhihu.com/p/52272990

https://blog.csdn.net/qq_16933601/article/details/111876189?spm=1001.2014.3001.5502

bootloader

BIOS并不直接引导操作系统。那么在硬盘的主引导区,还需要一个Bootloader。这个Bootloader可以从磁盘文件系统中把操作系统引导起来。

大多数嵌入式系统上都使用Flash存储介质。Flash有很多类型,包括NOR Flash、NAND Flash和其他半导体盘。其中,NOR Flash(也就是线性Flash)使用最为普遍。

NOR Flash可以支持随机访问,所以代码是可以直接在Flash上执行的。Bootloader一般是存储在Flash芯片上的。

Flash启动方式:

Bootloader一般放在Flash的底端或者顶端,这要根据处理器的复位向量设置。要使Bootloader的入口位于处理器上电执行第一条指令的位置。

接下来分配参数区,这里可以作为Bootloader的参数保存区域。

再下来内核映像区。Bootloader引导Linux内核,就是要从这个地方把内核映像解压到RAM中去,然后跳转到内核映像入口执行。

然后是文件系统区。

bootloader详解:https://www.cnblogs.com/anandexuechengzhangzhilu/p/10719869.html

ACPI

全称是 Advanced Configuration Power Interface高级配置和电源管理接口

CPI是为了解决APM的缺陷而问世的,APM全称是 Advanced Power Management(高级电源管理)它是一种基于BIOS 的系统电源管理方案 (是由BIOS实现)提供CPU和外设的电源管理功能;当空闲的时候会被OS调用提供CPU的电源管理。

https://zhuanlan.zhihu.com/p/283054574

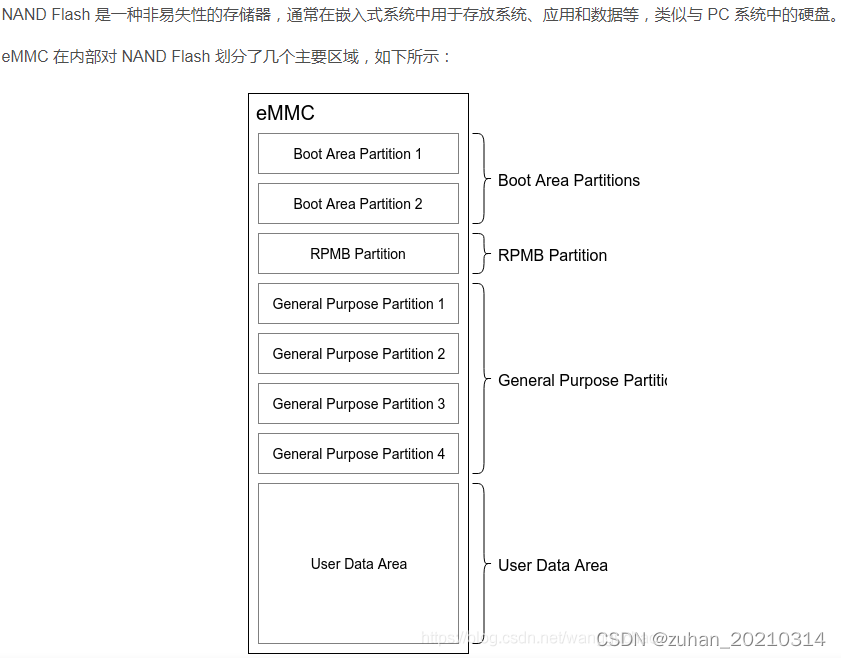

EMMC

eMMC (Embedded Multi Media Card)是MMC协会订立、主要针对手机或平板电脑等产品的内嵌式存储器标准规格。由一个嵌入式存储解决方案组成,带有MMC(多媒体卡)接口、快闪存储器设备及主控制器。所有都在一个小型的BGA 封装。接口速度高达每秒52MBytes,eMMC具有快速、可升级的性能。同时其接口电压可以是1.8V或者是3.3V。

它是在NAND闪存芯片的基础上,额外集成了控制器,并将二者“打包”封装封成一颗BGA芯片,从而减少了对PCB主板的空间占用,也是移动设备中普及度最高的存储单元。

https://blog.csdn.net/wangguchao/article/details/102859553

emmc:全称为embeded MultiMedia Card,是一种嵌入式非易失性存储器系统,由Nand flash和Nand flash控制器组成,以BGA方式封装在一款chip上。

Nand flash:一种存储数据介质;若要读取其中的数据,需要外接的主控电路。

Nor flash:也是一种存储介质;它的存储空间一般比较小,但它可以不用初始化,可以在其内部运行程序,一般在其存储一些初始化内存的固件代码;

SPI flash (Serial Peripheral interface):串行外围设备接口,SPI总线系统是一种同步串行外设接口,可以使MCU与外围设备以串行方式进行通信。spi flash是串行通信接口的NOR flash。

https://blog.csdn.net/wenxiaohua_113/article/details/108099689

PCIE BDF

和PCI总线一样,PCIe总线中的每一个功能(Function)都有一个唯一的标识符与之对应。这个标识符就是BDF(Bus,Device,Function),PCIe的配置软件(即Root的应用层,一般是PC)应当有能力识别整个PCIe总线系统的拓扑逻辑,以及其中的每一条总线(Bus),每一个设备(Device)和每一项功能(Function)。

在BDF中,Bus Number占用8位,Device Number占用5位,Function Number占用3位。显然,PCIe总线最多支持256个子总线,每个子总线最多支持32个设备,每个设备最多支持8个功能。

MII、GMII、RMII、SGMII、XGMII、XAUI、Interlaken的区分

https://blog.csdn.net/v13910/article/details/96998143

紧耦合和松耦合

https://blog.csdn.net/weixin_44723434/article/details/88851794

SR-IOV

SR-IOV是Single Root I/O Virtualization的缩写。

在虚拟机中,一切皆虚拟。比如网卡,虚拟机看来好像有一个真实网卡,但是这个网卡是宿主机虚拟出来的硬件,也就是一堆软件代码而已,没有真实硬件。,这一堆代码是需要CPU去执行的,所以,虚拟设备的性能会随着宿主机的性能而改变。SR-IOV最初应用在网卡上。简单的说,就是一个物理网卡可以虚拟出来多个轻量化的PCI-e物理设备,从而可以分配给虚拟机使用。

https://blog.csdn.net/u014174955/article/details/45599353

SR-IOV 技术是一种基于硬件的虚拟化解决方案,可提高性能和可伸缩性。SR-IOV 标准允许在虚拟机之间高效共享 PCIe(Peripheral Component Interconnect Express,快速外设组件互连)设备,并且它是在硬件中实现的,可以获得能够与本机性能媲美的 I/O 性能。SR-IOV 规范定义了新的标准,根据该标准,创建的新设备可允许将虚拟机直接连接到 I/O 设备。

PF 驱动是一个专门管理SR-IOV设备全局功能驱动,而且还要配置相关共享资源。PF 驱动 随着Hypervisor 的不同而不同,一般需要具有比普通虚拟机更高的权限才能对其进行操作。PF驱动包含了所有传统驱动的功能,使得Hypervisor能够访问设备I/O资源。也可以通过调用PF驱动执行相关操作从而影响整个设备。PF驱动必须在VF驱动之前加载,而且需要等VF驱动卸载之后才能卸载。

PF 是全功能的 PCIe 功能,可以像其他任何 PCIe 设备一样进行发现、管理和处理。PF 拥有完全配置资源,可以用于配置或控制 PCIe 设备

编写设备驱动程序

https://docs.oracle.com/cd/E37934_01/html/E36756/glggr.html

并发和并行

并发(Concurrent),在操作系统中,是指一个时间段中有几个程序都处于已启动运行到运行完毕之间,且这几个程序都是在同一个处理机上运行。

并行(Parallel),当系统有一个以上CPU时,当一个CPU执行一个进程时,另一个CPU可以执行另一个进程,两个进程互不抢占CPU资源,可以同时进行,这种方式我们称之为并行(Parallel)。

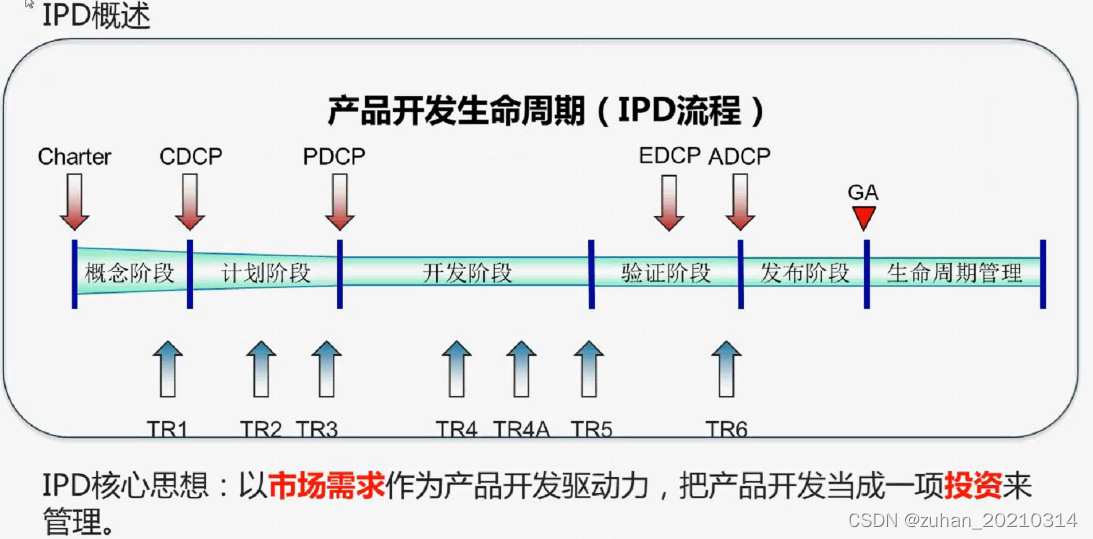

TR点

TR的意思是技术评审,是英语TechnicalReview的简写。

下面是某产品的技术评审点,

TR1——概念阶段技术评审点:产品需求和概念技术评审(业务需求评审)。

TR2——计划阶段技术评审点:需求分解和需求规格评审(功能需求评审,产品级规格)。

TR3——计划阶段技术评审点:总体方案评审(系统设计,架构设计,概要设计)。

TR4——开发阶段技术评审点:

1:模块/系统评审(详细设计,BBFV测试结果)TR4A——开发阶段技术评审点。

2:原形机的质量SDV结果和初始产品的准备情况TR5——开发阶段技术评审点。

3:初始产品的质量(SIT结果)(SITAlpha测试技术评审)。

TR6——验证阶段技术评审点:发布评审(SVTBeta测试、制造系统验证等)。

ATF

ARM Trusted Firmware

https://www.cnblogs.com/arnoldlu/p/14175126.html

https://www.shangyexin.com/2018/04/09/arm-trusted-firmware/

电磁波

https://blog.csdn.net/qq_42691315/article/details/113278342

LAN WAN WLAN的区别

WLAN 利用电磁波在空气中发送和接受数据,而无需线缆介质。

PHY——内部接口协议

来自 https://blog.csdn.net/weixin_31715171/article/details/116907190

PMA与PMA间的接口,可以是chip to chip,也可以是chip to module,有两种:

XLAUI:40 Gigabit Attachment Unit Interface,4条lane,每条lane的数率是10.3125Gbps;

CAUI:100 Gigabit Attachment Unit Interface,10条lane,每条lane的数率是10.31250Gbps;

x86、ARM和MIPS三种主流芯片架构

指令集可分为复杂指令集(CISC)和精简指令集(RISC)两部分;

复杂指令集(CISC)

x86 指令集因为硬件所提供的指令集较多,所以许多工作都能够以一个或是数个指令来代替,编译的工作因而减少了许多。是一种为了便于编程和提高记忆体访问效率的芯片设计体系,包括两大主要特点:一是使用微代码,指令集可以直接在微代码记忆体里执行,新设计的处理器,只需增加较少的电晶体就可以执行同样的指令集,也可以很快地编写新的指令集程式;二是拥有庞大的指令集,x86拥有包括双运算元格式、寄存器到寄存器、寄存器到记忆体以及记忆体到寄存器的多种指令类型,为实现复杂操作,微处理器除向程序员提供类似各种寄存器和机器指令功能外,还通过存于只读存储器(ROM)中的微程序来实现极强的功能,微处理器在分析完每一条指令之后执行一系列初级指令运算来完成所需的功能。

精简指令集(RISC)

ARM

是为了提高处理器运行速度而设计的芯片体系,它的关键技术在于流水线操作即**在一个时钟周期里完成多条指令.**相较复杂指令集CISC而言,以RISC为架构体系的ARM指令集的指令格式统一、种类少、寻址方式少,简单的指令意味着相应硬件线路可以尽量做到最佳化,从而提高执行速率。因为指令集的精简,所以许多工作必须组合简单的指令,而针对复杂组合的工作便需要由编译程序来执行。

ARM指令集架构的主要特点:一是体积小、低功耗、低成本、高性能;二是大量使用寄存器且大多数数据操作都在寄存器中完成,指令执行速度更快;三是寻址方式灵活简单,执行效率高;四是指令长度固定,可通过多流水线方式提高处理效率。

MIPS

是高效精简指令集计算机体系结构中的一种,与当前商业化最成功的ARM架构相比,MIPS的优势主要有五点:一是早于ARM支持64bit指令和操作,性能普遍高于ARM;二是MIPS有专门的除法器,可以执行除法指令;三是MIPS的内核寄存器比ARM多一倍,在同样的性能下MIPS的功耗会比ARM更低,同样功耗下性能比ARM更高;四是MIPS指令比ARM稍微多一些,执行部分运算更为灵活;五是MIPS在架构授权方面更为开放,允许授权商自行更改设计,如更多核的设计。

MIPS架构也存在一些不足之处:一是MIPS的内存地址起始有问题,这导致了MIPS在内存和cache的支持方面都有限制,即MIPS单内核无法面对高容量内存配置;二是MIPS技术演进方向是并行线程,类似INTEL的超线程,而ARM未来的发展方向是物理多核,从目前核心移动设备的发展趋势来看物理多核占据了上风;三是MIPS虽然结构更加简单,但是到现在还是顺序单/双发射,ARM则已经进化到了乱序双/三发射,执行指令流水线周期远不如ARM高效;四是MIPS学院派发展风格导致其商业进程远远滞后于ARM,当ARM与高通、苹果、NVIDIA等芯片设计公司合作大举进攻移动终端的时候,MIPS还停留在高清盒子、打印机等小众市场产品中;五是MIPS自身系统的软件平台也较为落后,应用软件与ARM体系相比要少很多。

MIPS:优雅的学术设计成果,RISC 类;

X86 : 不够优雅,但是市场成功,属 CISC 类,但是也融合了 RISC 的特点。在 PC 方面是无疑的王者,目前正想在移动领域跟 ARM 争个你死我活;

ARM:也是 RISC 型,相当于移动领域的 x86,几乎所有的移动设备芯片都是基于 ARM 架构。全世界超过95%的智能手机和平板电脑都采用ARM架构。

举个例子,如果处理器相当于一栋完整的建筑, ARM就像是建筑的框架,至于最后建造出来的房子长什么样,舒适度如何,就是由处理器厂商自己决定了。但是采用相同架构的处理器,性能基本上已经锁定在一定的范围之内,不会有本质的区别。所以,看处理器的性能要先看架构。ARM公司提供两类CPU授权:核心指令集授权,以及现成的CPU内核设计方案授权。业内多数手机处理器厂商选择直接购买ARM CPU设计方案,然后与其它组件(比如GPU、多媒体处理、调制解调器等等)整合,制造出完整的SoC片上系统。

HIGIG2

http://www.360doc.com/content/14/1009/09/13640092_415446680.shtml

NEON

NEON是一种基于SIMD思想的ARM技术。 SIMD, Single Instruction Multiple Data,是一种单条指令处理多个数据的并行处理技术,相比于一条指令处理一个数据,运算速度将会大大提高。

https://blog.csdn.net/yhb1047818384/article/details/51842607?spm=1001.2014.3001.5502

ACL

访问控制列表(Access Control Lists,ACL)是一种基于包过滤的访问控制技术,它可以根据设定的条件对接口上的数据包进行过滤,允许其通过或丢弃。访问控制列表被广泛地应用于路由器和三层交换机,借助于访问控制列表,可以有效地控制用户对网络的访问,从而最大程度地保障网络安全。

Apache

源于NCSAhttpd服务器,经过多次修改,成为世界上最流行的Web服务器软件之一。

PHY和MAC

以太网媒体接入控制器(MAC)和物理接口收发器(PHY)

PHY 将并行数据转化为串行流数据,按照物理层编码规则编码,再变为模拟信号把数据转发出去,收数据是流程反之;

并实现CSMA/CD的部分功能

MAC 控制是否可以发送数据并添加控制信息,并支持校验传输的数据

物理层的芯片称之为PHY,以太网卡中数据链路层的芯片称之为MAC控制器.

MAC从PCI总线收到IP数据包(或者其他网络层协议的数据包)后,将之拆分并重新打包成最大1518Byte,最小64Byte的帧。这个帧里面包括了目标MAC地址、自己的源MAC地址和数据包里面的协议类型(比如IP数据包的类型用80表示)。最后还有一个DWORD(4Byte)的CRC码。

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC),每4bit就增加1bit的检错码,然后把并行数据转化为串行流数据,再按照物理层的编码规则(10Based-T的NRZ编码或100based-T的曼彻斯特编码)把数据编码,再变为模拟信号把数据送出去。

MAC是Media Access Control的缩写,即媒体访问控制子层协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。以太网MAC由IEEE-802.3以太网标准定义

问:以太网PHY是什么?

答:PHY是物理接口收发器,它实现物理层.IEEE-802.3标准定义了以太网PHY.包括MII/GMII(介质独立接口)子层,PCS(物理编码子层),PMA(物理介质附加)子层,PMD(物理介质相关)子层,MDI子层.它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范.

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC.对于100BaseTX因为使用4B/5B编码,每4bit就增加1bit的检错码),然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去.收数据时的流程反之.PHY还有个重要的功能就是实现CSMA/CD的部分功能.它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去.如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据.这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突.

问:网卡的MAC和PHY间的关系?

答:网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口.物理层的芯片称之为PHY.数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能.以太网卡中数据链路层的芯片称之为MAC控制器.很多网卡的这两个部分是做到一起的.他们之间的关系是pci总线接mac总线,mac接phy,phy接网线(当然也不是直接接上的,还有一个变压装置).

PHY和MAC之间是如何传送数据和相互沟通的.通过IEEE定义的标准的MII/GigaMII(Media Independed Interfade,介质独立界面)界面连接MAC和PHY.这个界面是IEEE定义的.MII界面传递了网络的所有数据和数据的控制.ETHERNET的接口实质是MAC通过MII总线控制PHY的过程.

来自 https://www.cnblogs.com/jason-lu/articles/3195473.html

https://m.elecfans.com/article/109113.html

时钟信号

时钟信号是时序逻辑的基础,用于决定逻辑单元中的状态何时更新,是有固定周期并与运行无关的信号量。时钟信号有固定的时钟频率,时钟频率是时钟周期的倒数。

作用:时钟信号通常被用于同步电路当中,扮演计时器的角色,保证相关的电子组件得以同步运作;可以使用时钟来同步 CPU 的不同进程,通过上升沿或下降沿来改变周期输出。

通俗来讲,我们知道电信号以低电压和高电压来区分1和0,假如我们要传输一段01010101的电信号,只要根据变化就能区分出来得到正确的解析,但是如果我们需要传输一段0000的电信号,你就会发现一个问题,那就是我到底传输了几个0?因为电信号一直没有变化,无法区分,所以时钟信号的作用就在这里,根据时间间隔来分割每一段电信号

PRBS

Pseudo-Random Binary Sequence,中文翻译叫做伪随机二进制序列,江湖人简称它为伪随机码。做过测试的朋友们都应该特别熟悉,就是使用PRBS这种伪随机码进行高速串行通道的测试,主要是测试误码率的情况,例如我们常用的一些协议,PCIE,USB,以太网或者光模块的测试等等。

为什么业界公认选择这种prbs码型进行测试(仿真)呢?主要原因是这种码型与真实链路的数据传输情况非常接近。因为在真实情况中,所以的数据组合都是随机出现的,没有任何规律可言。 而PRBS 的码流在很大程度上具有这种“随机数据”的特性,“0”和“1”随机出现,这种码流的频谱特征和白噪声非常接近,所谓“白噪声”就是在一个比较宽的频域里功率密度谱均匀分布,也就是所有的频率都具有相同的能量,因此该码型能够模拟各种不同频率数据组成的情况,使测试更符合真实的情况。

原文链接:https://blog.csdn.net/xiaohaolaoda/article/details/106253629

加密卡

一些安全信息,相关法律明确禁止使用明文进行传输和存储。早期通过软件实现加密,但随着性能要求的不断提高,需要加密硬件实现以提高吞吐量。加密卡通过使用SM1、SM2、SM3、SM4等加密硬件来实现的,所有与加密解密和验证算法相关的内容直接传递到加密卡上。

TPM

是指符合TPM(可信赖平台模块)标准的安全芯片。能有效地保护PC、防止非法用户访问。符合TPM的芯片首先必须具有产生加解密密匙的功能,此外还必须能够进行高速的资料加密和解密,以及充当保护BIOS和操作系统不被修改的辅助处理器。

TPM芯片用途

1、存储、管理BIOS开机密码以及硬盘密码

以往这些事务都是由BIOS实现,忘记了密码只要取下CMOS电池,给CMOS放电就清除密码了。如今这些密钥实际上是存储于固化在芯片的存储单元中,即便是掉电其信息亦不会丢失。相比于BIOS管理密码,TPM安全芯片的安全性要大为提高。

2、TPM安全芯片可以进行范围较广的加密

TPM安全芯片除了能进行传统的开机加密以及对硬盘进行加密外,还能对系统登录、应用软件登录进行加密。比如MSN、QQ、网游以及网上银行的登录信息和密码,都可以通过TPM加密后再进行传输,这样就不用担心信息和密码被人窃取。

3、加密硬盘的任意分区

可以加密任意一个硬盘分区,将一些敏感的文件放入该分区以策安全。其实有些笔记本厂商采用的一键恢复功能,就是该用途的集中体现之一。还有一些大型商业软件公司(如Microsoft)也会利用其作为加密分区的手段。

SERDES

是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。这是一种通信技术的统称。

SGMII

–Serial Gigabit Media IndependentInterface SGMII是PHY与MAC之间的接口,类似与GMII和RGMII,只不过GMII和RGMII都是并行的,而且需要随路时钟,PCB布线相对麻烦,而且不适应背板应用。而SGMII是串行的,不需要提供另外的时钟,MAC和PHY都需要CDR去恢复时钟。另外SGMII是有8B/10b编码的,速率是1.25。所以,SGMII需要PHY来做8b/10b的解码工作。SGMII在物理上是兼容SERDES信号的,所以走的通道也是SERDESlane。

在intel的LAN芯片中,一般情况都是MAC和PHY在一起的。所以通过eeprom可以配置LAN芯片输出信号的种类。可以接电口RJ45和光口SFP。

如果我们需要直接从LAN芯片中接SFP接口,则需要配置成SerDes(1000Base-BX)mode;

如果接RJ45,则需要在flash中配置成copper PHY。

如果需要接另外一颗PHY,则需要在flash中配置成SGMII Mode,送如PHY中。

参考链接:https://www.pianshen.com/article/98551788018/

调制解调器

是调制器和解调器的缩写 ,一种计算机硬件,它能把计算机的数字信号翻译成可沿普通电话线传送的模拟信号,而这些模拟信号又可被线路另一端的另一个调制解调器接收,并译成计算机可懂的语言。这一简单过程完成了两台计算机间的通信。

调制解调器是Modulator(调制器)与Demodulator(解调器)的简称,中文称为调制解调器,根据Modem的谐音,亲昵地称之为“猫”,是一种能够实现通信所需的调制和解调功能的电子设备。一般由调制器和解调器组成。在发送端,将计算机串行口产生的数字信号调制成可以通过电话线传输的模拟信号;在接收端,调制解调器把输入计算机的模拟信号转换成相应的数字信号,送入计算机接口。在个人计算机中,调制解调器常被用来与别的计算机交换数据和程序,以及访问联机信息服务程序等。所谓调制,就是把数字信号转换成电话线上传输的模拟信号;解调,即把模拟信号转换成数字信号。合称调制解调器。

PCH

pch全称为Platform Controller Hub,是intel公司的集成南桥。

PCH是Paging Indicator CHannel的缩写,译为寻呼信道。是北桥中的内存控制器和PCIe控制器都集成到了CPU内部,相当于整个北桥芯片都集成到了CPU内部,主板上只剩下南桥.所以PCH可以理解成南桥.目前Intel的有些SOC就是连PCH也集成到了CPU内部,比如:Intel Xeon D系列.

SNMP

简单网络管理协议(Simple NetWork Management Protocol) 是专门设计用于在 IP 网络管理网络节点(服务器、工作站、路由器、交换机及HUBS等)的一种标准协议,它是一种应用层协议。管理MIB(Management Information Base,管理信息库)

328

328

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?