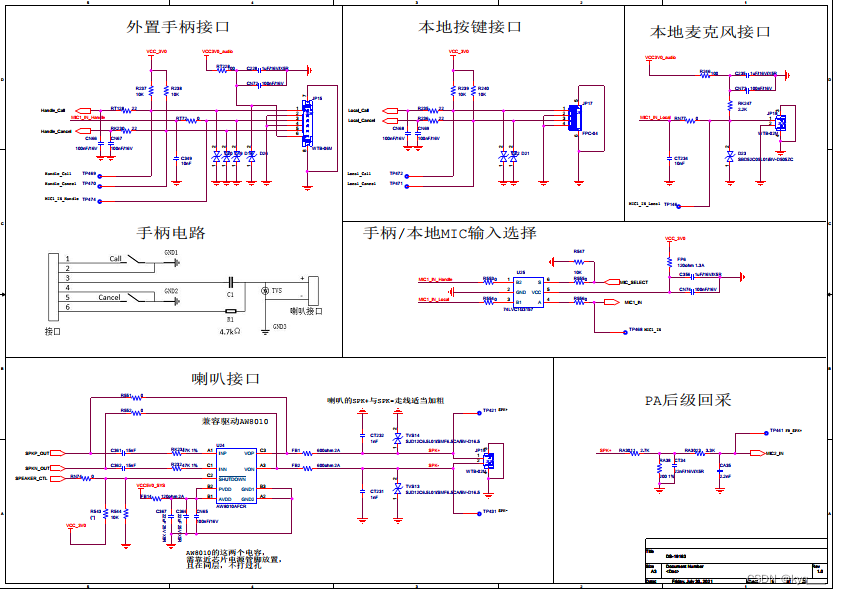

使用单刀双掷模拟开关时遇到问题:

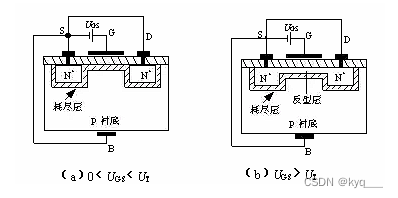

如图1,在Select脚为低时正常导通B1-A,但是在B2接入手柄(handle)输入音频时(此时MIC_local断开),A通道中也可采集到handle音频数据,测量B2点存在3.3V电压,与B1点电压几乎相同,将模拟开关芯片取下,测量PCB焊盘U25-(1、3),(1、6),(1、5)正常(不导通),测量芯片同样不导通,将芯片焊接回PCB,断开MIC_local与芯片0Ω串阻,电压消失,B2上存在的电压由B1引起。

图1 问题原理图

即使用模拟开关选通为低,选通B1时,B2音频信号也会同时串入。测量电平发现B1通道高电平大于芯片VDD电平。

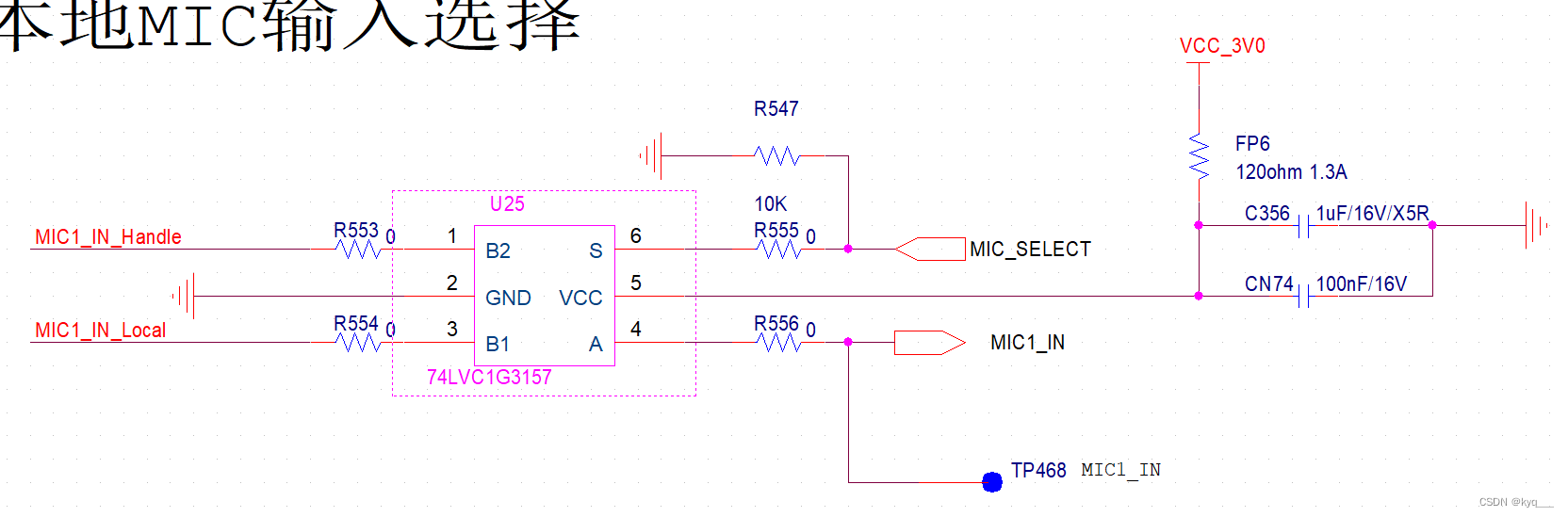

图2 模拟连接示意图

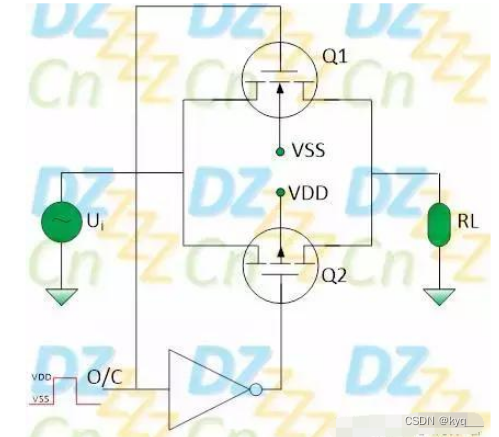

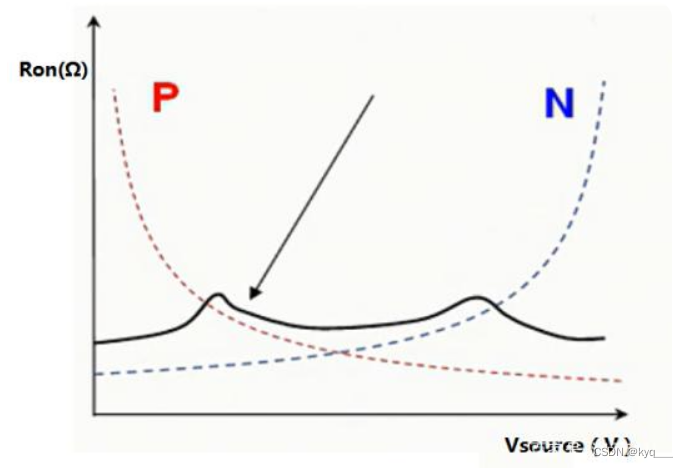

模拟开关芯片内部结构应为一对P、NMOS形成的传输栅,如下图:

图3 传输栅结构示意图

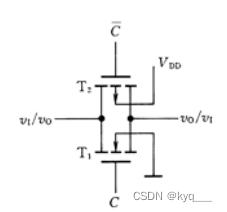

图4 模拟开关内部示意图

按照MOS原理:

在UGS﹥UT的条件下,如果在漏极D和源极S之间加上正电压UDS,导电沟道就会有电流流通。漏极电流由漏区流向源区,因为沟道有一定的电阻,所以沿着沟道产生电压降,使沟道各点的电位沿沟道由漏区到源区逐渐减小,靠近漏区一端的电压UGD最小,其值为UGD=UGS-UDS,相应的沟道最薄;靠近源区一端的电压最大,等于UGS,相应的沟道最厚。这样就使得沟道厚度不再是均匀的,整个沟道呈倾斜状。随着UDS的增大,靠近漏区一端的沟道越来越薄。

图5 增强型NMOS示意图

当MOS衬底B和S分开,单独接电源和GND,就形成了上图中模拟开关的内部结构,使用一对P、NMOS是因为由于PMOS和NMOS的不同特性,导致他们组成的开关具有如下图所示的特性。NMOS管在信号比较低时的导通电阻较小,而PMOS管则在输入信号较高时的导通电阻较小,两个电阻并联后,则在整个信号的有效范围内都比较低。

图6 传输栅结构RDS(on)示意图

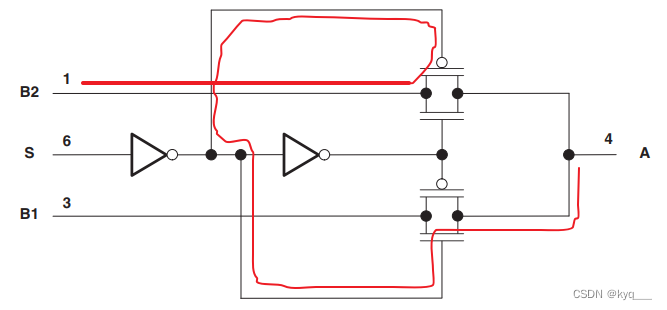

图7 输入通道通过衬源导通通道

总结

当输入端B1的信号MIC_local(不接MIC、接了MIC会与MIC内阻形成分压)电压值大于VDD(芯片的VCC端电压),会导致衬底和源极导通,继而导致有电流从衬底的低掺杂的P型硅片流向源极的高掺杂N+区,如图7,所以在使用该结构的模拟开关时需要保证衬—源之间电压UBS使衬—源之间PN结反向偏置,这样也不会有电流从衬底经过PN结流向源极。正常使用MOS时将衬底和源极短接也是这个原因。

后续如果模拟开关VDD电源和信号电源不是相同电源域,需要VDD大于信号电源域,本例中建议MIC上拉LDO电源使用3.0V

4472

4472

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?