一、为什么要上拉or下拉?

在数字逻辑电路中,一个信号不是0,就是1。正是因为这样,数字电路的设计才简单,可靠。

通常,用电压5v(或者接近5V)代表 on 开状态,代表高电平,对应状态 1。用电压0v (或者接近0v)代表off关状态,代表低电平,对应状态0。

有些开发板是基于3,3V的,因此使用3.3V作为高电平。

那么试想如果一个线路中的电压处于不确定的状态(例如一个引脚不和任何其它回路连通时),那我们就说它的电压是浮动的,他会随着时间不断变化、跳动,而且很容易受到外界环境的影响。处于这种不确定状态的电路会被随机解释为高或者低电平。 这种现象也叫电子噪声。

然而程序必须是严格准确的,所以电路的设计一定要避免线路电压处于浮动状态。

我们可以使用上拉电阻或者下拉电阻将电路的电压在任何时候都保持在确定的状态下,这就是上拉电阻和下拉电阻的作用。

上拉电阻

作用:将一个未知的电平拉高到稳定的高电平状态。

当S2没按下时(不确定时),Input通过2个电阻和+5V连接(注意电路中并没构成回路,因此不会有压降,所以Input端依然是高电平),为高电平。当S2按下时,+5V,R2,S2,GND形成回路,R2 电阻大,产生压降大,因此后面的Input就是低电平。

因此,可以通过Input端的电平来判断S2是否按下。

相比下拉电阻,上拉电阻在数字电路中使用的更多。

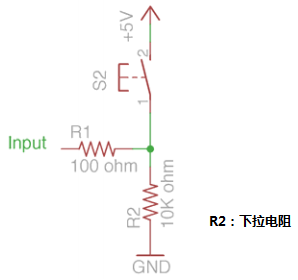

下拉电阻

作用:将一个未知的电平拉低到稳定的低电平状态。

上图中,我们要判定input这个引脚,是高电平还是低电平。

当按钮S2没按下时(不确定时),Input通过2个电阻接到GND,是稳定的低电平 。 当S2按下时,+5V ,S2 , R2 ,GND这条路导通,而Input接在R2的前面,因此会得到高电平。

因此,我们可以通过Input端是高电平还是低电平来判断S2是否按下。

如果没有下拉电阻R2,那么S2没按下前,Input没有和任何东西相连,它的电平处于浮动状态,且很容易受环境影响,带来电子噪声。

- 上拉是将不确定信号通过一个电阻钳位在高电平,电阻同时限流作用;

- 下拉是将不确定信号通过一个电阻钳位在低电平。

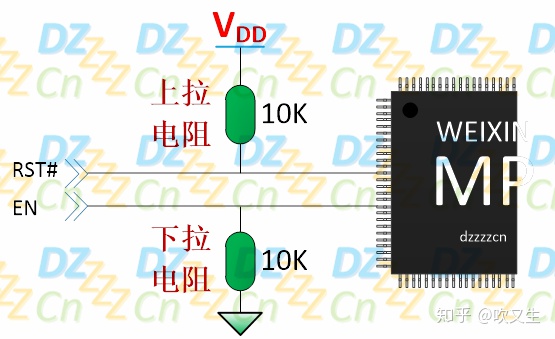

二、应用

- 对于高有效的使能控制信号(EN),如果希望电路系统在上电后应处于无效状态,则会使用下拉电阻(不确定工作状态时给低电平);假设这个使能信号是用来控制电机的,如果悬空的话,此信号线可能在上电后(或者运行中)受到其他噪声干扰而误触发为高电平,从而导致电机出现不期望的转动,这肯定是所不希望的,此时可以增加一个下拉电阻

- 相应地,对于低有效的复位控制信号(RST#),希望上电后复位后处于无效状态,则应使用上拉电阻(不确定工作状态时给高电平)。

拉电阻作为输出时牵涉到的知识点会更多一些,但本质的功能也是将电平箝位,最常见的输出上拉电阻出现在开集(Open Collector,OC)或开漏(Open Drain,OD)结构的引脚。

我们有很多芯片的输出引脚是推挽输出结构(Output Push-Pull),如下图所示(还有一种反相输出的结构,本质也是一样的):

推挽输出结构引脚的特点是:无论引脚输出高电平“H”还是低电平“L”,都有比较强的驱动能力(输入或输出电流能力)!

当推挽输出结构的控制信号为低电平“L”时,Q1截止Q2导通,电流I1由电源VCC经负载RL与三极管Q2流向公共地,我们称此电流为灌电流(Sink Current),也就是外部电流灌入芯片内部,如下图所示:

相应的,当推挽输出结构的控制信号为高电平“H”时,Q1导通Q2截止,电流I1由电源VCC经三极管Q1与负载RL流向公共地,我们称此电流为拉电流(Source Current),也就是芯片内部可以向外提供的电流(所以称之为“源电源”),从另一个角度讲,也就是外电路可以从芯片中拉走多少电流,如下图所示:

8042

8042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?