**

MIPI简介

**

MIPI (Mobile Industry Processor Interface) 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如:

摄像头接口CSI

显示接口DSI

射频接口DigRF

麦克风 /喇叭接口SLIMbus

等等

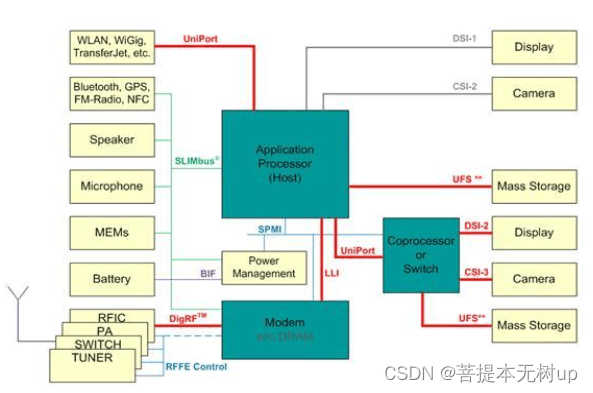

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。下图是按照 MIPI的规划下一代智能手机的内部架构。

MIPI联盟的MIPI DSI规范

MIPI名词解释

DCS(Display Command Set)

DSC是用于命令模式显示模块的标准化命令集

DBI、DPI(Display Bus Interface,Display Pixel Interface)

DBI:具有显示控制器和帧缓冲区的显示模块并行接口

DPI:无显示控制器和帧缓冲区的显示模块并行接口

DSI、CSI(Display Serial Interface,Camera Serial Interface)

DSI:定义了一个位于CPU和显示模组之间的高速串行接口

CSI:定义了一个位于CPU和摄像模组之间的高速串行接口

D-PHY

提供DSI和CSI的物理层定义

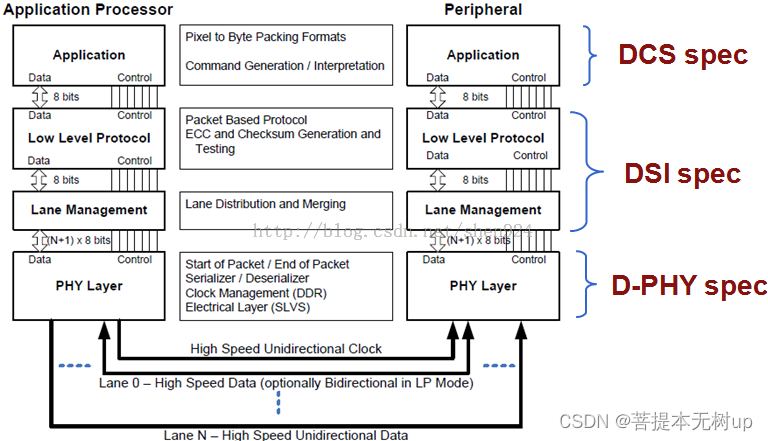

MIPI DSI分层结构

• PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

• Lane Management层:发送和收集数据流到每条lane。

• Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

• Application层:描述高层编码和解析数据流。

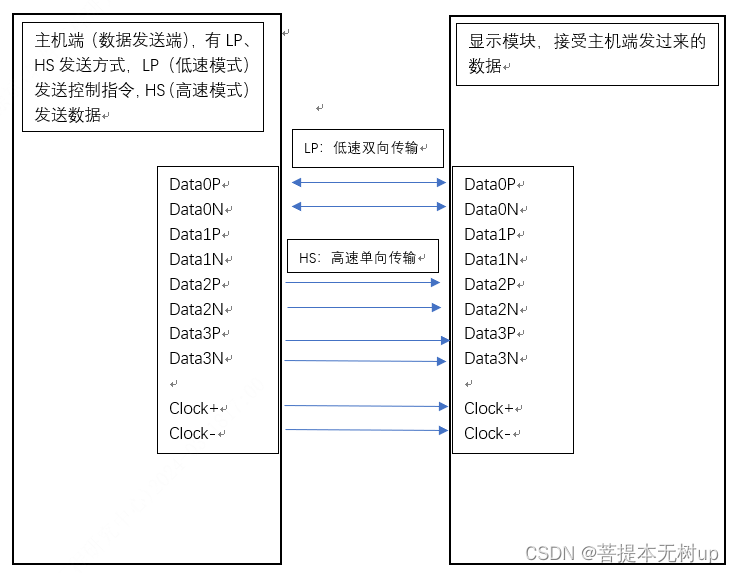

DSI的接口图,有一对Clock+ Clock- 时钟连接线和4组差分数据线。在LP(低速模式)下传输控制指令,在HS(高速模式)下传输数据。

液晶基础时钟概念

1、通用时钟概念

PORCH:液晶时序当中,常常用到的一些参数HSYNC、HBP、HACTIVE、HFP,VSYNC、VBP、VAVTIVE、VFP,概念如下:

HFP: Horizon front porch

HBP: Horizon back porch

VFP: Vertical front porch

VBP: Vertical back porch

HACTIVE: Horizon display period

VAVTIVE: Vertical display period

H-total = HSYNC+HBP+HACTIVE+HFP

V-total = VSYNC+VBP+VACTIVE+VFP

上述porch概念的具体含义,这里就不展开描述了。网上有很多资料,后续如果有更新液晶接口系列——RGB接口的话也许会重点讲解下这部分。简单说H-total 和V-total分别表示,为了传送一帧图像,每一行数据需要实际传送的像素数(H-total )和总共需要传输几行(V-total),而这两个值不等于分辨率原因在于图像传输有一些时序要求,方便数据的同步等,所以每一行都会用一些无用(非图像数据)的像素(pixel)传输。

2、DSI时钟概念

Total pixel = H-total x V-total x fps(一般是60)

fps是帧率,表示1s内传输的图像帧数,H-total x V-total表示一帧图像要传输的总pixel数,所以Total pixel 表示1s内要传输的pixel总数。说白了就是1s要传输多少个点。

Bitclk= Total pixel x 位深/lane number

位深:简单说是表示一个像素点需要多少bit来表示,比如如果rgb888格式的图像的,那就是3*8=24bit,如果是rgb565格式的图像,那位深就是5+6+5 = 16bit。以rgb888位例子,每个pixie要用24bit来表示,那么Total pixie x 24 表示的是1s内要传输多少个bit,所以Bitclk就表示1s内一条数据lane线上传输的bit总数。

Byteclk = bitclk/8

显然1Byte = 8bit,所以Byteclk =bitclk/8,表示1s内一条数据lane线上传输的Byte数。

pclk(Dsi pixel clock) = (Byteclk * lane number)/bpp(byte) = Total pixel

bpp简单说就是表示一个像素点需要用几个Byte表示,所以pclk就是表示1s内所有的lane传输的总Byte数/每个像素占用的字节数 = 所有的lane传输的总pixel数,与Total pixel 值相等。

UI = 1/Bitclk

UI是MIPI时序中很多时间要求的基本单位,我们可以从液晶IC的时序要求手册上看到它的身影,很多时序的上升沿、时序间隔等以UI为单位,用xx UI来表示时序要求。

注:

①、实际测的MIPI时钟:= Bitclk /2 (因为是双边沿采样,一个时钟可以穿两个bit的数据)

②、有些平台,Bitclk的计算方式不同,上述公式是理论上的,以高通平台为例的,但是有些平台(比如展锐)公式如下,且建议用该公式进行计算:Bitclk = Total pixel x 位深 x 1.2 / lane number 加主要是为了提高时钟,因为MIPI传输协议中,实际传输数据还会包括包头、包尾等更多的非图像数据,而没有乘以1.2计算出来的时钟是刚好够传输图像的时钟,如果不乘以1.2,那么时钟就会过小,因为被协议数据占据了一部分时钟,这样会导致时钟过低,从而液晶无法正常显示。1.2这个值是个经验值,而RK平台通常是在理论计算出后直接加上100Mhz,而不是乘以1.2.

所以mipi接口时钟(就是你用示波器去测量Clock lane的波形频率,是最终体现在接口上的实实在在的能测量到的时钟)公式如下

dsi clk = Bitclk / 2 = H-total x V-total x fps x 位深 / lane number / 2

上面公式中为什么要除以2,因为我们上一篇中讲过,MIPI采用双边沿采样传输,即一个时钟的上升沿和下降沿都可以传输数据,所以一个时钟可以传输2个bit,所以需要的实际时钟就可以只要是bitclk的一半就可以了。(如DSI时钟概念下的 “注B” 所分析,有的平台最终结果还要乘以1.2或者加上100M等)

来来来,我们for example下,比如我们要调试的液晶,porch参数如下:

HFP=48, HBP=48, HSYNC=32, VFP=8,VBP=8, VSYNC=4,HACTIVE=1920,VAVTIVE=1080,传输的图像格式是rgb888,fps=60,使用4个lane来传输。

那么

dsi clock = H-total * V-total * fps*位深 / lane numberl / 2

=(HSYNC+HBP+HACTIVE+HFP)*(VSYNC+VBP+VACTIVE+VFP) * 60 * 24 / 4 / 2

= 405504000 Hz =405.50 Mhz

液晶屏的模式

COMMAND模式和VIDEO模式

这个是针对屏幕来说的,简单理解,如果是通过将数据写到液晶IC中的GRAM的,即为COMMAND模式的屏幕(通过每次写显示数据时需要先发送命令给屏幕:我要开始写屏幕了,要写的位置坐标是(x,y))。而video模式的屏幕除了一开始给液晶IC的初始化命令(写IC的各种寄存器去开启液晶的各种配置,command屏也会有),后面屏幕的显示是一直不中断的给他发送显示数据的。

VIDEO屏的三种模式

Non-burst Mode Sync pulses

Non-burst Mode Sync event

Burst mode

这三种模式的区别主要是在于传输图像过程中,不同模式会发送不同的数据包,最常用的是burst mode。具体差别可以看DSI协议讲解中的参考链接,或者从液晶的IC手册中去看,一般都会有。

3166

3166

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?