Read me:

最近在搞FPGA,关于复位这里,一会儿是高电平复位,一会又是低电平复位。

复位到底什么时候是高电平,什么是低电平,傻傻分不清。

尤其是用到锁相环那里,看了一些网上的资料,说是PLL锁相环IP是的复位是高电平复位。这又是因为什么。

我觉得还是好好理解下为什么,不能不懂装懂,刚开始学的时候,就是要把基础概念与基础道理搞明白,这样才能保证之后在做工程上不糊涂。

本文目录:

1.什么是“复位”,为什么需要复位?”

2.低电平复位

3.高电平复位

4.关于 锁相环PLL IP 核中“复位”的说明

5.总结

正文:

1.什么是“复位”,为什么需要复位?

复位,从字面上理解,就是恢复到之前的位置。

之前的位置,我们书面上就叫做“初始状态”。

1.1为什么需要复位?

不管是单片机、CPU、DSP等处理器都有复位rst,就是防止程序跑飞,跑飞不受控,野蛮生长怎么办,所以得留一手,通过一个按键或者什么

机制,将一切恢复到一个“初始状态”,打回原形,恢复到原来的位置。

在产品中,也有这个概念,一般家里买的路由器,手机等,都有一个小孔,使用针戳进去,就实现了恢复出厂设置。这也是利用了“防止不受控,得留一手可以恢复原始状态的手段”思想。

复位有软复位,上电复位,硬件复位。

1.2 我们这里主要讲 硬件复位。

硬件复位,就是通过一个复位按键实现复位功能。

通过按一下这个按键,实现复位。

这种按键,按一下会闭合,松手后会自动弹回来。

正常情况下,我们是不想让芯片进行复位的,不复位是常态。

2.低电平复位

就是使用低电平时候进行复位。

更通俗的说,就是当这个管脚(复位管脚)为低电平时候,生效,使能。

2.1 那么,硬件上怎么设计呢?

记住我上面那句话,不复位是常态。

既然是低电平复位,那么就是高电平时常态了,即就是:在不按复位按键时,这个管脚应该长期处于高电平。

硬件中,对这个管脚上拉就可以。如下图:

2.2 那么,逻辑代码中怎么表示呢?

复位的英文是resert;

英文的negative,表示:消极、阴性、否的意思。这里就表示低电平。

简化一下,一般用rst_n,表示是“低电平类型”的复位。

rst_n 表示低电平复位。

3.高电平复位

同理,高电平复位,就是常态应该是低电平。

3.1 那么硬件管脚需要被下拉到地。

如下图:

2.2 那么,逻辑代码中怎么表示呢?

复位的英文是resert;

简化一下,一般用rst,表示是“高电平类型”的复位,因为低电平复位已经加“-n”区别了,所以这里可以不用再加尾缀加以区分。

rst 表示高电平复位。

按这种命名清晰,使得代码的可读性很强。

4.关于 锁相环PLL IP 核中“复位”的说明

在做FPGA逻辑设计时,PLL IP核最常用,网上很多教程上来,直接就说PLL IP 核的复位时高电平,要注意。

那么为什么?这个说法是否完全正确呢?

我们从调用IP核的步骤中,一看究竟吧。

这个复位是可以设置的,不是一定就得是高电平。

比如:

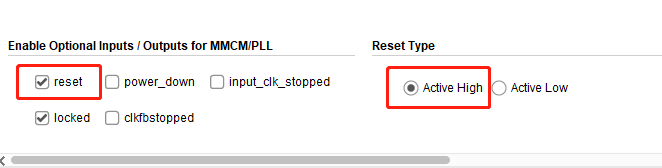

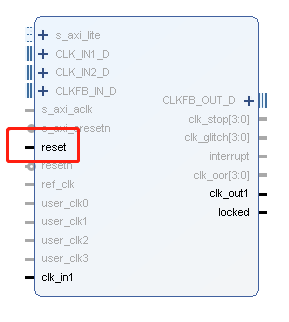

这里我们可以设置为:高电平复位。

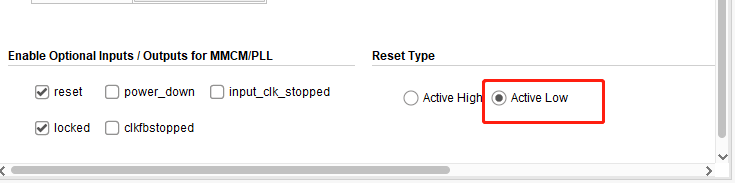

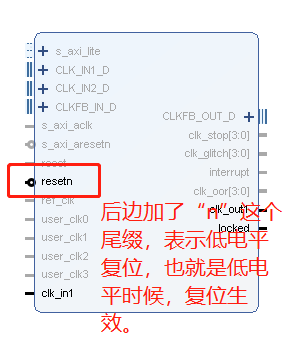

我们还可以设置为:低电平复位。

5.总结

将复位这里,从概念到具体,整理了一下自己的理解与思路。

又把PLL IP 复位这里,仔细研究了下。

心里总算是舒服了,踏实了,每一步走好,避免以后工程设计中“基础不牢,地动山摇”。

keep doing~~~

THE END~

8038

8038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?