在为ASIC选择复位策略前必须考虑许多方面的问题。对于复位,我们都只到有同步复位和异步复位,那么在实际设计的时候,就需要知道该选择哪种复位方式,还有所有的触发器是否都需要接收复位信号。

复位最基本的目的是使SoC进入一个能进行稳定操作的确定状态,这样可以避免SoC在上电后进入随机状态而死机。在verilog中,有四种逻辑状态:0,1,x,z。但是在进行IC设计的时候,会有十几种逻辑状态。所以添加复位信号十分有必要。一旦SoC生产出来,是否需要对SoC使用复位就由系统、SoC的使用环境以及SoC的自身的设计方式来决定。好的设计指南会在系统没有明确要求的情况下为SoC中的每一个触发器都提供复位信号。在某些情况下,当流水线的寄存器在高速应用中使用时,应该去掉某些寄存器的复位信号以使设计达到更高性能。

设计可以选择异步复位或同步复位,或者同时使用两者。两种复位方式各都有各自的优点和缺点。在实际设计中没有完全确定的复位方法,我们必须根据实际设计,选择最合适的复位方法。

同步复位与异步复位

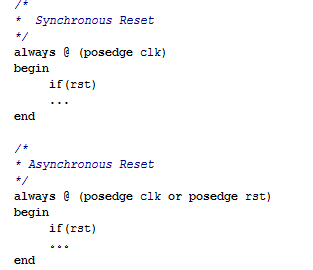

图1用verilog描述了什么是同步复位以及异步复位

图 1 同步复位和异步复位

1 用同步复位进行设计

同步复位的复位信号只有在时钟的有效沿到来时才能对寄存器进行复位。由于复位树具有高扇出,复位相对于时钟周期可能是一个“迟到的信号”。即使复位信号经过了复位缓冲树的缓冲,也要尽可能减少其到达本地逻辑前穿过的逻辑数量。

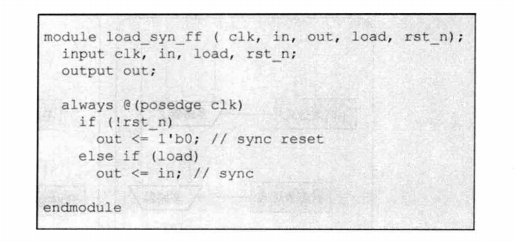

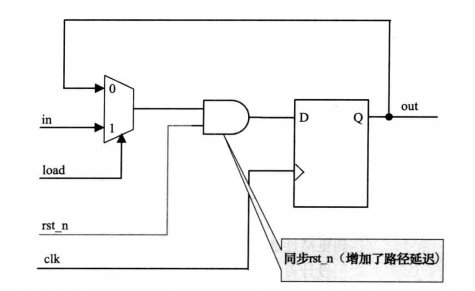

图2表示了带有同步复位的可加载触发器的RTL代码,图3位对应的硬件实现。

图 2 同步复位可加载触发器的RTL代码

图 3 带同步复位的可加载触发器

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2190

2190

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?